Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf

|

71 |

К настоящему времени разработано |

много способов схемной реализации |

базовых логических элементов: |

|

-резисторно-транзисторная логика РТЛ, отличается невысоким быстродействием, требует большой площади на подложке и в настоящее время применяется очень редко;

-диодно-транзисторная логика ДТЛ, имеет среднее быстродействие, ранее выпускался широкий набор микросхем низкой степени интеграции с использованием этих элементов. Для них t здср составляло 20…100 нс. В настоящее время применение

ограничено вследствие появления устройств с более высоким быстродействием и низкой потребляемой мощностью;

-транзисторно-транзисторная логика ТТЛ является дальнейшим развитием ДТЛ, имеет среднее быстродействие и более низкую потребляемую мощность, посравнению с ДТЛ. ТТЛ более технологична при изготовлении микросхем с большой степенью интеграции изготовлении. Относится к наиболее разработанным типам. Включает в свой состав большое количество типов элементов;

-транзисторно-транзисторная логика с диодами Шотки (ТТЛШ) разработана на основе ТТЛ с целью дальнейшего повышения быстродействия и снижения потребляемой мощности;

-эмиттерно-связанная логика имеет высокое быстродействие при высокой потребляемой мощности. Используется в основном в синтезаторах частоты при построении делителей частоты;

-логические элементы на МДП (металл-диэлектрик-полупроводник) транзисторах характеризуются невысоким быстродействием и высокой технологичностью изготовления. Для повышения быстродействия были разработаны логические устройства на МДП транзисторах с разной проводимостью КМОП (комплементарные металл – оксид - полупроводник) логика. Этот вид устройств на сегодняшний день является самым технологичным и наиболее распространен в цифровой технике при построении СБИС;

-интегрально-инжекционная логика И2 Л имеет высокое быстродействие и весьма высокую технологичность изготовления, но невысокую помехоустойчивость. Применяется исключительно в составе БИС и СБИС.

|

72 |

Рассмотрим реализацию базового |

логического элемента И-НЕ на |

микросхемах разных типов. |

|

3.3.1. Интегральные схемы ТТЛ и ТТЛШ

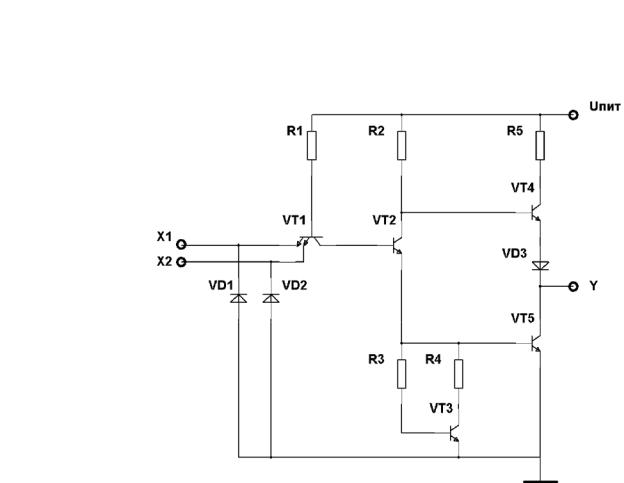

Схема, реализующая базовый элемент И-НЕ ТТЛ, представлена на рис. 9.

При подаче хотя бы на один из входов логического «0», транзистор VT1 переходит в состояние насыщения, при этом транзистор фазорасщепителя VT2 запирается, запирается также транзистор VT5, а ток текущий в базу транзистора VT4 через резистор R2 отпирает его и на выходе Y устанавливается высокий уровень логической «1». При наличии на обеих входах X1, X2, логической «1», ток через эмиттерные переходы VT1 не течет, при этом коллекторный переход VT1 оказывается смещенным в прямом направлении и протекающий через него и R1 ток приводит в состояние насыщения транзистор VT2. Ток, протекающий через резистор R2 и транзистор VT2, приводит к насыщению транзистора VT5. При этом напряжение на базе транзистора VT5 оказывается недостаточным для его открывания, и он запирается.

Рис.9 Схема электрическая принципиальная элемента 2И-НЕ ТТЛ.

|

73 |

Таким образом, на выходе Y |

устанавливается низкий уровень. Такой |

сложный выходной каскад (VT4, VT5) необходим для уменьшения t здср , т. к. позволяет

обеспечить малое выходное сопротивление элемента как в состоянии лог. «1», так и лог. «0» и тем самым достаточно быстро перезаряжать нежелательные входную емкость последующих логических элементов и емкость монтажа. Цепь, состоящая из резисторов R3, R4 и транзистора VT3 позволяет улучшить прямоугольность передаточной характеристики. Диоды VD1, VD2 выполняют защитную функцию, предотвращая попадание на вход больших отрицательных напряжений.

Такое построение логического элемента позволяет получить И-НЕ с числом входов до восьми, при этом к выходу такого элемента допускается подключать до десяти входов однотипных элементов. Параллельное соединение выходов таких элементов не допускается. К одному из существенных недостатков этого схемного решения является большой импульсный «сквозной» ток во время изменения логического состояния выхода элемента, когда транзистор VT5 еще не успел закрыться, поскольку был в состоянии насыщения, а VT4 уже открылся. Поэтому с увеличением частоты переключения растет и потребляемая элементом от источника питания мощность. Для ограничения этого тока служит резистор R5.

Для решения вспомогательных задач, например подключение элементов индикации, исполнительных узлов (реле и пр.), были разработаны элементы ТТЛ с открытым коллектором, где в схеме отсутствуют R3, R4, R5, VD3, VT3, VT4. При этом быстродействие существенно уменьшается, но появляются дополнительные возможности. Кроме описанного элементы с открытым коллектором позволяют, там, где не требуется высокого быстродействия, параллельно соединять несколько выходов, реализуя тем самым операцию монтажного ИЛИ-НЕ. При этом соединенные выходы необходимо подключить через резистор к источнику Uпит.

Существуют и ТТЛ элементы с увеличенной нагрузочной способностью, при этом транзистор VT4 выполняется в виде составного по схеме Дарлингтона. При этом к выходу элемента допускается подключать в 3…5 раз больше входов.

Повышение быстродействия ТТЛ элементов возможно за счет уменьшения величины сопротивления R2, R4. При этом уменьшается время перезаряда емкостей коллекторных переходов VT4, VT5. Такое решение хотя и позволяет увеличить быстродействие в 3 – 4 раза, но применяется редко, поскольку существенно возрастает

|

74 |

потребляемая мощность. Дальнейшие |

исследования привели к разработке ТТЛ с |

диодами Шотки – ТТЛШ. Дело в том, что основной вклад в t здср , вносит время

рассасывания неосновных носителей после насыщения VT1, VT2, VT5. Поэтому было найдено решение с шунтированием коллекторных переходов транзисторов диодами с барьерами Шотки. При этом транзисторы работают без захода в область насыщения и t здср при том же потребляемом токе уменьшается более чем в 5 раз. Диоды Шотки

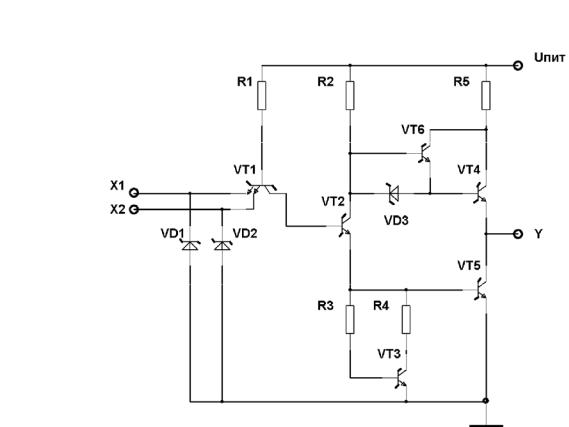

образуются контактом металла с полупроводником и имеют пороговое напряжение открывания примерно в два раза меньше по-сравнению с обычными переходами. Поскольку они включены параллельно коллекторным переходам, насыщения последних не происходит. С другой стороны накопление заряда в самих диодах Шотки не происходит. Схема базового элемента 2И-НЕ ТТЛШ приведена на рис. 10. Разработаны также элементы ТТЛШ, имеющие быстродействие такое же, как у ТТЛ, но потребляющие ток на порядок меньше, что особенно актуально при создании БИС и СБИС, где степень интеграции ограничивается потребляемой микросхемой мощностью.

Рис. 10. Схема электрическая принципиальная элемента 2И-НЕ ТТЛШ.

3.3.2. Интегральные микросхемы на МОП-структурах

75

В большей части современных цифровых устройств используются микросхемы на МОП-структурах. Эта популярность обусловлена высоким быстродействием при низкой потребляемой мощности особенно в статическом режиме, высокой технологичностью изготовления. Эти микросхемы названы так потому, что их работа основана на регулировании величины тока в приповерхностном слое полупроводникового материала за счет влияния поперечного электрического поля на проводимость канала, т. е. здесь используются полевые транзисторы. Практическое применение получили полевые транзисторы с индуцируемым каналом с оксидной изоляцией затворов, образующие структуру металл-окисел-полупроводник (МОП), и транзисторы с комбинированной нитридно-оксидной изоляцией. Последние используются в запоминающих устройствах. В отличие от биполярных ток в канале создается основными носителями, что обуславливает их высокое быстродействие, т. к. процессы рассасывания носителей заряда в этих приборах отсутствуют.

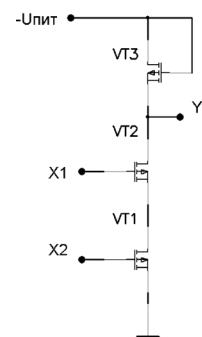

Существуют полевые транзисторы с каналами n-типа и p-типа. Существуют и достаточно широко используются устройства трех типов: статического, квазистатического и динамического типов. В схемах квазистатического и динамического типов используется свойство высокого входного сопротивления МОП транзисторов, откуда вытекает способность емкости затвора длительное время сохранять заряд и уровень напряжения на затворе. Схемы этого типа широко применялись для построения последовательностных устройств: триггеров, регистров, счетчиков. В настоящее время наиболее часто используются схемы статического типа. На рис. 11 приведена схема электрическая принципиальная базового элемента И-НЕ на р-канальных МОП-транзисторах.

76

Рис. 11. Схема электрическая принципиальная элемента 2И-НЕ на р-канальных МОП-транзисторах.

Для реализации функции И-НЕ ключевые транзисторы VT1, VT2 включены последовательно с нагрузочным транзистором VT3. При наличии логических «1» на входах Х1, Х2 ключевые транзисторы VT1, VT2 открываются, через нагрузочный транзистор VT3 протекает ток, а на выходе Y устанавливается логический «0» (отрицательное напряжение близкое к 0). При наличии хотя бы одного логического «0» на входах Х1, Х2 ток в последовательно соединенных транзисторах не протекает и на выходе Y устанавливается логическая «1» (отрицательное напряжение близкое к Uпит). Эти схемы являются схемами отрицательной логики, т. к. логической «1» соответствует отрицательное напряжение на логических входах. Учитывая очень высокое входное сопротивление входных ключей (более 1012 Ом), цифровые устройства на их основе имеют очень высокую нагрузочную способность (более 20). Такое построение логических элементов имеет существенные недостатки:

-невысокое быстродействие, т. к. эквивалентное сопротивление нагрузочного транзистора составляет ~ 30 кОм, а емкость нагрузки при 10 подключенных входах составляет ~ 20 пФ, что обуславливает минимальное время задержки ~ 0,5 мкс;

-постоянное протекание тока при логическом «0» на выходе.

-для сопряжения с микросхемами серий ТТЛ(ТТЛШ) требуются специальные преобразователи уровней.

|

77 |

Основным достоинством является |

технологическая простота изготовления |

этих микросхем, т. к. они содержат всего лишь один элемент – полевой транзистор. Ограничения по быстродействию, характерные для МОП схем с р-каналами, могут быть частично устранены с помощью использования в схемах n-канальных МОП структур. Подвижность электронов в полупроводнике больше, чем подвижность дырок, поэтому скорость переключения вентилей на n-канальных МОП транзисторах в 2-3 раза больше. К тому же логические уровни и напряжения питания у них такие же, как у ТТЛ.

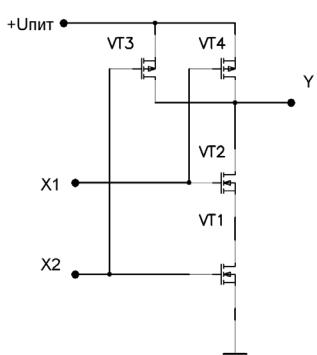

Дальнейшее совершенствование цифровой техники на МОП структурах привело к появлению комплементарных МОП (КМОП) элементов. На рис. 12 приведена схема электрическая принципиальная базового элемента И-НЕ на комплементарных МОПтранзисторах.

Рис. 12. Схема электрическая принципиальная элемента 2И-НЕ на КМОП-транзисторах.

Как видно из схемы на рис. 12, здесь параллельно включены транзисторы р-типа и последовательно транзисторы n-типа. При подаче на любой из входов напряжения логического «0» соответствующий транзистор (VT1 или VT2) закрывается, при этом VT3 или VT4 открывается. При этом на выходе микросхемы устанавливается уровень логической «1». При одновременном наличии на обоих входах логической «1», транзисторы VT1 и VT2 открыты, а VT3 и VT4 закрыты. При этом на выходе микросхемы устанавливается уровень логического «0». Ток через транзисторы

|

78 |

протекает только при изменении |

логического состояния для перезаряда |

емкости, образованной емкостями входов, подключенных к выходу и емкостью монтажа.

В статическом состоянии потребляемый ток очень мал и определяется только сквозными токами утечки транзисторов. С другой стороны выходное сопротивление элемента невелико, что обуславливает высокое быстродействие устройства. В настоящее время созданы элементы, имеющие времена задержки единицы нс. Рассмотренная структура КМОП логического элемента в настоящее время является наиболее часто используемой в цифровой технике. Следует отметить, что рассмотренный КМОП элемент относится к положительной логике. Причем для большинства типов КМОП возможно совместное использование с ТТЛ (ТТЛШ) микросхемами без специальных устройств согласования, т. к. они имеют те же величины напряжений логических уровней и напряжений питания.

3.3.3. Микросхемы эмиттерно-связанной транзисторной логики

Цифровые микросхемы эмиттерно-связанной логики ЭТСЛ представляют собой транзисторные переключательные схемы с объединенными эмиттерами и обладают наибольшими по-сравнению с другими типами микросхем быстродействием и большой потребляемой мощностью. Большое быстродействие обусловлено тем, что в этих ключах биполярные транзисторы работают в ненасыщенном (линейном) режиме. На выходах ключей установлены эмиттерные повторители, ускоряющие процесс перезаряда емкости нагрузки. Уменьшение времени задержки достигается также и за счет уменьшения разности напряжений между лог. «0» и лог. «1», что, однако приводит к снижению помехоустойчивости.

Рассмотрим принцип работы ЭТСЛ на примере базового логического элемента, выполняющего одновременно функции ИЛИ-НЕ и ИЛИ (рис. 13).

Схема состоит из дифференциального усилителя на транзисторах VT1…VT3. В этом усилителе при подаче логических уровней на входы Х1, Х2 ток может протекать либо через транзистор VT3 (когда на обеих входах установлено напряжение логического «0» (U 0 =-1,65 В), либо через транзисторы VT1 или VT2 или оба вместе при подаче на один или оба входа напряжения лог. «1» (U1 =-0,96 В). Выходные эмиттерные повторители VT5,VT6 подключаются к источнику смещения -2 В через внешние резисторы 50 Ом. Когда закрыт VT3 на выходе Y1 устанавливается напряжение

|

79 |

-0,96 В, соответствующее лог. «1», а на |

выходе Y – напряжение -1,85 В, |

Рис. 13 Схема электрическая принципиальная ЭТСЛ элемента ИЛИ-НЕ / ИЛИ соответствующее лог. «0». Когда VT3 открыт, на выходе Y устанавливается напряжение -0,96 В, соответствующее лог. «1», а на выходе Y1 – напряжение -1,85 В, соответствующее лог. «0». Микросхемы ЭТСЛ при использовании совместно с ТТЛ, или КМОП микросхемами требуют применения специальных преобразователей уровня. Достаточно высокое входное сопротивление ЭТСЛ (~ 50 кОм), и низкое выходное, обуславливают высокий коэффициент разветвления (более 15).

Большая потребляемая мощность, наличие большого числа компонентов в логических элементах ограничивают применение ЭТСЛ в БИС и СБИС.

3.3.4. Инжекционные интегральные логические схемы (И2Л)

Для повышения технологичности изготовления желательно при разработке ИС применять схемотехнические решения, использующие только однотипные элементы, например транзисторы. Этот путь, как было показано ранее, реализован в ИС МДП, что наряду с другими достоинствами является причиной их широкого распространения. Однако, как уже отмечалось, ключ на биполярных транзисторах на сегодняшний день обладает лучшими как ключевыми, так и частотными свойствами. Это является предпосылкой к постоянному поиску новых схемотехнических решений для реализации биполярных ИС. Такой поиск привел к почти одновременной разработке фирмами Philips и IBM элемента интегральной инжекционной логики

(И2Л).

В основе И2Л схем лежат дна принципа |

80 |

схемотехники и технологии биполярных |

схем: 1) совмещение электрически связанных однородных областей полупроводника в кристалле ИС, что приводит к увеличению степени интеграции; 2) отказ от традиционного способа питания цепи базы и коллектора ключевых транзисторов через резисторы.

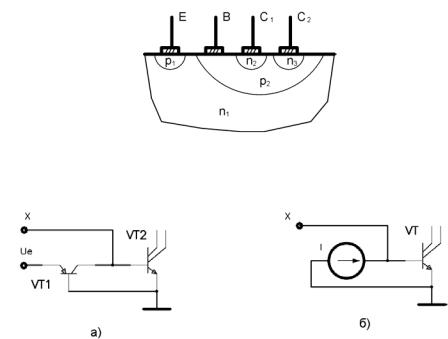

На рис. 14 показана инжекционная структура с дополнительным р — n-переходом. Если база (область р2) переключающего вертикального транзистора n2 — р2 — n1 -типа расположена вблизи прямосмещенного перехода р1—n1, то часть инжектированных данным переходом дырок попадает в область базы р2. В результате нарушения электронейтральности базы этого транзистора через переход база — эмиттер начинает протекать ток, смещающий этот переход в прямом направлении. Область р1, введенную для инжекции избыточных носителей, называют инжектором Е. Питание инжектора осуществляется от внешнего генератора тока или от источника напряжения через резистор (один внешний резистор).

Рис. 14. Упрощенная топология элемента И2 Л

Рис. 15. Эквивалентная схема элемента И2 Л

Данную инжекционную структуру можно представить в виде схемы, содержащей два транзистора: токозадающий горизонтальный р1—n1—р2-типа (включен по схеме с общей базой) и переключающий вертикальный n2 — p2—n1-типа (рис. 15, а). Упрощенная эквивалентная схема состоит из транзистора n — p — n-типа и генератора тока I в цепи его базы (рис. 15б). Обычно транзистор n — p — n-типа выполняется с несколькими коллекторами (область n3 на рис. 14).