Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf

|

211 |

- простая, когда обращение к ячейке |

памяти осуществляется по адресу, |

находящемся в индексном регистре, т. е. никаких действий над его содержимым не проводится;

-относительной, когда адрес суммированием содержимого индексного регистра и числа, задаваемого в команде. Существуют и другие разновидности косвенной адресации.

-при непосредственной адресации в команде содержится сам операнд. Возможность использования различных видов адресации сокращает объем и время

выполнения программ.

С помощью того или иного способа адресации формируется физический адресный код, поступающий на шину адреса для выбора ячейки памяти или внешнего устройства с которы в данный момент взаимодействует процессор.

Адресация может быть абсолютной или неабсолютной. При абсолютной адресации обратиться к ячейке памяти или внешнему устройству можно только по одному единственному адресу. При неабсолютной адресации для ячейки памяти или внешнего устройства выделяется некоторая зона адресов. Число таких зон, естественно, будет меньше, чем число отдельных адресов, поэтому для указания зоны потребуется меньшая разрядность адреса.

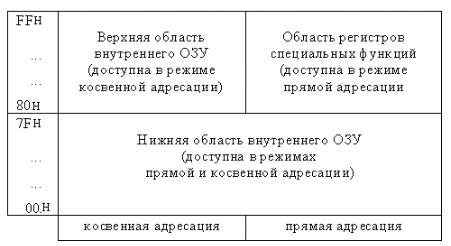

Структура внутренней памяти данных рассматриваемого микроконтроллера представлена на рис. 2.4.

Рис. 2.4. Структура внутренней памяти данных MCS-51

Внутренняя память данных всегда адресуется байтом, что подразумевает 256 байт адресного пространства. Однако фактически можно обращаться к 384-м байтам.

|

212 |

Прямая адресация ячейки с адресом |

свыше 7Fh осуществляет доступ к |

области регистров специальных функций, а косвенная - к верхней области внутренней памяти данных. Т.о. эти две области занимают одно и то же адресное пространство, хотя и разделены физически. Все байты в нижней 128-байтной половине внутренней памяти данных могут адресоваться как прямо, так и косвенно.

Первые 32 байта в нижней области внутреннего ОЗУ сгруппированы в 4 банка по 8 регистров. Инструкции программы могут оперировать с ними как с регистрами общего назначения R0-R7. Два бита регистра PSW определяют, какой из банков используется в текущий момент. Это позволяет более эффективно использовать память программ, поскольку регистровые инструкции короче, чем прямая адресация. Переключение регистровых банков эффективно заменяет операции сохранения регистров в стеке на время обработки прерывания.

Следующие за регистровыми банками 16 байт образуют блок побитно адресуемого пространства. Набор инструкций MCS-51 содержит широкий набор операций над битами, а 128 бит (16 байт по 8) в этом блоке могут быть прямо адресованы. Битовые адреса имеют значения от 00h до 7Fh.

Для 16 адресов в пространстве SFR (регистры специальных функций) имеется возможность как битовой, так и байтовой адресации. Побитово-адресуемыми регистрами являются те, чей шестнадцатеричный адрес заканчивается на “0” или “8”. Битовые адреса в этой области располагаются со значения 80h по FFh.

Наиболее часто используемыми регистрами специальных функций являются:

-Аккумулятор (байтовый адрес 0E0h). Используется во всех арифметических и логических операциях в качестве операнда;

-Регистр B (байтовый адрес - 0F0h). Используется при операциях умножения и деления, а также как сверхоперативный регистр;

-Слово состояния программы PSW (байтовый адрес - 0D0h). Содержит информацию о состоянии программы;

-Указатель стека (байтовый адрес -081h). Используется для указания на вершину стека в операциях записи в стек и чтения из него. По аппаратному сбросу устанавливается в значение 07h (область стека в этом случае начинается с адреса 08h) и инкрементируется при каждой записи в

|

213 |

стек. Запись в SP |

производится для предопределения |

положения стека во внутренней памяти данных микроконтроллера;

- Указатель данных DPTR (байтовые адреса 082h, 083h). Состоит из двух байт: старшего - DPH и младшего - DPL. Используется как 16-ти или 8- битовый указатель адреса при обращении к внешней памяти или выполнении команды перехода по косвенному адресу.

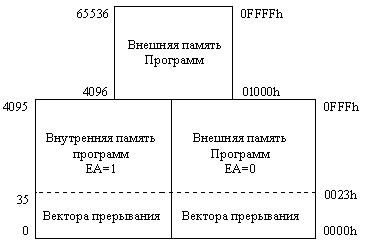

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом 64 Кбайт, причем для некоторых микросхем (например КР1816ВЕ51, КМ1819ВЕ751, КР1830ВЕ51) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область млаших адресов памяти программ. Учитывая, что выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, то при включении питания начнет выполняться программа, записанная во внутненнем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (например КР1816ВЕ31 и КР1830ВЕ31) могут работать только с внешней микросхемой ПЗУ емкостью до 64 Кбайт (при использовании портов P1 и P3 в качестве расширителя адреса объем подключаемой ПЗУ может быть увеличен до 1Гбайта). Микроконтроллеры семейства MCS-51 имеют внешний вывод EA, с помощью которого можно запретить работу внутренней памяти, для чего необходимо подать на вывод EA логический "0" (соединить этот вывод с корпусом). При этом внутренняя память программ отключается и, начиная с нулевого адреса, все обращения происходят к внешней памяти программ.

Доступ к внешней памяти программ осуществляется в двух случаях:

1.при действии сигнала EA=0 независимо от адреса обращения,

2.в любом случае, если программный счетчик (РС) содержит число большее, чем максимальная ячейка внутренней памяти программ.

Распределение памяти программ микроконтроллера АТ89С52 представлено ниже:

214

Для чтения памяти программ используются команды

MOVC A, A+@DPTR и MOVC A, A+@PC

Рис. 2.5. Адресное пространство памяти программ.

Для других микроконтроллеров этого семейства изменяется только объем внутренней памяти программ и количество доступных векторов прерываний программы.

Ниже приведены адреса векторов прерываний и соответствующие им аппаратурные источники прерываний программы:

Вектор |

Флаги, вызывающие |

Источник прерывания |

|

|

прерывания |

прерывание |

|

|

|

|

|

|

||

0000Н |

- |

Рестарт (сброс) контроллера RESET |

||

|

|

|

|

|

0003Н |

IE0 |

внешнее прерывание INT0 |

|

|

|

|

|

|

|

000bН |

TF0 |

Таймер 0 |

|

|

|

|

|

|

|

0013Н |

IE1 |

внешнее прерывание INT1 |

|

|

|

|

|

|

|

001bН |

TF1 |

Таймер 1 |

|

|

|

|

|

|

|

0023Н |

RI, TI |

Последовательный порт |

|

|

|

|

|

|

|

002bН |

TF2, EXF2 |

Таймер 2 |

|

|

|

|

|

|

|

0033Н |

CF, CCFn(n=0:4) |

Набор |

программируемых |

счётчиков |

|

|

(РСА) |

|

|

|

|

|

||

003bН |

AIF |

Аналого-цифровой преобразователь |

||

|

|

|

|

|

0043Н |

CF1,C1CCFn(n=1:4) |

Набор |

программируемых |

счётчиков |

|

|

(РСА1) |

|

|

|

|

|

|

|

004bН |

SEPIF |

Последовательный порт SEP |

|

|

|

|

|

|

|

0053Н |

IE2 |

внешнее прерывание INT2 |

|

|

|

|

|

|

|

005bН |

IE3 |

внешнее прерывание INT3 |

|

|

|

|

|

|

|

0063Н |

IE4 |

внешнее прерывание INT4 |

|

|

|

|

|

|

|

006bН |

IE5 |

внешнее прерывание INT5 |

|

|

|

|

|

|

|

0073Н |

IE6 |

внешнее прерывание INT6 |

|

|

|

|

|

|

|

Примечание: вектора прерывания, выделенные:

1. жирным подчеркнутым текстом- |

215 |

присутствуют во всех микросхемах |

|

семейства; |

|

2.жирным текстом- отсутствуют в микросхемах 8051,8031, КР1816ВЕ31,

КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751;

3.обычным текстомприсутствуют только в микросхемах 8Х51FA, FB, FC и GB

4.курсивом- присутствуют только в микросхеме 8Х51GB

Система команд микроконтроллера предоставляет большие возможности обработки данных, обеспечивает реализацию логических, арифметических операций, а также управление в режиме реального времени.

Реализована побитная, потетрадная (4 бита), побайтовая (8 бит) и 16-разрядная обработка данных. Микросхемы семейства MCS-51 - это 8-разрядные микропроцессоры, а это означает, что ПЗУ, ОЗУ, регистры специального назначения, АЛУ и внешние шины имеют байтовую организацию.

Двухбайтовые данные используются только регистром-указателем (DPTR) и счетчиком команд (PC).

В машинном коде команда занимает один, два или три байта в зависимости от типа адресации.

Команды выполняются за один, два или четыре (умножение и деление) машинных цикла.

Все множество команд, выполняемых микроконтроллером, можно разбить на следующие группы:

●команды пересылки данных;

●команды арифметических операций;

●команды логических операций;

●команды операций с битами;

●команды передачи управления;

●команды управления системой (специальные команды).

2.2.2. Архитектура AVR микроконтроллеров

Как было сказано ранее микроконтроллеры AVR представляют собой восьми разрядные RISC-микроконтроллеры с Гарвардской архитектурой и пониженным энергопотреблением. Набор команд, ограниченность которого свойственна RISC-

|

216 |

архитектурам тем не менее необычно |

широк (120 команд), однако при этом |

сохранено основное преимущество RISC-архитектур повышенное быстродействие и сокращенное число операций обмена с памятью программ. Почти все команды размещаются в одной ячейке программной памяти и выполняются за один такт синхросигнала.Доступ к памяти данных и памяти программ осуществляется по разным шинам (по собственным шинам этих модулей), поэтому можно не только сделать различными разрядности этих шин, но и реализовать параллельное выполнение текущей команды и выборку и дешифрацию следующей.

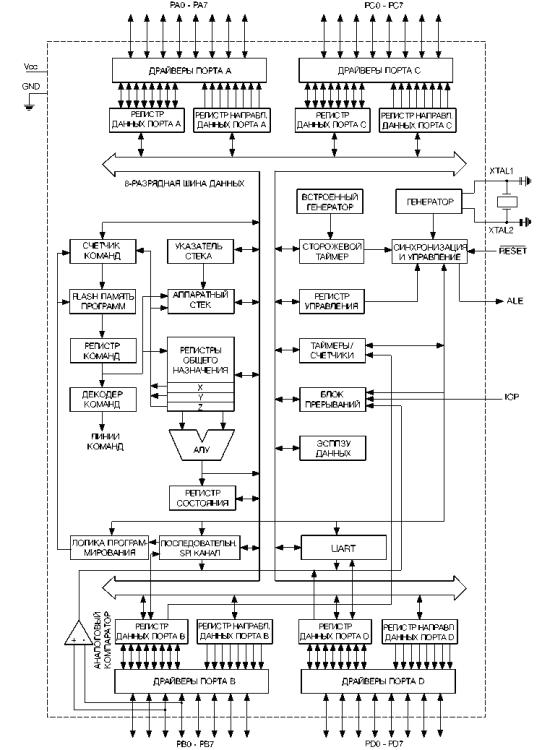

На рис. 2.6 представлена структурная схема микроконтроллера АТ90S8515. Многие блоки по назначению аналогичны рассмотренным ранее блокам микроконтроллера и имеют такое же назначение. В памяти ЭСППЗУ (EEPROM) хранятся редко изменяемые данные ( калибровочные константы и т. п.), Указатель стека используется для организации стека в некоторой области памяти Аппаратного Стека (SRAM). Микроконтроллер имеет 32 программно доступных регистра общего назначения (РОН), которые объединены в регистровый файл. В отличие от ранее рассмотренного микроконтроллера здесь АЛУ способно выполнять операции над содержимым любой пары РОН , т. е. все регистры непосредственно доступны для АЛУ и регистр – аккумулятор не требуется. Регистр состояния аналогичен рассмотренному ранее регистру PSW и выполняет те же функции.

Структура портов ввода – вывода немного отличается от предыдущего микроконтроллера. Порт представляет собою набор из восьми линий. Каждая из восьми линий любого порта конфигурируется как входная или выходная индивидуально с помощью управляющего слова, загружаемого в регистр направления передачи. Каждый бит этого слова задает конфигурацию своей линии. Вводимые или выводимые данные поступают в регистр данных. Входные и выходные сигналы проходят через буферные каскады (драйверы).

Последовательный SPI (Serial Peripheral Interface) периферийный канал применяется как для программирования микроконтроллера в последовательном режиме, так и для обмена данными с периферийными устройствами или между микроконтроллерами, если они работают в системе. Протокол обмена для SPI предусматривает работу в режиме либо ведущего (master), либо ведомого (slave).

|

217 |

Асинхронный последовательный |

интерфейс между микроконтроллером и |

внешними устройствами обеспечивается рассмотренным ранее блоком UART. Кроме этого в рассматриваемом микроконтроллере имеется аналоговый компаратор напряжения, подключенный к двум специально выделеным линиям порта В. Компаратор позволяет реализовывать ряд достаточно необходимых функций, например, служить формирователем при измерении длительности или частоты следования импульсов входного сигнала, служить в качестве элемента простейшего АЦП с обратным интегрированием и т. п.

Рис. 2.6. Структурная схема микроконтроллера AVR

|

218 |

Организация памяти и |

функционирование микроконтроллера |

|

AVR. |

Согласно Гарвардской архитектуре, адресные пространства (АП) для памяти программ

ипамяти данных разделены. Память данных организована линейно и имеет два адресных пространства. В первом находятся адреса регистровой памяти и адреса статического ЗУ (SRAM). Во втором размещены адреса энергонезависимой репрограммируемой памяти (EEPROM). Кроме того, возможно подключение к микроконтроллеру внешнего ОЗУ, для которого шины адреса и мультитиплексируемая шина адресов/данных организуется с помощью портов ввода/вывода РА и РС. Линии этих портов формируют 16-разрядные адреса для работы с внешней памятью больших объемов.

Распределение адресного пространства иллюстрируется рис. 2.7.

В регистровой области памяти размещены адреса регистров общего назначения РОН (32 адреса) и регистров ввода/вывода РВВ (64 адреса для адресации 64 байтов памяти). Соответственно общая емкость регистровой памяти составляет 96 байтов. Для адресов статической памяти отведены следующие 512 адресов. Подключение внешнего ОЗУ, как уже отмечалось, может довести емкость до 64 Кбайт. Обращение к внешнему ОЗУ увеличивает время выполнения команды на 1-2 такта для каждого обрабатываемого байта.

В пространстве РВВ размещаются операнды, служебные регистры микроконтроллера

ирегистры, относящиеся к внешним устройствам. В их числе 12 регистров для работы

спортами ввода/вывода ( для каждого порта предусмотрены регистр данных, регистр направления данных и регистр выводов. Имеется также регистр – указатель стека. Энергонезависимая память EEPROM, рассчитана на хранение редко изменяемых данных и имеет длительные операции записи, отличающиеся особым алгоритмом. Доступ к ней производится посредством трех регистров РВВ.

Программы, хранятся во флэш-памяти, а ее разрядность соответствует формату команд и составляет два байта.

Повышению производительности микроконтроллера способствует выполнение почти всех команд за один такт. Такая возможность – следствие конвейерной обработки

219

Рис. 2.6. Адресные пространства микроконтроллера AVR

информации и непосредственного подключения АЛУ ко всем РОН. В нормальном режиме работы конвейера параллельно выполнению текущей команды происходит выборка и декодирование следующей. При нарушении последовательного следования команд, например при появлении команды условного перехода, в работе конвейера возникает разрыв и время выполнения команды увеличивается до 2-4 тактов.

Начало выполнения программы инициируется сигналом сброса, после которого микроконтроллер обращается к стартовому адресу программы.

В ходе выполнения программы микроконтроллер выполняет команду за командой, пока не дойдет до команды останова. Большая часть микропрограмм построена так, что определенный набор микрокоманд выполняется циклически, т. е. необходимость в команде останова отпадает.

Все множество команд, выполняемых микроконтроллером, можно разбить на следующие группы:

●команды пересылки данных;

●команды арифметических сдвигов;

●команды логических операций;

220

●команды операций с битами;

●команды передачи управления;

●команды управления системой.

Сопоставляя перечисленные группы команд с рассмотренными в предыдущей главе для CISC процессоров, можно отметить их большое сходство. Специфичная группа команд операций с битами содержит команды установки и сброса заданного разряда в регистре РОН или РВВ. Для удобства программирования задействованным разрядам регистров РВВ присваиваются символические имена, определение которых дается в специальном файле, подключаемом вначале программы.

3.Программирование микроконтроллеров

3.1Языки программирования для микроконтроллеров

Программирование для микроконтроллеров, как и программирование для универсальных компьютеров прошло большой путь развития от программирования в машинных кодах до применения современных интегрированных систем написания программ, отладки и программирования микроконтроллеров. В настоящее время исходный текст программы пишется на одном из языков программирования. Процесс преобразования операторов исходного языка программирования в машинные коды микропроцессора называется трансляцией исходного текста. В настоящее время ручная трансляция программ практически не используется. Трансляция производится специальными программамитрансляторами.

Существует два больших класса программ-трансляторов: компиляторы и интерпретаторы . При использовании компиляторов весь исходный текст программы преобразуется в машинные коды, и именно эти коды записываются в память микроконтроллера. При использовании интерпретатора в память микроконтроллера записывается исходный текст программы, а трансляция производится при считывании очередного оператора. Естественно, что быстродействие интерпретаторов намного ниже по сравнению с компиляторами, т.к. при использовании оператора в цикле он транслируется многократно. Однако при программировании на языке высокого уровня объем кода, который нужно хранить во внутренней памяти может быть значительно меньше по сравнению с исполняемым кодом. Еще одним преимуществом применения интерпретаторов является легкая переносимость программ с одного процессора на другой.