Рабочий стол / Alaev_A_N (1) / Алаев А.Н / DIGITAL_Konsp

.pdf

|

81 |

Когда транзисторы VT1 и VT2 закрыты, |

транзистор VT3 открыт током инжектора |

I (сплошная линия прохождения тока на рис. 16) и напряжение в узле 2 И2Л

U 2 =U эб =0,75 В (лог. «1»)

Рис. 16. Эквивалентная схема структуры И2 Л

что соответствует уровню логической 1. Если транзистор VT2 откроется, то ток инжектора VT3 переключится в цепь коллектора VT2 (пунктирная линия на рис. 16) и транзистор VT3 закроется. В узле 2 будет напряжение насыщения коллектора VT2:

U 2 =U эб =0,05 В (лог. «0»).

Площадь, приходящаяся на один ЛЭ в схемах в И2Л, приблизительно в 10 раз меньше, чем в схемах ТТЛ. Применение диодов Шотки в схемах И2Л позволяет без увеличения потребляемой мощности получить еще более высокое быстродействие.

Высокое быстродействие элементов И2Л при малой потребляемой мощности объясняется незначительными паразитными емкостями, отсутствием накопления заряда и очень небольшой разницей логических уровней. Типичное время задержки составляет 10 нс, а использование структур И2 Л с диодами Шотки позволяет получить время задержки менее 0,1 нс.

3.3.5. Схемные особенности логических элементов

Рассмотренные логические элементы могут иметь некоторые схемотехнические особенности построения выходных каскадов. Рассмотрим основные из них на примере ТТЛ элементов, учитывая при этом, что подобные решения применяются и для логических элементов, выполненных с использованием других технологий. Наряду с базовым элементом И-НЕ, рассмотренным ранее, там, где не требуется высокого быстродействия, широко используются элементы И-НЕ с «открытым коллектором». Упрощенное схемное изображение этого элемента представлено на рис. 17.

82

Рис. 17. Упрощенная схема элемента 2И-НЕ с открытым коллектором Этот элемент требует подключения внешней нагрузки, в качестве которой могут использоваться резистор, исполнительные устройства (реле, двигатели и т. п.), элементы индикации. Элементы с открытым коллектором допускают, в отличие от основной схемы параллельное соединение выходов с целью получения «монтажного ИЛИ».

Кроме элементов с открытым коллектором иногда используются логические элементы с «открытым эмиттером». Они обозначаются

знаком ◊ .

Вместе с элементами с двумя логическими состояниями используются элементы, имеющие третье (нейтральное) состояние. При переходе элемента в третье состояние, его выходное сопротивление становится очень большим и выход элемента не оказывает влияния на соединенные параллельно с ним входы и выходы других элементов. Такие элементы носят название тристабильных.

Упрощенная схема тристабильного элемента 2И-НЕ приведена на рис. 18.

Рис. 18. Упрощенная схема тристабильного элемента 2И-НЕ

|

83 |

Если сигнал ОЕ (Output Enable) низкого |

уровня, дополнительный транзистор |

закрыт и включенные встречно диоды не оказывают влияния на работу выходного каскада. Если сигнал ОЕ высокого уровня, дополнительный транзистор входит в состояние насыщения, закрывая транзисторы выходного каскада и логический элемент переходит в третье состояние.

Такие элементы используются там, где необходима передача информации по одной линии от нескольких источников к одному или нескольким приемникам (многоканальные системы уплотнения с временным уплотнением сигналов), а также при разработке микросхем сложных логических устройств, где один вывод микросхемы реализует несколько функций.

3.4. Сложные комбинационные цифровые автоматы

При разработке сложных логических устройств необходимо выполнять логические операции И, ИЛИ, НЕ над большим числом переменных. При этом использование простых логических элементов базовой логики, рассмотренных ранее ведет к значительному усложнению печатных плат, увеличению массогабаритных характеристик, снижению надежности. Поэтому для упрощения технической реализации, уменьшения числа внешних соединений были разработаны и производятся сложные комбинационные логические элементы. Некоторые из них, наиболее часто используемые, рассмотрены в этом разделе.

3.4.1. Сумматор по модулю два

Операция «сумма по модулю 2» (исключающее ИЛИ, логическая неравнозначность) обозначается символом и определяется соотношением:

X Y = |

X |

Y + X |

Y |

=( |

X |

+ |

Y |

) ( X +Y ) , |

(24) |

Операция «сумма по модулю 2» коммутативна, ассоциативна и дистрибутивна |

|

||||||||

относительно конъюнкции, т. е. |

|

||||||||

|

|

X Y =Y X , |

(25) |

||||||

|

X (Y Z ) = (X Y ) Z, |

(26) |

|||||||

|

X (Y Z ) = X Y X Z. |

(27) |

|||||||

Для операции «сумма по модулю 2» справедливы тождества: |

|

||||||||

84

X 0 = X , X 1 = X , X X =1, X X = 0 ,

X Y = X Y = X Y ,

Операция X Y называется операцией исключающее ИЛИ-НЕ.

Логические элементы, выполняющие операцию исключающее ИЛИ и исключающее ИЛИ-НЕ, всегда имеют только два входа, т. е. операция выполняется только для двух переменных.

Таблица истинности для элемента исключающее ИЛИ выглядит следующим образом:

X 2 |

X1 |

Y |

0 |

0 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

На рис. 19 показано условное графическое изображение элемента исключающее ИЛИ.

Рис.19 Условное графическое изображение элемента исключающее ИЛИ

3.4.2. Мультиплексоры и демультиплексоры

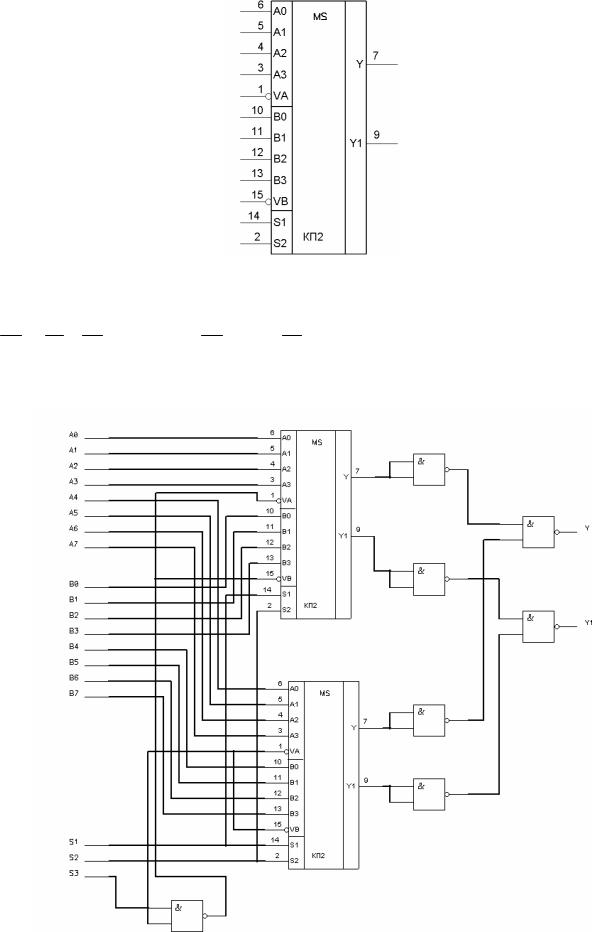

Мультиплексором называется логическое устройство, которое имеет m + 2m входов и один выход, где m- число адресных входов, а 2 m - число информационных входов мультиплексора. В условных графических изображениях мультиплексоры обозначаются буквами MS, MX, MUX. Условное графическое обозначение сдвоенного четырех канального мультиплексора К155КП2 приведено на рис. 20.

85

Рис. 20. Условное графическое изображение сдвоенного четырех канального мультиплексора К155КП2

Логическое уравнение для выхода Y будет иметь вид:

Y =VA (S1 S2 A0 + S1 S2 A1 + S1 S2 A2 + S1 S2 A3 ). (30)

Входы VA, VB используются при необходимости увеличения числа коммутируемых входов как показано на рис. 21.

Рис. 21. Пример схемы электрической принципиальной сдвоенного мультиплексора на 8 каналов на микросхемах К155КП2.

|

86 |

Входы VA, VB могут использоваться |

также и для других целей, например в |

качестве стробирующих для устранения эффекта гонок. |

|

Демультиплексоры выполняют функцию обратную мультиплексированию, т. е.

производят коммутацию одного входного сигнала на 2m выходов, где m число адресных входов. Демультиплексоры описываются системой логических уравнений:

Yi = x mi ; i = 0,...,2n −1,

где mi - минтермы переменных,

например, для n=2 и адресных входах S1 , S2 :

m0 = S1 S2 , m1 = S1 S2 ,

m2 = S1 S2 , m3 = S1 S2 .

В условных обозначениях демультиплексор обозначается буквами DMX, DM.

Основное назначение демультиплексоров – разделение последовательных потоков данных, например при использовании в системах с временным уплотнением каналов, цифровых АТС и т. п.. Условное графическое изображение демультиплексора приведено на рис. 22.

Рис.22. Условное графическое изображение четырехканального демультиплексора. Следует отметить, что микросхемы демультиплексоров применяются редко, а наиболее часто в качестве демультиплексоров используются микросхемы дешифраторов – демультиплексоров, рассмотренные далее.

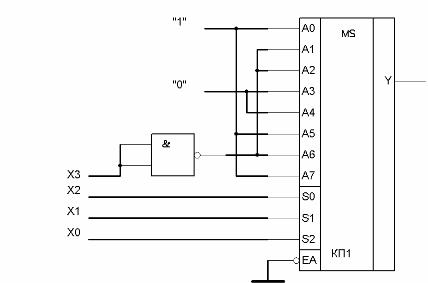

Мультиплексоры находят широкое применение и при создании СБИС, например для сокращения числа выводов микропроцессоров. Кроме основного назначения мультиплексоры могут использоваться для синтеза комбинационных схем.

|

87 |

Рассмотрим пример синтеза |

комбинационного автомата с |

использованием восьми канального мультиплексора. Пусть автомат выполняет логическую функцию, заданную таблицей истинности табл. 3.1.

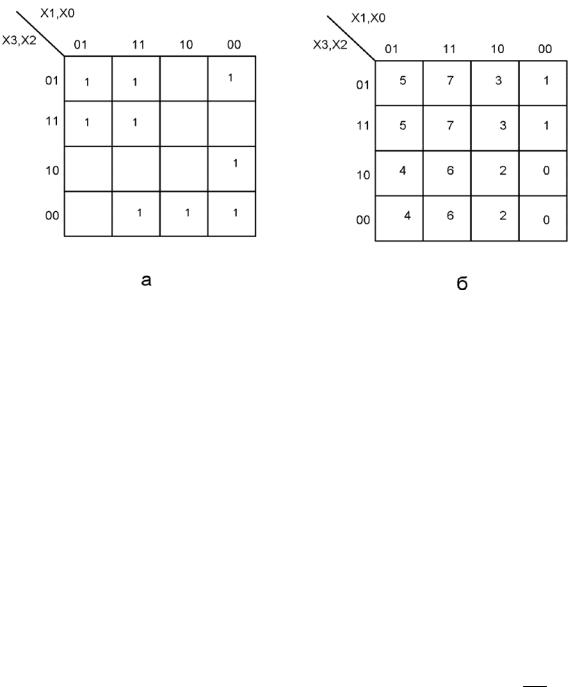

По этой таблице построена карта Карно рис. 23а. Правило выбора адресных переменных устанавливается из соображений, что для наиболее рационального использования адресных входов мультиплексора, им необходимо присваивать значения тех переменных, которые входят в ДНФ наибольшее число раз. Из таблицы Карно следует, что ДНФ функции Y имеет вид:

Y = X 0 X 2 + X1 X 2 X 3 + X 0 X1 X 2 + X 0 X 2 X 3 ,

В этой формуле наиболее часто встречаются X 2 , X 0 , поэтому на адресный вход S3 подаем X 0 , на адресный вход S2 подаем X 2 и на адресный вход S1 можно подать как

X 3 так и X1 . Подадим на S3 X1 . Адреса, соответствующие такому выбору указаны на карте рис. 23б.

|

|

|

|

Таблица 3.1. |

|

|

|

|

|

|

|

|

|

№ |

X3 |

X2 |

X1 |

|

X0 |

Y |

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

2 |

0 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

4 |

0 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

6 |

0 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

8 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

10 |

1 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

12 |

1 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

14 |

1 |

1 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

16 |

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

88

Рис. 23. Карта Карно и карта адресов комбинационного автомата. Сигналы, подаваемые на входы А0…А7 мультиплексора определим на основании рис.23 следующим образом:

-номерам входов соответствуют цифры, записанные в ячейках рис. 23б;

-на вход соответствующий адресу i подается лог. «1», если в обеих ячейках с адресом i в карте Карно записана «1».;

-на вход соответствующий адресу i подается лог. «0», если обе ячейки с адресом i в карте Карно пусты.;

-на вход соответствующий адресу i подается логический сигнал X 3 , если в ячейке с

адресом i и соответствующей X 3 = 1 в карте Карно записана «1», а в ячейке с адресом

i и соответствующей X 3 = 0 в карте Карно пустая ячейка;

- на вход соответствующий адресу i подается логический сигнал X 3 , если в ячейке с

адресом i и соответствующей X 3 = 0 в карте Карно записана «1», а в ячейке с адресом

i и соответствующей X 3 = 1 в карте Карно пустая ячейка;

На основании этих правил разработана схема автомата рис. 24.

89

Рис.24. Схема комбинационного автомата с использованием восьми канального мультиплексора.

В случае если комбинационный автомат одновременно реализует несколько логических функций, синтез производится аналогичным образом. Для каждой функции строятся карты Карно и ДНФ, затем путем сравнения ДНФ находятся наиболее часто встречающиеся переменные, которые подаются на адресные входы, причем каждой функции соответствует свой мультиплексор, а адресные входы мультиплексоров объединяются.

3.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

Дешифраторы преобразуют двоичный код на входах устройства в активный сигнал на том выходе, номер которого равен десятичному эквиваленту двоичного кода на входах. В полном дешифраторе количество выходов равно m = 2n , где n – число входов. В неполном дешифраторе m 2n . На схемах дешифраторы обозначаются DC

(от англ. decoder). Для целей расширения микросхемы дешифратора обычно имеют дополнительный вход EA(VA). Так, например, таблица истинности для полного двух разрядного (n=2) дешифратора таблица истинности имеет вид:

90

Таблица 3.2.

DEC |

А1 |

А0 |

EA |

Y0 |

Y1 |

Y2 |

Y3 |

число |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

2 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

3 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

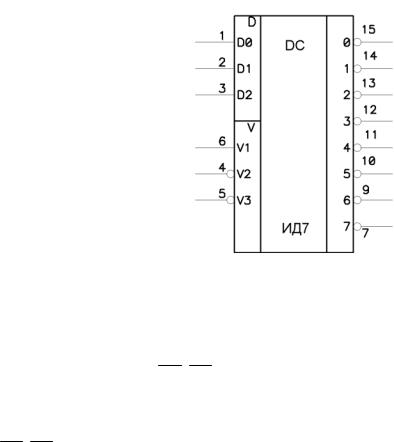

Пример условного обозначения трехразрядного дешифратора К555ИД7 приведен на рис. 25.

Рис. 25. Пример условного обозначения на схемах электрических принципиальных дешифратора К555ИД7.

На этом обозначении информационным входам А0…А2 соответствуют вводы D0…D2,

а входу ОЕ – три входа V1,V 2,V 3. Причем разрешающим состоянием входов разрешения является одновременное наличие лог. «1» на входе V1 и лог. «0» на входах V 2,V 3. Такое устройство микросхемы позволяет без использования дополнительных логических элементов производить наращивание числа разрядов логического устройства.

Как видно по своей структуре дешифраторы очень похожи на демультиплексоры, разница заключается в отсутствии в дешифраторах специального информационного входа. Поэтому, при использования дешифраторов в качестве демультиплексоров, информационным обычно служит один из входов разрешения.