- •Методічні вказівки до лабораторних робіт

- •II-iiIкурсувсіх форм навчання)

- •1 Опис лабораторного стенду та методики його використання

- •2 Лабораторна робота № 1 дослідження роботи логічних елементів та простих комбінаційних схем

- •2.1 Мета лабораторної роботи

- •2.2 Програма лабораторної роботи

- •2.3 Теоретичні відомості

- •2.3.1 Логічне заперечення (інверсія)

- •2.3.2 Логічне множення (кон'юнкція)

- •2.3.3 Логічне складання (диз'юнкція)

- •2.3.4 Аксіоми і закони булевої алгебри

- •2.3.5 Базові електронні елементи

- •2.3.6 Функція «сума по модулю 2»

- •2.3.7 Побудова логічних функцій трьох і більше аргументів

- •2.3.8 Оптимізація логічних функцій. Карти Карно

- •2.4 Завдання, порядок виконання роботи і проведення досліджень

- •2.4.1 Особливості використання лабораторного стенду в даній лабораторній роботі

- •2.4.2 Підготовка до роботи

- •2.4.3 Проведення досліджень

- •2.4.4 Зміст звіту

- •3.3.2 Дешифратори (декодери)

- •3.4 Завдання, порядок виконання роботи і проведення досліджень

- •3.4.1 Підготовка до роботи

- •3.4.2 Проведення досліджень

- •3.4.3 Зміст звіту

- •4.3.1 Rs-тригер з інверсними входами

- •4.3.2 Rs-тригер з прямими входами

- •4.3.3 Тактований rs-тригер з прямими входами

- •4.3.4 Потенційний d-тригер

- •4.3.5 Тригери на мікросхемах середнього ступеня інтеграції

- •4.4 Завдання, порядок виконання роботи і проведення досліджень

- •4.4.1 Підготовка до роботи

- •4.4.2 Проведення досліджень

- •4.4.3 Зміст звіту

- •5.3.2 Синхронні лічильники

- •5.3.3 Кільцевий лічильник

- •5.3.4 Синхронний 4-х розрядний реверсивний двійковий лічильник к155ие7

- •5.4 Завдання, порядок виконання роботи і проведення досліджень

- •5.4.1 Підготовка до роботи

- •5.4.2 Проведення досліджень

- •5.4.3 Зміст звіту

- •6.3.2 Дільник частоти на віднімаючому лічильнику

- •6.3.3 Дільник частоти з роздрібним коефіцієнтом ділення

- •6.4 Завдання, порядок виконання роботи і проведення досліджень

- •6.4.1 Підготовка до роботи

- •6.4.2 Проведення досліджень

- •6.4.3 Зміст звіту

- •Перелік посилань

2.4.4 Зміст звіту

У звіті повинні бути представлені схеми і умовні позначень досліджуваних логічних елементів і таблиць станів, що ілюструють їх роботу, зміряні параметри, висновок про результати досліджень.

3 ЛАБОРАТОРНА РОБОТА № 2 ДОСЛІДЖЕННЯ РОБОТИ КОДУЮЧИХ І ДЕКОДУЮЧИХ ПРИСТРОЇВ

3.1 Мета лабораторної роботи

Вивчення принципів роботи, методів синтезу кодуючих і декодуючих пристроїв, виконаних на основі інтегральних мікросхем, придбання навиків і умінь побудови і перевірки працездатності досліджуваних схем.

3.2 Програма лабораторної роботи

У програму роботи входить дослідження роботи кодуючих і декодуючих пристроїв, виконаних на логічних елементах і у вигляді однієї мікросхеми.

3.3 Теоретичні відомості

Принципи роботи і методи синтезу кодуючих і декодуючих пристроїв (шифраторів і дешифраторів) приведені в книгах [4, 7, 8].

Кодерами (шифраторами) і декодерами (дешифраторами) називаються пристрою для перетворення вхідних кодів у вихідні. Найчастіше використовуються двійкові кодери і декодери.

3.3.1 Шифратори (кодери)

Двійкові шифратори перетворять код «1 з N» в двійковий код. При подачі рівня логічної одиниці на один з N входів кодера на його виходах формується двійковий код, що відображає номер цього входу. (на інших входах шифратора при цьому є рівень логічного нуля). Існують шифратори, у яких на один з входів подається рівень логічного нуля, на решті входів шифратора при цьому підтримується рівень логічної одиниці.

Одне з основних застосувань шифратора - введення даних з клавіатури, при якому натиснення клавіші з десятковою цифрою повинне приводити до передачі в пристрій двійкового коду даної цифри.

Повний шифратор має N входів і n виходів. Причому N=2n.

Розглянемо приклад побудови двійкового шифратора для вхідного коду «1 з 3». Таблиця 3.1 є таблицею істинності такого кодера. У початковому «незбудженому» стані входи F1, F2, F3 знаходяться в стані логічного нуля. При подачі на один з входів рівня логічне одиниці на виходах а0, а1 з'явиться двійковий код відповідний десятковому номеру «збудженого» входу.

Таблиця 3.1 – Таблиця істинності шифратора (кодера)

|

Входи |

Виходи | |||

|

F3 |

F2 |

F1 |

a1 |

a0 |

|

Основні комбінації | ||||

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

Заборонені комбінації | ||||

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

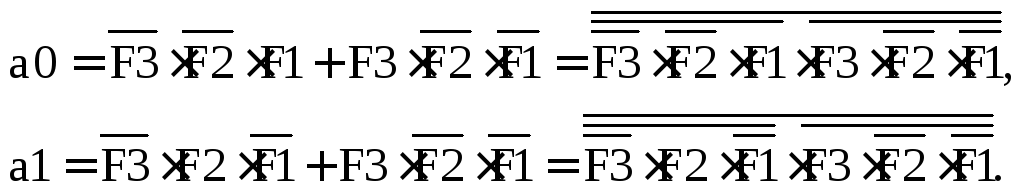

Використовуючи таблицю 3.1 рівнянь кодера можна представити в наступному вигляді:

![]() (3.1)

(3.1)

У базисі «І-НЕ» вирази (3.1) приймають вигляд:

(3.2)

(3.2)

Враховуючи,

що даний кодер має три вхідні сигнали,

його таблиця істинності має в загальному

випадку

![]() рядків.

Як видно з таблиці 3.1 код «1 з 3» (як і

будь-який код «1 з N») є «надмірним» в

сенсі кількості використаних вхідних

розрядів. Комбінації в яких більш за

один вхідний розряд мають значення

«Логічна 1» є для коду «1 з N» забороненими.

рядків.

Як видно з таблиці 3.1 код «1 з 3» (як і

будь-який код «1 з N») є «надмірним» в

сенсі кількості використаних вхідних

розрядів. Комбінації в яких більш за

один вхідний розряд мають значення

«Логічна 1» є для коду «1 з N» забороненими.

Проте, в реальних електронних пристроях такі комбінації можуть зустрічатися. Наприклад, при перетворенні номера натиснутої клавіші в двійковий код, можуть зустрітися ситуації коли одночасно натиснутими виявляються декілька клавіш. При побудові цифрового автомата (шифратора) за виразами (3.1) або (3.2) таким ситуаціям відповідатиме «нульовий» сигнал на обох виходах.

У ситуаціях коли заборонені комбінації на входах шифратора принципово неможливі, вирази, що описують роботу кодера, можуть бути приведені до простішого вигляду:

![]() (3.3)

(3.3)

У виразах (3.3) «нульові» вхідні сигнали не використовуються, оскільки в коді «1 з N» передбачається, що за наявності одного «одиничного» входу усі інші свідомо «нульові».

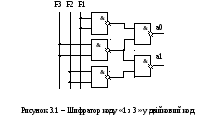

На підставі отриманих виразів (3.3) будується кодер, показаний на рисунку 3.1.

Аналогічно розглянутому вище будуються кодери (шифратори) з будь-якою кількістю входів.