- •Методічні вказівки до лабораторних робіт

- •II-iiIкурсувсіх форм навчання)

- •1 Опис лабораторного стенду та методики його використання

- •2 Лабораторна робота № 1 дослідження роботи логічних елементів та простих комбінаційних схем

- •2.1 Мета лабораторної роботи

- •2.2 Програма лабораторної роботи

- •2.3 Теоретичні відомості

- •2.3.1 Логічне заперечення (інверсія)

- •2.3.2 Логічне множення (кон'юнкція)

- •2.3.3 Логічне складання (диз'юнкція)

- •2.3.4 Аксіоми і закони булевої алгебри

- •2.3.5 Базові електронні елементи

- •2.3.6 Функція «сума по модулю 2»

- •2.3.7 Побудова логічних функцій трьох і більше аргументів

- •2.3.8 Оптимізація логічних функцій. Карти Карно

- •2.4 Завдання, порядок виконання роботи і проведення досліджень

- •2.4.1 Особливості використання лабораторного стенду в даній лабораторній роботі

- •2.4.2 Підготовка до роботи

- •2.4.3 Проведення досліджень

- •2.4.4 Зміст звіту

- •3.3.2 Дешифратори (декодери)

- •3.4 Завдання, порядок виконання роботи і проведення досліджень

- •3.4.1 Підготовка до роботи

- •3.4.2 Проведення досліджень

- •3.4.3 Зміст звіту

- •4.3.1 Rs-тригер з інверсними входами

- •4.3.2 Rs-тригер з прямими входами

- •4.3.3 Тактований rs-тригер з прямими входами

- •4.3.4 Потенційний d-тригер

- •4.3.5 Тригери на мікросхемах середнього ступеня інтеграції

- •4.4 Завдання, порядок виконання роботи і проведення досліджень

- •4.4.1 Підготовка до роботи

- •4.4.2 Проведення досліджень

- •4.4.3 Зміст звіту

- •5.3.2 Синхронні лічильники

- •5.3.3 Кільцевий лічильник

- •5.3.4 Синхронний 4-х розрядний реверсивний двійковий лічильник к155ие7

- •5.4 Завдання, порядок виконання роботи і проведення досліджень

- •5.4.1 Підготовка до роботи

- •5.4.2 Проведення досліджень

- •5.4.3 Зміст звіту

- •6.3.2 Дільник частоти на віднімаючому лічильнику

- •6.3.3 Дільник частоти з роздрібним коефіцієнтом ділення

- •6.4 Завдання, порядок виконання роботи і проведення досліджень

- •6.4.1 Підготовка до роботи

- •6.4.2 Проведення досліджень

- •6.4.3 Зміст звіту

- •Перелік посилань

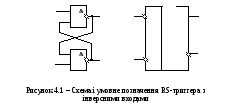

4.3.1 Rs-тригер з інверсними входами

На рисунку 4.1 зображений RS-триггер з інверсними входами.

Початковому стану входів тригера в режимі зберігання інформації відповідають рівні логічної одиниці. Для перемикання тригера в одиничний стан необхідно короткочасно з'єднати вхід S тригера з нульовою шиною стенду. При цьому вхід R тригера повинен мати потенціал логічної одиниці. Для перемикання тригера в нульовий стан необхідно короткочасно з'єднати вхід R з нульовою шиною стенду. При цьому вхід S тригера повинен мати потенціал логічної одиниці.

Стан, при якому на обидва входи такого тригера подається рівень логічного нуля є забороненим. При такій комбінації входів на обох виходах тригера з'явиться рівень логічної одиниці (виходи перестають бути взаємно інверсними).

Таблиця 4.1 є таблицею станів тригера з інверсними входами.

Таблиця 4.1 – Таблиця станів RS-триггера з інверсними входами

|

Вхідні аргументи |

Виходи | ||||

|

S |

R |

|

|

|

|

|

0 |

0 |

X |

X |

З |

З |

|

0 |

1 |

Х |

Х |

1 |

0 |

|

1 |

0 |

Х |

Х |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

Примітка: Х – будь-який стан (логічний 0 або логічна 1); З – заборонений стан.

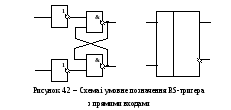

4.3.2 Rs-тригер з прямими входами

На рисунку 4.2 зображений RS-триггер з прямими входами. Стан входів в режимі зберігання - рівні логічного нуля. Керуючі інформаційні сигнали повинні мати рівень логічної одиниці. В основному робота даного тригера подібна до роботи RS-триггера з інверсними входами.

Таблиця 4.2 є таблицею станів тригера з прямими входами.

Таблиця 4.2 – Таблиця станів RS-триггера з прямими входами

|

Вхідні аргументи |

Виходи | ||||

|

S |

R |

|

|

|

|

|

1 |

1 |

X |

X |

З |

З |

|

0 |

1 |

Х |

Х |

0 |

1 |

|

1 |

0 |

Х |

Х |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

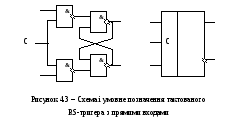

4.3.3 Тактований rs-тригер з прямими входами

На рисунку 4.3 зображена схема тактованого RS-триггера з прямими входами. Інформація в такий тригер заноситься шляхом подачі рівнів логічної одиниці на один з входів S або R і подальшого перемикання сигналу на тактуючому вході С в «одиницю». Іншими словами, занесення інформації в тригер відбувається синхронно з сигналом на тактуючому вході, тому такі тригери ще називають синхронними. При рівні логічного нуля на вході С тригер зберігає попередню інформацію і стан входів S і R на його роботу не впливає.

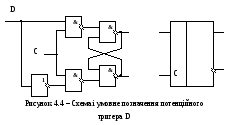

4.3.4 Потенційний d-тригер

На рисунку 4.4 зображена схема потенційного D-тригера. Інформація, подана на вхід D (логічний нуль або логічна одиниця), буде записана в тригер після подачі рівня (потенціалу) логічної одиниці на вхід С.