- •Методічні вказівки до лабораторних робіт

- •II-iiIкурсувсіх форм навчання)

- •1 Опис лабораторного стенду та методики його використання

- •2 Лабораторна робота № 1 дослідження роботи логічних елементів та простих комбінаційних схем

- •2.1 Мета лабораторної роботи

- •2.2 Програма лабораторної роботи

- •2.3 Теоретичні відомості

- •2.3.1 Логічне заперечення (інверсія)

- •2.3.2 Логічне множення (кон'юнкція)

- •2.3.3 Логічне складання (диз'юнкція)

- •2.3.4 Аксіоми і закони булевої алгебри

- •2.3.5 Базові електронні елементи

- •2.3.6 Функція «сума по модулю 2»

- •2.3.7 Побудова логічних функцій трьох і більше аргументів

- •2.3.8 Оптимізація логічних функцій. Карти Карно

- •2.4 Завдання, порядок виконання роботи і проведення досліджень

- •2.4.1 Особливості використання лабораторного стенду в даній лабораторній роботі

- •2.4.2 Підготовка до роботи

- •2.4.3 Проведення досліджень

- •2.4.4 Зміст звіту

- •3.3.2 Дешифратори (декодери)

- •3.4 Завдання, порядок виконання роботи і проведення досліджень

- •3.4.1 Підготовка до роботи

- •3.4.2 Проведення досліджень

- •3.4.3 Зміст звіту

- •4.3.1 Rs-тригер з інверсними входами

- •4.3.2 Rs-тригер з прямими входами

- •4.3.3 Тактований rs-тригер з прямими входами

- •4.3.4 Потенційний d-тригер

- •4.3.5 Тригери на мікросхемах середнього ступеня інтеграції

- •4.4 Завдання, порядок виконання роботи і проведення досліджень

- •4.4.1 Підготовка до роботи

- •4.4.2 Проведення досліджень

- •4.4.3 Зміст звіту

- •5.3.2 Синхронні лічильники

- •5.3.3 Кільцевий лічильник

- •5.3.4 Синхронний 4-х розрядний реверсивний двійковий лічильник к155ие7

- •5.4 Завдання, порядок виконання роботи і проведення досліджень

- •5.4.1 Підготовка до роботи

- •5.4.2 Проведення досліджень

- •5.4.3 Зміст звіту

- •6.3.2 Дільник частоти на віднімаючому лічильнику

- •6.3.3 Дільник частоти з роздрібним коефіцієнтом ділення

- •6.4 Завдання, порядок виконання роботи і проведення досліджень

- •6.4.1 Підготовка до роботи

- •6.4.2 Проведення досліджень

- •6.4.3 Зміст звіту

- •Перелік посилань

6.3.2 Дільник частоти на віднімаючому лічильнику

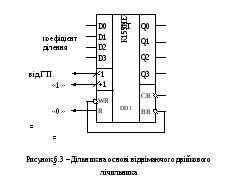

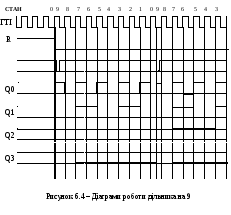

На рисунках 6.3, 6.4 зображена схема і часові діаграми роботи дільника частоти із заданим коефіцієнтом перерахунку, який заснованонабазівіднімаючого лічильника, що має режим паралельного занесення. Діаграми відповідають коефіціентові ділення 9.

Даний дільник імпульсів працює наступним чином. На входи D0÷D3 мікросхеми DD 1 подається двійковий код десяткового числа, рівного коефіцієнту ділення. При подачі на віднімаючий вхід лічильника послідовності імпульсів від ГТІабо ГОІвміст лічильника зменшується і після вступу на вхід лічильника кількості імпульсів, рівної коефіцієнту ділення, лічильник обнуляється. На його виходізворотного перенесення BR виникає перепад з 1 в 0. Цей перепад поступає на вхід дозволу паралельного запису WR і в лічильник знову заноситься двійкове число, рівне коефіцієнту ділення. Після цього лічильник знову переводиться в режим віднімання і цикл роботи повторюється.

Виходом дільника є вихід зворотного перенесення ВR.

На рисунку6.5 представлена схема і часові діаграми

дільника частоти з коефіцієнтом

перерахунку![]() ,

де N - будь-яке число від 1 до 16.

,

де N - будь-яке число від 1 до 16.

Схема

є двоступінчатим дільником. Перший

ступінь дільника утворений на основі

мікросхеми DD 1 з коефіцієнтом

ділення ![]() ,

другий ступінь дільника є тригерним

дворозрядним лічильником-дільником на

3. При необхідності збільшення коефіцієнта

ділення розрядність двійкового лічильника

необхідно збільшити. Самостійно зобразіть

часові діаграми роботи даної схеми при

N, що

відповідає таблиці 6.1.

,

другий ступінь дільника є тригерним

дворозрядним лічильником-дільником на

3. При необхідності збільшення коефіцієнта

ділення розрядність двійкового лічильника

необхідно збільшити. Самостійно зобразіть

часові діаграми роботи даної схеми при

N, що

відповідає таблиці 6.1.

Таблиця 6.1 – Коефіцієнти N згідно з варіантами

|

Номер бригади |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

|

N |

2 |

3 |

5 |

7 |

8 |

11 |

13 |

12 |

14 |

15 |

4 |

6.3.3 Дільник частоти з роздрібним коефіцієнтом ділення

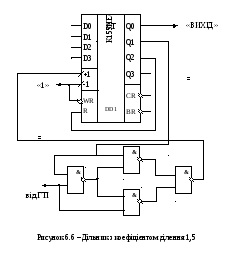

На рисунку 6.6представлена схема дільника частоти з коефіцієнтом ділення 1,5. Схема містить двійковий лічильник DD 1 і суматор по модулю 2, виконаний на логічних елементах 2И-НЕ. На рахунковий вхід "+1" лічильника поступає вихідний сигнал схеми суматора по модулю 2, а на входи схеми суматора - тактовий сигнал і вихідний сигнал з другого розряду лічильника. Якщо на виході другого розряду лічильника встановлюється рівень логічного 0, то сигнал на виході суматора повторює вхідний тактовий сигнал з урахуванням деякої часової затримки. Якщо ж на виході другого розряду встановлюється рівень логічною 1, то тактовий сигнал на виході суматора інвертується. Це призводить до збільшення кількості переходів з 1 в 0 і з 0 в 1 на виході схеми суматора і викликає додаткові перемикання лічильника DD 1. У результаті на виході"1" лічильника частота сигналу менше вхідної частоти не в 2, а в 1,5 рази, а на виході "2" - в три рази.

6.4 Завдання, порядок виконання роботи і проведення досліджень

6.4.1 Підготовка до роботи

6.4.1.1 Вивчити принципи побудови і роботу цифрових дільників частоти на інтегральних схемах (дільники частоти на основі лічильників, що підсумовують або віднімають, багатоступінчасті дільники частоти, дільники частоти на основі лічильників з підвищеною розрядністю та ін.)

Вивчити паспортні дані, характеристики і основні режими роботи мікросхем, що становлять схеми дільників частоти.

6.4.1.2 Самостійно розробіть та зобразіть часові діаграми роботи для схеми, яку зображено на рисунку 6.5, при N, що відповідає таблиці 6.1.

6.4.1.3 Самостійно розробіть та зобразіть часові діаграми роботи для схеми, яку зображено на рисунку 6.6.