- •А.Д. Чередов организация эвм и систем

- •Введение

- •Архитектуры, характеристики, классификация эвм

- •1.1. Однопроцессорные архитектуры эвм

- •Название фирм и разработанных ими risc-процессоров

- •Максимальное и среднее число команд, выполняемых в одном машинном цикле

- •1.2. Технические и эксплуатационные характеристики эвм

- •Результаты тестирования процессоров

- •1.3. Классификация эвм

- •1.3.1. Классификация эвм по назначению

- •1.3.2. Классификация эвм по функциональным возможностям и размерам

- •Сравнительные параметры различных классов эвм

- •Функциональная и структурная организация эвм

- •2.1. Связь между функциональной и структурной организацией эвм

- •2.2. Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •2.3. Структура и форматы команд эвм

- •Способ расширения кодов операции

- •2.4. Способы адресации информации в эвм

- •Классификация способов адресации по наличию адресной информации в команде Явная и неявная адресация

- •Классификация способов адресации по кратности обращения в память

- •Непосредственная адресация операнда

- •Прямая адресация операндов

- •Косвенная адресация операндов

- •Классификация способов формирования исполнительных адресов ячеек памяти

- •Относительная адресация ячейки оп Базирование способом суммирования

- •Относительная адресация с совмещением составляющих аи

- •Индексная адресация

- •Стековая адресация

- •2.5. Примеры форматов команд и способов адресации

- •2.5.1. Форматы команд и способы адресации в cisc-процессорах

- •Развитие системы команд процессоров архитектуры Intel

- •Общий формат команд

- •Способы адресации

- •2.5.2. Форматы команд и способы адресации в risc-процессорах

- •2.6. Типы данных

- •Данные со знаком

- •3. Функциональная и структурная организация центрального процессора эвм

- •3.1. Назначение и структура центрального процессора

- •3.2. Регистровые структуры центрального процессора

- •4. Регистры отладки и тестирования.

- •3.2.1. Основные функциональные регистры

- •Регистры общего назначения

- •Регистры сегментов и дескрипторы сегментов

- •Указатель команд

- •Регистр флагов

- •3.2.2. Регистры процессора обработки чисел с плавающей точкой

- •3.2.3. Системные регистры

- •3.2.4. Регистры отладки и тестирования

- •3.3. Назначение, классификация и организация цуу

- •3.3.1. Центральное устройство управления микропрограммного типа

- •3.3.2. Процедура выполнения команд

- •3.3.3. Принципы организации системы прерывания программ

- •Характеристики системы прерывания

- •Программно–управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •3.4. Назначение, классификация и организация алу

- •Классификация алу

- •Обобщенная структурная схема алу

- •Методы повышения быстродействия алу

- •4. Принципы организации подсистемы памяти эвм и вс

- •4.1. Иерархическая структура памяти эвм

- •4.2. Организация внутренней памяти процессора

- •4.3. Способы организации кэш-памяти

- •4.3.1. Общие сведения

- •Типовая структура кэш-памяти

- •4.3.2. Способы размещения данных в кэш-памяти

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •Распределение секторов

- •4.3.3. Методы обновления строк основной памяти

- •Условия сохранения и обновления информации

- •Сквозная запись

- •Обратная запись

- •4.3.4. Методы замещения строк кэш-памяти

- •4.4. Принципы организации оперативной памяти

- •4.4.1. Общие положения

- •4.4.2. Методы управления памятью

- •Типы адресов

- •Распределение памяти фиксированными разделами

- •Распределение памяти разделами переменной величины

- •Перемещаемые разделы

- •4.4.3. Организация виртуальной памяти

- •Страничное распределение

- •Сегментное распределение

- •Странично-сегментное распределение

- •Свопинг

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •Выборка широким словом

- •Расслоение обращений

- •4.4.5. Методы защиты памяти

- •Защита памяти по граничным адресам

- •Защита памяти по маскам

- •Защита памяти по ключам

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •5. Принципы организации подсистемы ввода-вывода

- •5.1. Проблемы организации подсистем ввода-вывода

- •5.2. Способы организации передачи данных

- •Прямой доступ к памяти

- •5.3. Унификация средств обмена и интерфейсы эвм

- •5.3.1. Общая характеристика и классификация интерфейсов

- •5.3.2. Типы и характеристики стандартных шин

- •Характеристики стандартных шин

- •5.4. Современные и перспективные структуры подсистем ввода-вывода

- •6. Многопроцессорные и многомашинные вычислительные системы

- •6.1. Архитектуры вычислительных систем

- •6.2. Сильно связанные многопроцессорные системы

- •6.3. Слабосвязанные многопроцессорные системы

- •Список использованной литератуРы

- •Оглавление

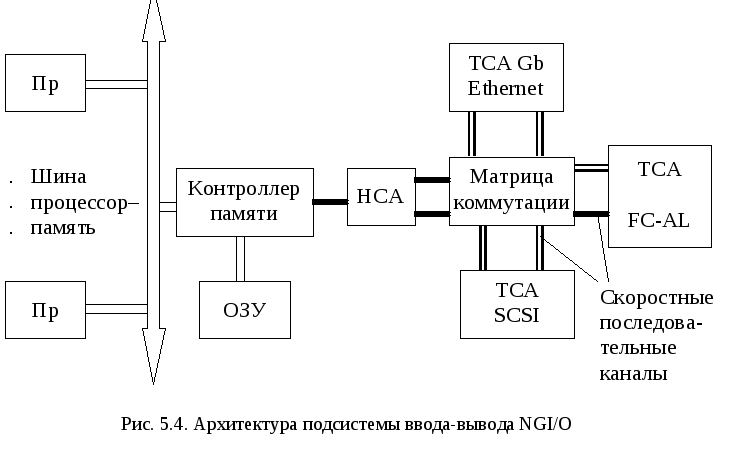

5.4. Современные и перспективные структуры подсистем ввода-вывода

Учитывая дальнейший рост производительности микропроцессоров, а также недостатки и ограничения топологии "общая шина", осенью 1998 г. корпорация Intel обнародовала принципиально иную архитектуру, которую скромно адресовала следующему поколению подсистем ввода-вывода — Next Generation I/O (NGI/O). Собственно, это было ответом на спецификацию PCI-X.

Основными чертами новой архитектуры являются последовательный обмен данными, канальная технология ввода-вывода и матричная топология. Таким образом, в интеловской архитектуре компьютеров появляются каналы ввода-вывода, которые были на время забыты (хотя до сих пор используются в мэйнфреймах). Базовый микропроцессор не будет сам заниматься рутинной работой по обмену данными с ПУ, а станет только инициировать прием или передачу, давая соответствующие указания процессору (контроллеру) канала. Немаловажно и то, что ПУ будут иметь доступ к ОП исключительно через контроллер канала.

Топология матричной коммутации, заложенная в NGI/O, позволяет взаимодействовать всем устройствам, входящим в матрицу, по принципу "каждый с каждым". Ее задачей является распределение данных по каналам. Ключи матрицы временно образуют коммутационный канал между компьютером и ПУ, организуя обмен "точка-точка".

Благодаря этой технологии исключается проблема арбитража и конфликтов, "горячая" замена устройств становится действительно автоматической, существенно облегчается конфигурирование контроллеров (причем общая производительность не ухудшается из-за неправильного конфигурирования одного из них), расстояние между периферийным контроллером и контроллером памяти может быть увеличено до 30 м. Стоит также отметить, что трудностей с расширением при использовании этой топологии практически не существует. По некоторым данным с помощью NGI/O к системе (серверу) можно подключить до 64 тыс. устройств.

В качестве интерфейса контроллера памяти сервера (рис. 5.4) служит главный канальный адаптер НСА (Host Channel Adapter). Он содержит процессор прямого доступа к памяти (DMA). Для связи между матрицей коммутации и контроллерами ввода-вывода ПУ предназначены объектные канальные адаптеры ТСА (Target Channel Adapter). Канальный адаптер может подключаться к другому адаптеру или ключу. Эти ключи и образуют матрицу коммутации.

Скорость передачи для одного канала NGI/O оценивается на уровне 1,25 - 2,5 Гбит/с, однако при увеличении числа каналов до четырех она соответственно возрастет до 10 Гбит/с.

Сразу после объявления NGI/O по инициативе корпорации IBM был создан альянс для разработки открытого стандарта на архитектуру под названием Future I/O. Уже известно, что для данной архитектуры, как и для NGI/O планируется использовать матричную топологию, позволяющую получить соединение типа "точка-точка". Правда в отличие от NGI/O в спецификации Future I/O допускается применение PCI-адаптеров. Сделано это для того, чтобы продлить жизнь своему детищу – PCI-X. Максимальная производительность одного соединения может достигать 2 Гб/с по медному кабелю на расстоянии 5 - 10 м, а по оптоволоконному – до 300 м.

В начале 2000 г. спецификация должна быть утверждена, а первые результаты применения новой технологии могут быть получены не ранее 2001 г.