- •А.Д. Чередов организация эвм и систем

- •Введение

- •Архитектуры, характеристики, классификация эвм

- •1.1. Однопроцессорные архитектуры эвм

- •Название фирм и разработанных ими risc-процессоров

- •Максимальное и среднее число команд, выполняемых в одном машинном цикле

- •1.2. Технические и эксплуатационные характеристики эвм

- •Результаты тестирования процессоров

- •1.3. Классификация эвм

- •1.3.1. Классификация эвм по назначению

- •1.3.2. Классификация эвм по функциональным возможностям и размерам

- •Сравнительные параметры различных классов эвм

- •Функциональная и структурная организация эвм

- •2.1. Связь между функциональной и структурной организацией эвм

- •2.2. Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •2.3. Структура и форматы команд эвм

- •Способ расширения кодов операции

- •2.4. Способы адресации информации в эвм

- •Классификация способов адресации по наличию адресной информации в команде Явная и неявная адресация

- •Классификация способов адресации по кратности обращения в память

- •Непосредственная адресация операнда

- •Прямая адресация операндов

- •Косвенная адресация операндов

- •Классификация способов формирования исполнительных адресов ячеек памяти

- •Относительная адресация ячейки оп Базирование способом суммирования

- •Относительная адресация с совмещением составляющих аи

- •Индексная адресация

- •Стековая адресация

- •2.5. Примеры форматов команд и способов адресации

- •2.5.1. Форматы команд и способы адресации в cisc-процессорах

- •Развитие системы команд процессоров архитектуры Intel

- •Общий формат команд

- •Способы адресации

- •2.5.2. Форматы команд и способы адресации в risc-процессорах

- •2.6. Типы данных

- •Данные со знаком

- •3. Функциональная и структурная организация центрального процессора эвм

- •3.1. Назначение и структура центрального процессора

- •3.2. Регистровые структуры центрального процессора

- •4. Регистры отладки и тестирования.

- •3.2.1. Основные функциональные регистры

- •Регистры общего назначения

- •Регистры сегментов и дескрипторы сегментов

- •Указатель команд

- •Регистр флагов

- •3.2.2. Регистры процессора обработки чисел с плавающей точкой

- •3.2.3. Системные регистры

- •3.2.4. Регистры отладки и тестирования

- •3.3. Назначение, классификация и организация цуу

- •3.3.1. Центральное устройство управления микропрограммного типа

- •3.3.2. Процедура выполнения команд

- •3.3.3. Принципы организации системы прерывания программ

- •Характеристики системы прерывания

- •Программно–управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •3.4. Назначение, классификация и организация алу

- •Классификация алу

- •Обобщенная структурная схема алу

- •Методы повышения быстродействия алу

- •4. Принципы организации подсистемы памяти эвм и вс

- •4.1. Иерархическая структура памяти эвм

- •4.2. Организация внутренней памяти процессора

- •4.3. Способы организации кэш-памяти

- •4.3.1. Общие сведения

- •Типовая структура кэш-памяти

- •4.3.2. Способы размещения данных в кэш-памяти

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •Распределение секторов

- •4.3.3. Методы обновления строк основной памяти

- •Условия сохранения и обновления информации

- •Сквозная запись

- •Обратная запись

- •4.3.4. Методы замещения строк кэш-памяти

- •4.4. Принципы организации оперативной памяти

- •4.4.1. Общие положения

- •4.4.2. Методы управления памятью

- •Типы адресов

- •Распределение памяти фиксированными разделами

- •Распределение памяти разделами переменной величины

- •Перемещаемые разделы

- •4.4.3. Организация виртуальной памяти

- •Страничное распределение

- •Сегментное распределение

- •Странично-сегментное распределение

- •Свопинг

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •Выборка широким словом

- •Расслоение обращений

- •4.4.5. Методы защиты памяти

- •Защита памяти по граничным адресам

- •Защита памяти по маскам

- •Защита памяти по ключам

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •5. Принципы организации подсистемы ввода-вывода

- •5.1. Проблемы организации подсистем ввода-вывода

- •5.2. Способы организации передачи данных

- •Прямой доступ к памяти

- •5.3. Унификация средств обмена и интерфейсы эвм

- •5.3.1. Общая характеристика и классификация интерфейсов

- •5.3.2. Типы и характеристики стандартных шин

- •Характеристики стандартных шин

- •5.4. Современные и перспективные структуры подсистем ввода-вывода

- •6. Многопроцессорные и многомашинные вычислительные системы

- •6.1. Архитектуры вычислительных систем

- •6.2. Сильно связанные многопроцессорные системы

- •6.3. Слабосвязанные многопроцессорные системы

- •Список использованной литератуРы

- •Оглавление

5.3. Унификация средств обмена и интерфейсы эвм

5.3.1. Общая характеристика и классификация интерфейсов

Объединение отдельных подсистем (устройств, модулей) ЭВМ в единую систему основывается на многоуровневом принципе с унифицированным сопряжением между всеми уровнями — стандартным интерфейсом. Под стандартными интерфейсами понимают такие интерфейсы, которые приняты и рекомендованы в качестве обязательных отраслевыми или государственными стандартами, различными международными комиссиями, а также крупными зарубежными фирмами.

Интерфейсы характеризуются следующими параметрами:

пропускной способностью интерфейса — количеством информации, которая может быть передана через интерфейс в единицу времени;

максимальной частотой передачи информационных сигналов через интерфейс;

информационной шириной интерфейса — числом бит или байт данных, передаваемых параллельно через интерфейс;

максимально допустимым расстоянием между соединяемыми устройствами;

динамическими параметрами интерфейса — временем передачи отдельного слова или блока данных с учетом продолжительности процедур подготовки и завершения передачи;

общим числом проводов (линий) в интерфейсе.

В настоящее время не существует однозначной классификации интерфейсов. Можно выделить следующие четыре классификационных признака интерфейсов:

способ соединения компонентов системы (радиальный, магистральный, смешанный);

способ передачи информации (параллельный, последовательный, параллельно-последовательный);

принцип обмена информацией (асинхронный, синхронный);

режим передачи информации (двусторонняя поочередная передача, односторонняя передача).

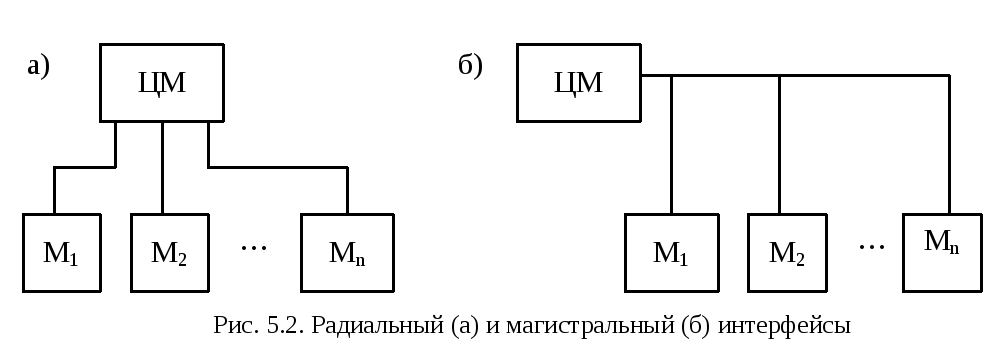

На рис. 5.2 представлены радиальный и магистральный интерфейсы, соединяющие центральный модуль (ЦМ) и другие модули (компоненты) системы (М1, . . . , Мn).

Радиальный интерфейс позволяет всем модулям (М1, . . . , Мn) работать независимо, но имеет максимальное количество шин. Магистральный интерфейс (общая шина) использует принцип разделения времени для связи между ЦМ и другими модулями. Он сравнительно прост в реализации, но лимитирует скорость обмена.

Параллельные интерфейсы позволяют передавать одновременно определенное количество бит или байт информации по многопроводной линии. Последовательные интерфейсы служат для последовательной передачи по двухпроводной линии.

В случае синхронного интерфейса моменты выдачи информации передающим устройством и приема ее в другом устройстве должны синхронизироваться, для этого используют специальную линию синхронизации. При асинхронном интерфейсе передача осуществляется по принципу "запрос-ответ". Каждый цикл передачи сопровождается последовательностью управляющих сигналов, которые вырабатываются передающим и приемным устройствами. Передающее устройство может осуществлять передачу данных (байта или нескольких байтов) только после подтверждения приемником своей готовности к приему данных.

Классификация интерфейсов по назначению отражает взаимосвязь с архитектурой реальных средств вычислительной техники. В соответствии с этим признаком в ЭВМ и вычислительных системах можно выделить несколько уровней сопряжений:

машинные системные интерфейсы;

локальные шины;

интерфейсы периферийных устройств (малые интерфейсы);

межмашинные интерфейсы.

Машинные (внутримашинные) системные интерфейсы предназначены для организации связей между составными компонентами ЭВМ на уровне обмена информацией с центральным процессором, ОП и контроллерами (адаптерами) ПУ.

Локальной шиной называется шина, электрически выходящая непосредственно на контакты микропроцессора, и предназначенная для увеличения быстродействия видеоадаптеров и контроллеров дисковых накопителей. Она обычно объединяет процессор, память, схемы буферизации для системной шины и ее контроллер, а также некоторые вспомогательные схемы. Типичными примерами локальных шин являются VLB и PCI.

Назначение интерфейсов периферийных устройств (малых интерфейсов) состоит в выполнении функций сопряжения контроллера (адаптера) с конкретным механизмом ПУ.

Межмашинные интерфейсы используются в вычислительных системах и сетях.

С целью снижения стоимости некоторые компьютеры имеют единственную шину (общая шина) для памяти и устройств ввода-вывода. Персональные компьютеры первых поколений, как правило, строились на основе одной системной шины в стандартах ISA, EISA или MCA. Необходимость сохранения баланса производительности по мере роста быстродействия микропроцессоров привела к многоуровневой организации шин на основе использования нескольких системных и локальных шин. В современных компьютерах шины интерфейсов делят на шины, обеспечивающие организацию связи процессора с памятью, и шины ввода-вывода. Шины процессор-память сравнительно короткие, обычно высокоскоростные и соответствуют организации подсистемы памяти для обеспечения максимальной пропускной способности канала память-процессор. Шины ввода-вывода могут иметь большую протяженность, поддерживать подсоединение многих типов устройств и обычно следуют одному из шинных стандартов. Обычно количество и типы устройств ввода-вывода в вычислительных системах не фиксируются, что дает возможность пользователю самому подобрать необходимую конфигурацию. Шина ввода-вывода компьютера рассматривается как шина расширения, обеспечивающая постепенное наращивание устройств ввода-вывода. Поэтому стандарты играют огромную роль, позволяя разработчикам компьютеров и устройств ввода-вывода работать независимо.