- •А.Д. Чередов организация эвм и систем

- •Введение

- •Архитектуры, характеристики, классификация эвм

- •1.1. Однопроцессорные архитектуры эвм

- •Название фирм и разработанных ими risc-процессоров

- •Максимальное и среднее число команд, выполняемых в одном машинном цикле

- •1.2. Технические и эксплуатационные характеристики эвм

- •Результаты тестирования процессоров

- •1.3. Классификация эвм

- •1.3.1. Классификация эвм по назначению

- •1.3.2. Классификация эвм по функциональным возможностям и размерам

- •Сравнительные параметры различных классов эвм

- •Функциональная и структурная организация эвм

- •2.1. Связь между функциональной и структурной организацией эвм

- •2.2. Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •2.3. Структура и форматы команд эвм

- •Способ расширения кодов операции

- •2.4. Способы адресации информации в эвм

- •Классификация способов адресации по наличию адресной информации в команде Явная и неявная адресация

- •Классификация способов адресации по кратности обращения в память

- •Непосредственная адресация операнда

- •Прямая адресация операндов

- •Косвенная адресация операндов

- •Классификация способов формирования исполнительных адресов ячеек памяти

- •Относительная адресация ячейки оп Базирование способом суммирования

- •Относительная адресация с совмещением составляющих аи

- •Индексная адресация

- •Стековая адресация

- •2.5. Примеры форматов команд и способов адресации

- •2.5.1. Форматы команд и способы адресации в cisc-процессорах

- •Развитие системы команд процессоров архитектуры Intel

- •Общий формат команд

- •Способы адресации

- •2.5.2. Форматы команд и способы адресации в risc-процессорах

- •2.6. Типы данных

- •Данные со знаком

- •3. Функциональная и структурная организация центрального процессора эвм

- •3.1. Назначение и структура центрального процессора

- •3.2. Регистровые структуры центрального процессора

- •4. Регистры отладки и тестирования.

- •3.2.1. Основные функциональные регистры

- •Регистры общего назначения

- •Регистры сегментов и дескрипторы сегментов

- •Указатель команд

- •Регистр флагов

- •3.2.2. Регистры процессора обработки чисел с плавающей точкой

- •3.2.3. Системные регистры

- •3.2.4. Регистры отладки и тестирования

- •3.3. Назначение, классификация и организация цуу

- •3.3.1. Центральное устройство управления микропрограммного типа

- •3.3.2. Процедура выполнения команд

- •3.3.3. Принципы организации системы прерывания программ

- •Характеристики системы прерывания

- •Программно–управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •3.4. Назначение, классификация и организация алу

- •Классификация алу

- •Обобщенная структурная схема алу

- •Методы повышения быстродействия алу

- •4. Принципы организации подсистемы памяти эвм и вс

- •4.1. Иерархическая структура памяти эвм

- •4.2. Организация внутренней памяти процессора

- •4.3. Способы организации кэш-памяти

- •4.3.1. Общие сведения

- •Типовая структура кэш-памяти

- •4.3.2. Способы размещения данных в кэш-памяти

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •Распределение секторов

- •4.3.3. Методы обновления строк основной памяти

- •Условия сохранения и обновления информации

- •Сквозная запись

- •Обратная запись

- •4.3.4. Методы замещения строк кэш-памяти

- •4.4. Принципы организации оперативной памяти

- •4.4.1. Общие положения

- •4.4.2. Методы управления памятью

- •Типы адресов

- •Распределение памяти фиксированными разделами

- •Распределение памяти разделами переменной величины

- •Перемещаемые разделы

- •4.4.3. Организация виртуальной памяти

- •Страничное распределение

- •Сегментное распределение

- •Странично-сегментное распределение

- •Свопинг

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •Выборка широким словом

- •Расслоение обращений

- •4.4.5. Методы защиты памяти

- •Защита памяти по граничным адресам

- •Защита памяти по маскам

- •Защита памяти по ключам

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •5. Принципы организации подсистемы ввода-вывода

- •5.1. Проблемы организации подсистем ввода-вывода

- •5.2. Способы организации передачи данных

- •Прямой доступ к памяти

- •5.3. Унификация средств обмена и интерфейсы эвм

- •5.3.1. Общая характеристика и классификация интерфейсов

- •5.3.2. Типы и характеристики стандартных шин

- •Характеристики стандартных шин

- •5.4. Современные и перспективные структуры подсистем ввода-вывода

- •6. Многопроцессорные и многомашинные вычислительные системы

- •6.1. Архитектуры вычислительных систем

- •6.2. Сильно связанные многопроцессорные системы

- •6.3. Слабосвязанные многопроцессорные системы

- •Список использованной литератуРы

- •Оглавление

Сегментное распределение

При страничной организации виртуальное адресное пространство процесса делится механически на равные части. Это не позволяет дифференцировать способы доступа к разным частям программы (сегментам), а это свойство часто бывает очень полезным. Например, можно запретить обращаться с операциями записи и чтения в кодовый сегмент программы, а для сегмента данных разрешить только чтение. Кроме того, разбиение программы на «осмысленные» части делает принципиально возможным разделение одного сегмента несколькими процессами. Например, если два процесса используют одну и ту же математическую подпрограмму, то в оперативную память может быть загружена только одна копия этой подпрограммы.

Рассмотрим, каким образом сегментное распределение памяти реализует эти возможности (рис. 4.16). Виртуальное адресное пространство процесса делится на сегменты, размер которых определяется программистом с учетом смыслового значения содержащейся в них информации. Отдельный сегмент может представлять собой подпрограмму, массив данных и т.п. Иногда сегментация программы выполняется по умолчанию компилятором.

При загрузке процесса часть сегментов помещается в оперативную память (при этом для каждого из этих сегментов операционная система подыскивает подходящий участок свободной памяти), а часть сегментов размещается в дисковой памяти. Сегменты одной программы могут занимать в оперативной памяти несмежные участки. Во время загрузки система создает таблицу сегментов процесса (аналогичную таблице страниц), в которой для каждого сегмента указывается начальный физический адрес сегмента в оперативной памяти, размер сегмента, правила доступа, признак модификации, признак обращения к данному сегменту за последний интервал времени и некоторая другая информация. Если виртуальные адресные пространства нескольких процессов включают один и тот же сегмент, то в таблицах сегментов этих процессов делаются ссылки на один и тот же участок оперативной памяти, в который данный сегмент загружается в единственном экземпляре.

Система с сегментной организацией функционирует аналогично системе со страничной организацией: время от времени происходят прерывания, связанные с отсутствием нужных сегментов в памяти, при необходимости освобождения памяти некоторые сегменты выгружаются, при каждом обращении к оперативной памяти выполняется преобразование виртуального адреса в физический. Кроме того, при обращении к памяти проверяется, разрешен ли доступ требуемого типа к данному сегменту.

Виртуальный адрес при сегментной организации памяти может быть представлен парой (g, s), где g — номер сегмента, а s — смещение в сегменте. Физический адрес получается путем сложения начального физического адреса сегмента, найденного в таблице сегментов по номеру g, и смещения s.

Недостатком данного метода распределения памяти является фрагментация на уровне сегментов и более медленное по сравнению со страничной организацией преобразование адреса.

Странично-сегментное распределение

Как видно из названия, данный метод представляет собой комбинацию страничного и сегментного распределения памяти и, вследствие этого, сочетает в себе достоинства обоих подходов. Виртуальное пространство процесса делится на сегменты, а каждый сегмент в свою очередь делится на виртуальные страницы, которые нумеруются в пределах сегмента. Оперативная память делится на физические страницы. Загрузка процесса выполняется операционной системой постранично, при этом часть страниц размещается в оперативной памяти, а часть на диске. Для каждого сегмента создается своя таблица страниц, структура которой полностью совпадает со структурой таблицы страниц, используемой при страничном распределении.

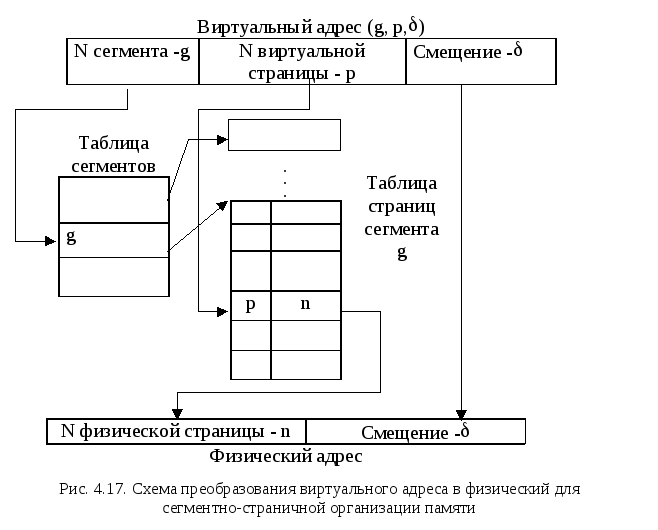

Для каждого процесса создается таблица сегментов, в которой указываются адреса таблиц страниц для всех сегментов данного процесса. Адрес таблицы сегментов загружается в специальный регистр процессора, когда активизируется соответствующий процесс. На рис. 4.17 показана схема преобразования виртуального адреса в физический для данного метода.

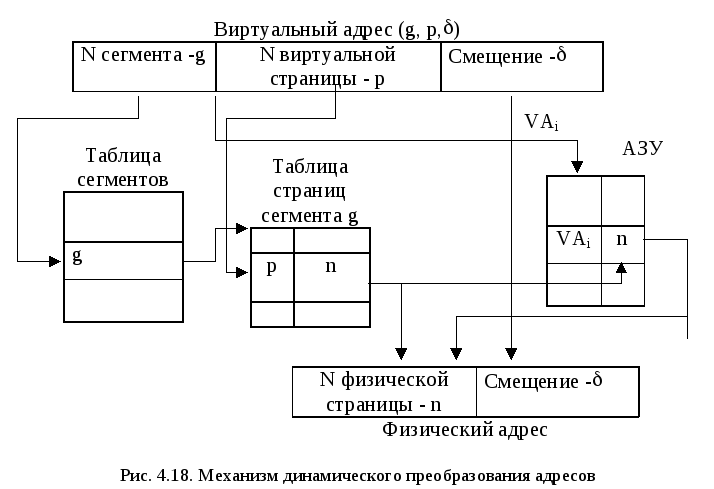

Процесс преобразования адресов посредством таблиц является достаточно длительным и, естественно, приводит к снижению производительности системы. С целью ускорения этого процесса преобразование может осуществляться специальными аппаратными средствами, в основе которых лежит использование принципа ассоциативной памяти. Реализуемый при этом механизм получил название механизма динамического преобразования адресов (рис. 4.18).

Виртуальный адрес страницы VA, составленный из полей g и p, передается в ассоциативную память (буфер быстрой переадресации) в качестве поискового признака — первое поле ассоциативного ЗУ (АЗУ). Вторым полем АЗУ является физический адрес страницы в ОП. При обнаружении совпадения VАi c содержимым памяти из соответствующей ячейки АЗУ выбирается физический адрес страницы n, позволяющий сформировать полный физический адрес элемента данных, находящегося в ОП. Если совпадение не произошло, то трансляция адресов осуществляется обычными методами через таблицы сегментов и страниц. Эффективность механизма динамического преобразования адресов зависит от коэффициента «попадания», т.е. от того, насколько редко приходится обращаться к табличным методам трансляции адресов. Учитывая принцип локальности программ и данных, можно сказать, что при первом обращении к странице, расположенной в ОП, физический адрес определяется с помощью таблиц и загружается в соответствующую ячейку АЗУ. Последующие обращения к странице выполняются с использованием АЗУ.