- •А.Д. Чередов организация эвм и систем

- •Введение

- •Архитектуры, характеристики, классификация эвм

- •1.1. Однопроцессорные архитектуры эвм

- •Название фирм и разработанных ими risc-процессоров

- •Максимальное и среднее число команд, выполняемых в одном машинном цикле

- •1.2. Технические и эксплуатационные характеристики эвм

- •Результаты тестирования процессоров

- •1.3. Классификация эвм

- •1.3.1. Классификация эвм по назначению

- •1.3.2. Классификация эвм по функциональным возможностям и размерам

- •Сравнительные параметры различных классов эвм

- •Функциональная и структурная организация эвм

- •2.1. Связь между функциональной и структурной организацией эвм

- •2.2. Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •2.3. Структура и форматы команд эвм

- •Способ расширения кодов операции

- •2.4. Способы адресации информации в эвм

- •Классификация способов адресации по наличию адресной информации в команде Явная и неявная адресация

- •Классификация способов адресации по кратности обращения в память

- •Непосредственная адресация операнда

- •Прямая адресация операндов

- •Косвенная адресация операндов

- •Классификация способов формирования исполнительных адресов ячеек памяти

- •Относительная адресация ячейки оп Базирование способом суммирования

- •Относительная адресация с совмещением составляющих аи

- •Индексная адресация

- •Стековая адресация

- •2.5. Примеры форматов команд и способов адресации

- •2.5.1. Форматы команд и способы адресации в cisc-процессорах

- •Развитие системы команд процессоров архитектуры Intel

- •Общий формат команд

- •Способы адресации

- •2.5.2. Форматы команд и способы адресации в risc-процессорах

- •2.6. Типы данных

- •Данные со знаком

- •3. Функциональная и структурная организация центрального процессора эвм

- •3.1. Назначение и структура центрального процессора

- •3.2. Регистровые структуры центрального процессора

- •4. Регистры отладки и тестирования.

- •3.2.1. Основные функциональные регистры

- •Регистры общего назначения

- •Регистры сегментов и дескрипторы сегментов

- •Указатель команд

- •Регистр флагов

- •3.2.2. Регистры процессора обработки чисел с плавающей точкой

- •3.2.3. Системные регистры

- •3.2.4. Регистры отладки и тестирования

- •3.3. Назначение, классификация и организация цуу

- •3.3.1. Центральное устройство управления микропрограммного типа

- •3.3.2. Процедура выполнения команд

- •3.3.3. Принципы организации системы прерывания программ

- •Характеристики системы прерывания

- •Программно–управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •3.4. Назначение, классификация и организация алу

- •Классификация алу

- •Обобщенная структурная схема алу

- •Методы повышения быстродействия алу

- •4. Принципы организации подсистемы памяти эвм и вс

- •4.1. Иерархическая структура памяти эвм

- •4.2. Организация внутренней памяти процессора

- •4.3. Способы организации кэш-памяти

- •4.3.1. Общие сведения

- •Типовая структура кэш-памяти

- •4.3.2. Способы размещения данных в кэш-памяти

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •Распределение секторов

- •4.3.3. Методы обновления строк основной памяти

- •Условия сохранения и обновления информации

- •Сквозная запись

- •Обратная запись

- •4.3.4. Методы замещения строк кэш-памяти

- •4.4. Принципы организации оперативной памяти

- •4.4.1. Общие положения

- •4.4.2. Методы управления памятью

- •Типы адресов

- •Распределение памяти фиксированными разделами

- •Распределение памяти разделами переменной величины

- •Перемещаемые разделы

- •4.4.3. Организация виртуальной памяти

- •Страничное распределение

- •Сегментное распределение

- •Странично-сегментное распределение

- •Свопинг

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •Выборка широким словом

- •Расслоение обращений

- •4.4.5. Методы защиты памяти

- •Защита памяти по граничным адресам

- •Защита памяти по маскам

- •Защита памяти по ключам

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •5. Принципы организации подсистемы ввода-вывода

- •5.1. Проблемы организации подсистем ввода-вывода

- •5.2. Способы организации передачи данных

- •Прямой доступ к памяти

- •5.3. Унификация средств обмена и интерфейсы эвм

- •5.3.1. Общая характеристика и классификация интерфейсов

- •5.3.2. Типы и характеристики стандартных шин

- •Характеристики стандартных шин

- •5.4. Современные и перспективные структуры подсистем ввода-вывода

- •6. Многопроцессорные и многомашинные вычислительные системы

- •6.1. Архитектуры вычислительных систем

- •6.2. Сильно связанные многопроцессорные системы

- •6.3. Слабосвязанные многопроцессорные системы

- •Список использованной литератуРы

- •Оглавление

4.2. Организация внутренней памяти процессора

Регистровая структура процессора была рассмотрена в разделе 3.

Обращает на себя внимание ставший стандартным в современной архитектуре ЭВМ прием организации регистров общего назначения в виде сверхоперативного ЗУ с прямой адресацией(короткие адреса регистров размещаются в команде). В машинах с коротким словом, вынуждающим прибегать к одноадресным командам, один из общих регистров выделяется в качестве аккумулятора — регистра, в котором находится один из операндов и в который помещается результат операции. Регистр аккумулятор в явном виде в команде не адресуется, используется подразумеваемая адресация. В этом случае СОЗУ с прямой адресацией (рис. 4.2, а) состоит из совокупности регистров Р[ 0 ], . . . , P[ M ], связанных с входной X и выходной Z шинами, по которым передаются n — разрядные слова. Адрес регистра, к которому производится обращение с целью записи или чтения (управляющий сигнал ЗП/ЧТ) информации, поступает по шине А. Дешифратор адреса ДША формирует управляющие сигналы 0, 1, . . . , М, подключающие регистр с заданным адресом к шинам СОЗУ.

При использовании двухадресных команд типа «регистр-регистр», в которых указываются адреса двух операндов, расположенных в регистрах, и результат операции помещается по одному из этих адресов, данная организация СОЗУ становится неэффективной. Это связано с тем, что за один машинный такт может быть выбрано содержимое только одного регистра. Для реализации таких команд за один такт СОЗУ строится по схеме, приведенной на рис. 4.2, б.

СОЗУ состоит из совокупности регистров, связанных с входной шиной Х и двумя выходными шинами Y, Z. Адреса регистров, к которым производится обращение с целью чтения информации, поступают по шинам А и В. Адрес регистра для записи информации поступает по входу В. Дешифраторы адресов ДША и ДШВ формируют управляющие сигналы 0, 1, . . . , М, подключающие два регистра к выходным шинам при чтении и один регистр к входной шине при записи.

Стековая память,реализующая безадресное задание операндов, является эффективным элементом архитектуры ЭВМ. Стек представляет собой группу последовательно пронумерованных регистров (аппаратный стек) или ячеек памяти, снабженных указателем стека (обычно регистром), в котором автоматически при записи и считывании устанавливается номер (адрес) первой свободной ячейки стека (вершина стека). При операции записи заносимое в стек слово помещается в свободную ячейку стека, а при считывании из стека извлекается последнее поступившее в него слово. Таким образом, в стеке реализуется правило «последний пришел - первый ушел» - магазинная адресация.

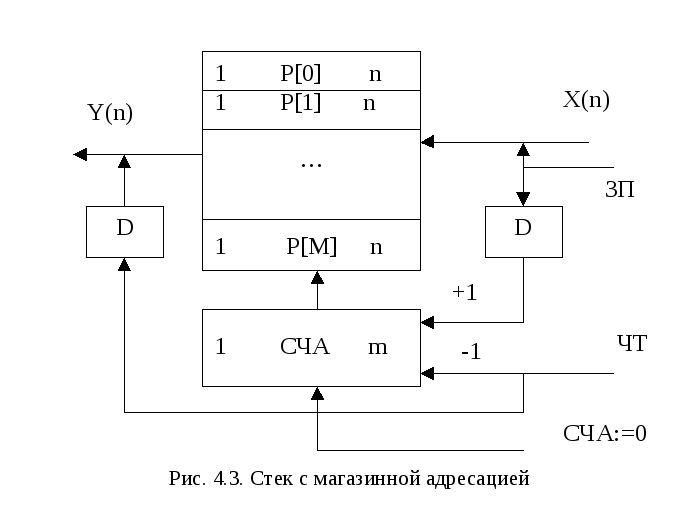

Механизм стековой адресации поясняется на рис. 4.3. Для реализации магазинной адресации используется счетчик адреса СЧА, который перед началом работы устанавливается в состояние ноль, и память (стек) считается пустой. Состояние СЧА определяет адрес первой свободной ячейки. Слово загружается в стек с входной шины Х в момент поступления сигнала записи ЗП.

По сигналу ЗП слово Х записывается в регистр P[СЧА], номер которого определяется текущим состоянием счетчика адреса, после чего с задержкой D, достаточной для выполнения микрооперации записи P[СЧА]:=Х, состояние счетчика увеличивается на единицу. Таким образом, при последовательной загрузке слова А, В и С размещаются в регистрах с адресами P[S], P[S + 1] и P[S + 2], где S — состояние счетчика на момент начала загрузки. Операция чтения слова из ЗУ инициируется сигналом ЧТ, при поступлении которого состояние счетчика уменьшается на единицу, после чего на выходную шину Y поступает слово, записанное в стек последним. Если слова загружались в стек в порядке А, В, С, то они могут быть прочитаны только в обратном порядке С, В, А.

В современных архитектурах процессоров и микропроцессоров стек и стековая адресация широко используется при организации переходов к подпрограммам и возврата из них, а также в системах прерывания.