- •А.Д. Чередов организация эвм и систем

- •Введение

- •Архитектуры, характеристики, классификация эвм

- •1.1. Однопроцессорные архитектуры эвм

- •Название фирм и разработанных ими risc-процессоров

- •Максимальное и среднее число команд, выполняемых в одном машинном цикле

- •1.2. Технические и эксплуатационные характеристики эвм

- •Результаты тестирования процессоров

- •1.3. Классификация эвм

- •1.3.1. Классификация эвм по назначению

- •1.3.2. Классификация эвм по функциональным возможностям и размерам

- •Сравнительные параметры различных классов эвм

- •Функциональная и структурная организация эвм

- •2.1. Связь между функциональной и структурной организацией эвм

- •2.2. Обобщенная структура эвм и пути её развития

- •Обрабатывающая подсистема

- •Подсистема памяти

- •Подсистема ввода-вывода

- •Подсистема управления и обслуживания

- •2.3. Структура и форматы команд эвм

- •Способ расширения кодов операции

- •2.4. Способы адресации информации в эвм

- •Классификация способов адресации по наличию адресной информации в команде Явная и неявная адресация

- •Классификация способов адресации по кратности обращения в память

- •Непосредственная адресация операнда

- •Прямая адресация операндов

- •Косвенная адресация операндов

- •Классификация способов формирования исполнительных адресов ячеек памяти

- •Относительная адресация ячейки оп Базирование способом суммирования

- •Относительная адресация с совмещением составляющих аи

- •Индексная адресация

- •Стековая адресация

- •2.5. Примеры форматов команд и способов адресации

- •2.5.1. Форматы команд и способы адресации в cisc-процессорах

- •Развитие системы команд процессоров архитектуры Intel

- •Общий формат команд

- •Способы адресации

- •2.5.2. Форматы команд и способы адресации в risc-процессорах

- •2.6. Типы данных

- •Данные со знаком

- •3. Функциональная и структурная организация центрального процессора эвм

- •3.1. Назначение и структура центрального процессора

- •3.2. Регистровые структуры центрального процессора

- •4. Регистры отладки и тестирования.

- •3.2.1. Основные функциональные регистры

- •Регистры общего назначения

- •Регистры сегментов и дескрипторы сегментов

- •Указатель команд

- •Регистр флагов

- •3.2.2. Регистры процессора обработки чисел с плавающей точкой

- •3.2.3. Системные регистры

- •3.2.4. Регистры отладки и тестирования

- •3.3. Назначение, классификация и организация цуу

- •3.3.1. Центральное устройство управления микропрограммного типа

- •3.3.2. Процедура выполнения команд

- •3.3.3. Принципы организации системы прерывания программ

- •Характеристики системы прерывания

- •Программно–управляемый приоритет прерывающих программ

- •Организация перехода к прерывающей программе

- •3.4. Назначение, классификация и организация алу

- •Классификация алу

- •Обобщенная структурная схема алу

- •Методы повышения быстродействия алу

- •4. Принципы организации подсистемы памяти эвм и вс

- •4.1. Иерархическая структура памяти эвм

- •4.2. Организация внутренней памяти процессора

- •4.3. Способы организации кэш-памяти

- •4.3.1. Общие сведения

- •Типовая структура кэш-памяти

- •4.3.2. Способы размещения данных в кэш-памяти

- •Прямое распределение

- •Полностью ассоциативное распределение

- •Частично ассоциативное распределение

- •Распределение секторов

- •4.3.3. Методы обновления строк основной памяти

- •Условия сохранения и обновления информации

- •Сквозная запись

- •Обратная запись

- •4.3.4. Методы замещения строк кэш-памяти

- •4.4. Принципы организации оперативной памяти

- •4.4.1. Общие положения

- •4.4.2. Методы управления памятью

- •Типы адресов

- •Распределение памяти фиксированными разделами

- •Распределение памяти разделами переменной величины

- •Перемещаемые разделы

- •4.4.3. Организация виртуальной памяти

- •Страничное распределение

- •Сегментное распределение

- •Странично-сегментное распределение

- •Свопинг

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •Выборка широким словом

- •Расслоение обращений

- •4.4.5. Методы защиты памяти

- •Защита памяти по граничным адресам

- •Защита памяти по маскам

- •Защита памяти по ключам

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •5. Принципы организации подсистемы ввода-вывода

- •5.1. Проблемы организации подсистем ввода-вывода

- •5.2. Способы организации передачи данных

- •Прямой доступ к памяти

- •5.3. Унификация средств обмена и интерфейсы эвм

- •5.3.1. Общая характеристика и классификация интерфейсов

- •5.3.2. Типы и характеристики стандартных шин

- •Характеристики стандартных шин

- •5.4. Современные и перспективные структуры подсистем ввода-вывода

- •6. Многопроцессорные и многомашинные вычислительные системы

- •6.1. Архитектуры вычислительных систем

- •6.2. Сильно связанные многопроцессорные системы

- •6.3. Слабосвязанные многопроцессорные системы

- •Список использованной литератуРы

- •Оглавление

Относительная адресация ячейки оп Базирование способом суммирования

В команде адресный код АКразделяется на две составляющие: АБ– адрес регистра в регистровой памяти , в котором хранится база Б (базовый адрес); C – код смещения относительно базового адреса (рис. 2.7).

Для определения максимальной емкости ОП, адресуемой с помощью базирования, способом суммирования, определим длину кода исполнительного адреса

![]() max{

nБ; nC}.

max{

nБ; nC}.

Так как nБ = mРП и обычно больше, чем nC, то справедливо следующее выражение:

MОП=![]()

![]() =

=![]() ,

,

т. е.

максимальная адресуемая емкость ОП

определяется разрядностью РП. Длина

![]() поля кода команды, задающего адрес

регистра базы АБ, определяется

через емкость РП MРПпо формуле

поля кода команды, задающего адрес

регистра базы АБ, определяется

через емкость РП MРПпо формуле

![]() ³log2MРП.

³log2MРП.

Таким образом, можно

определить количество

![]() двоичных разрядов в адресном поле

команды, необходимое для формирования

АИс размещением базы в РП:

двоичных разрядов в адресном поле

команды, необходимое для формирования

АИс размещением базы в РП:

![]() log2МРП+ nС.

log2МРП+ nС.

Приведенные выражения позволяют определить числовые значения параметров относительной адресации (базирование способов суммирования).

Для того, чтобы увеличить МОП,

необходимо выполнить условие:![]() ³

³![]() ,

т.е mРП³log2MРП+ nС.

,

т.е mРП³log2MРП+ nС.

С помощью метода относительной адресации удается получить так называемый перемещаемый программный модуль, который одинаково выполняется процессором независимо от адресов, в которых он расположен. Начальный адрес программного модуля (база) загружается, при входе в модуль, в базовый регистр. Все остальные адреса программного модуля формируются через смещение относительно начального адреса (базы) модуля. Таким образом, одна и та же программа может работать с данными, расположенными в любой области памяти, без перемещения данных и без изменения текста программы только за счет изменения содержания всего одного базового регистра. Однако время выполнения каждой операции при этом возрастает.

Относительная адресация с совмещением составляющих аи

Для увеличения емкости

адресной ОП (МОП) без увеличения

длины адресного поля команды![]() можно

использовать для формирования

исполнительного адреса совмещение

(конкатенацию) кодов базы и смещения

(рис. 2.8).

можно

использовать для формирования

исполнительного адреса совмещение

(конкатенацию) кодов базы и смещения

(рис. 2.8).

При совмещении кодов базы и смещения

![]() .

.

Таким образом, MОП=![]()

![]() =

=![]() .

.

Следует отметить, что

емкость ОП (МОП) может быть увеличена

в![]() раз за счет использования способа

совмещения. Однако в данном случае

начальные адреса массивов не могут быть

реализованы произвольно, а должны иметь

в младших разрядах nC

нулей.

раз за счет использования способа

совмещения. Однако в данном случае

начальные адреса массивов не могут быть

реализованы произвольно, а должны иметь

в младших разрядах nC

нулей.

Индексная адресация

Для работы программ с массивами, требующими однотипных операций над элементами массива, удобно использовать индексную адресацию. Схема индексной адресации аналогична базированию путем суммирования (см. рис. 2.7). В этом случае адрес i-го операнда в массиве определяется как сумма начального адреса массива (задаваемого полем смещения С) и индекса И, записанного в одном из регистров РП, называемом теперь индексным регистром. Адрес индексного регистра задается в команде полем адреса индекса — АИН(аналогично АБ).

В каждом i-м цикле содержимое индексного регистра изменяется на величину постоянную (часто равную 1). Использование индексной адресации значительно упрощает программирование циклических алгоритмов.

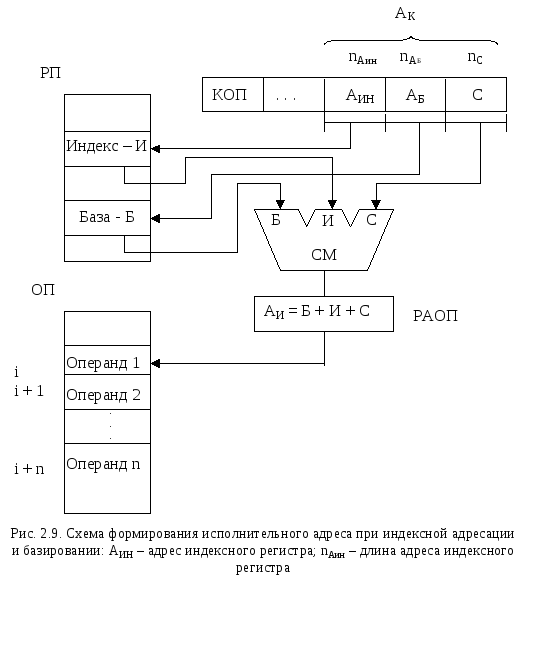

Для эффективной работы при относительной адресации применяется комбинированная индексация с базированием, при которой адрес операнда вычисляется как сумма трех величин (рис. 2.9):

АИОП = Б + И + С.