- •Лабораторная работа № 10

- •Наименование работы

- •Исследование последовательностных схем

- •Цель работы

- •Задание к лабораторной работе

- •Варианты заданий

- •Перечень используемого оборудования Краткие теоретические сведения

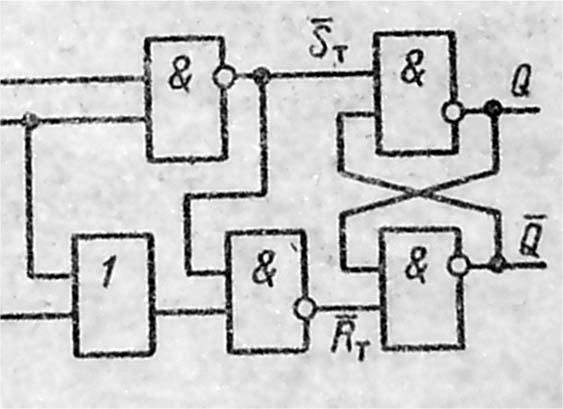

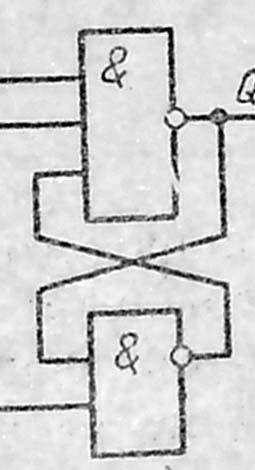

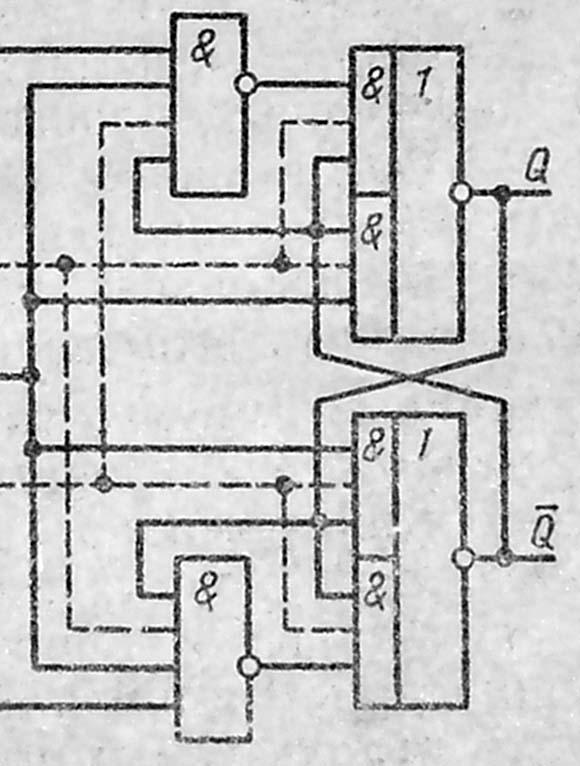

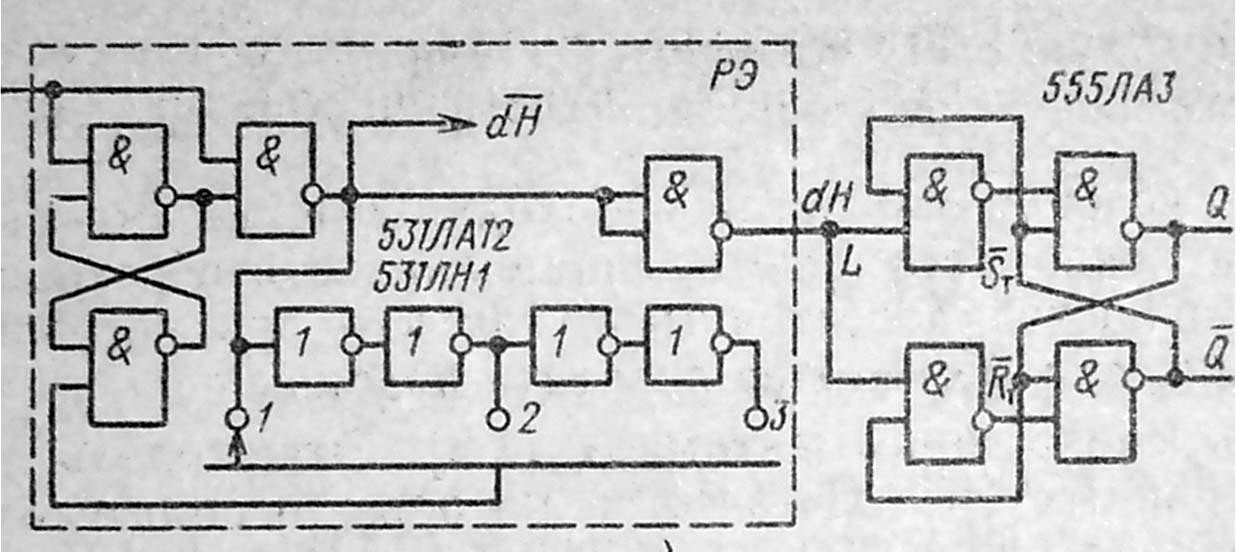

- •Основная модель асинхронного потенциального автомата

- •Пример последовательностной схемы

- •Разработка vhdl модели последовательностных схем

- •Порядок проведения работы

- •Содержание отчета

- •Контрольные вопросы

- •Список литературы

- •Приложение 1 Варианты последовательностных схем

Содержание отчета

Отчет к лабораторной работе должен содержать:

-

Задание на разработку последовательностной схемы

-

Структурную схему VHDL модели цифровой системы

-

Программную модель цифровой системы

-

Временной анализ верификации модели цифровой системы в Stateflow\Simulink

-

Временной анализ верификации VHDL модели в среде MAX PLUS

-

Временной анализ верификации VHDL модели в приложении GHDL

-

Принципиальную электрическую схему валидации VHDL модели на макете FLEX8000.

-

Временной анализ валидации VHDL модели цифровой системы

-

Оценку коэффициентов управляемости и коэффициентов наблюдаемости схемы

-

Оценку длины критического пути

-

Рекомендации по совершенствованию системы тестирования

-

Выводы по лабораторной работе.

Контрольные вопросы

-

Приведите определение последовательностной схемы

-

Приведите определение потенциального автомата

-

Приведите определение импульсного автомата

-

Приведите структурную схему последовательностной схемы

5. Приведите основные элементы языка VHDL, используемые при описании последовательностных схем.

Список литературы

1. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на

интегральных микросхемах: Справочник.- М.: Радио и связь, 1990.- 340 с.

2. Хопкфорт Джон Э., Мотванн Раджив, Ульиман Джефри Д. Введение в теорию

автоматов, языков и вычислений.: Пер. с англ.- М.: Издательский дом «Вильямс»,

2002.- c. 224.

3. Matlab Stateflow\Simulink Toolboxes

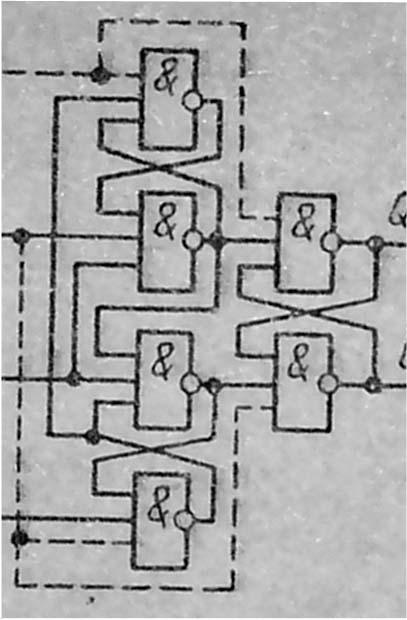

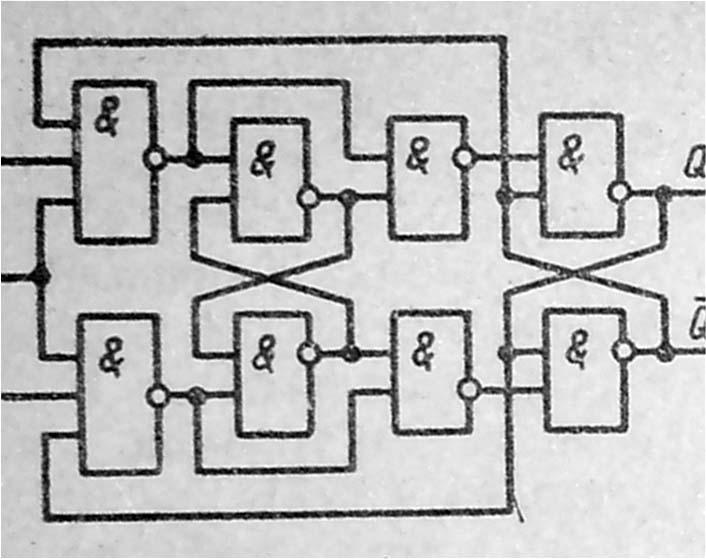

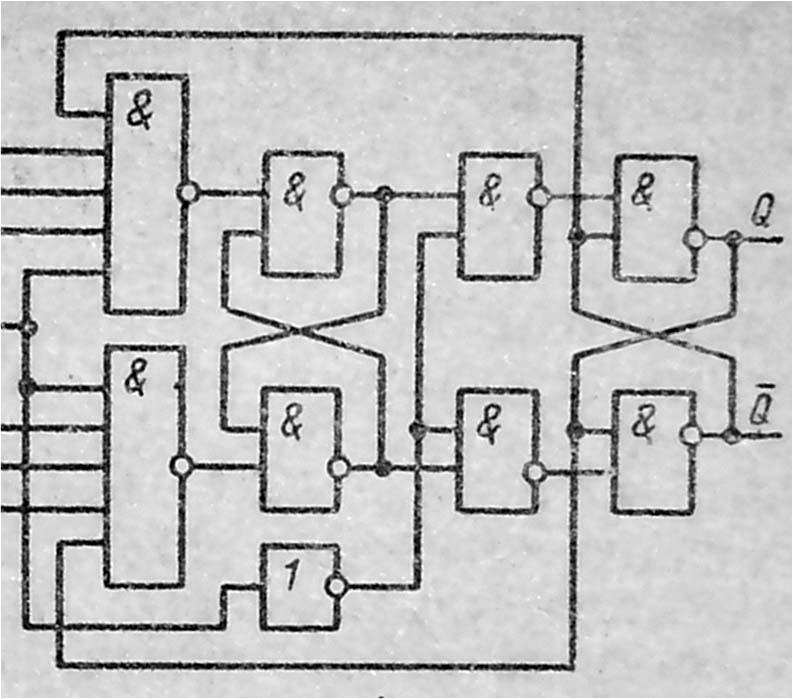

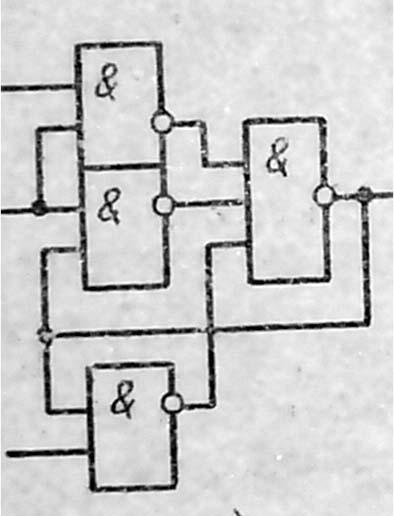

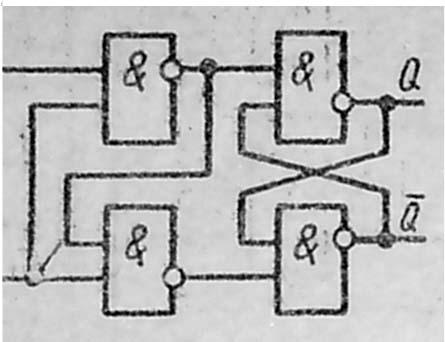

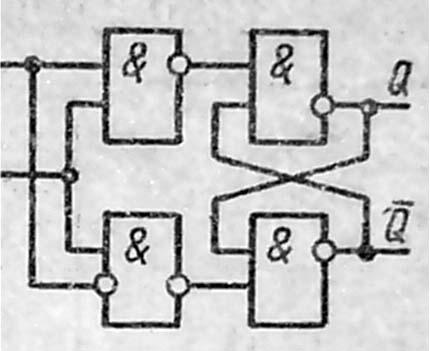

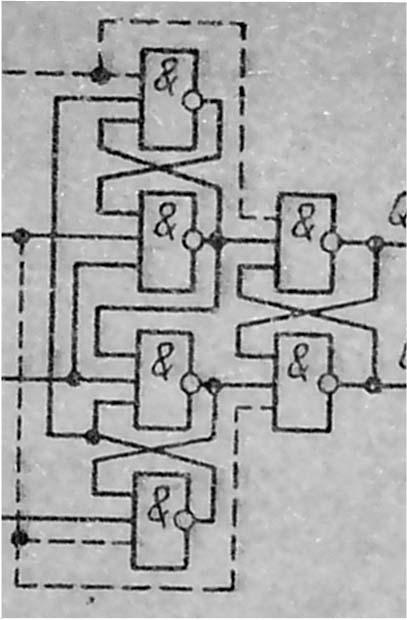

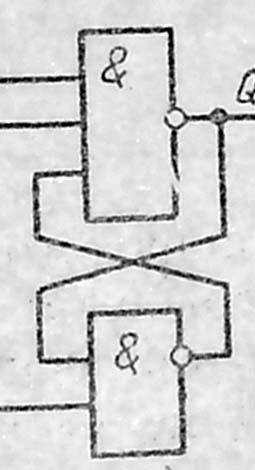

Приложение 1 Варианты последовательностных схем

|

№ |

|

|

1 |

|

|

2 |

|

|

3 |

|

|

4 |

|

|

5 |

|

|

6 |

|

|

7 |

|

|

8 |

|

|

9 |

|

|

10 |

|

|

11 |

|

|

12 |

|

|

13 |

|

|

14 |

|

|

15 |

|

|

16 |

|

Содержание

Наименование работы 1

Цель работы 1

Задание к лабораторной работе 1

Варианты заданий 1

Перечень используемого оборудования 2

Краткие теоретические сведения 2

Основная модель асинхронного потенциального автомата 2

Пример последовательностной схемы 4

Разработка VHDL модели последовательностных схем 6

Порядок проведения работы 6

Содержание отчета 7

Контрольные вопросы 7

Список литературы 7

Приложение 1 Варианты последовательностных схем 8