ВМСиС_1 / ВМСиС / лабораторные / labRab12_2012

.pdf

Лабораторная работа №12

Наименование работы

Разработка VHDL модели многопортовой памяти

Цель работы

1.Закрепить понятие конечного автомата на примере разработки многопортовой памяти

2.Изучить особенности проектирования многопортовой памяти на примере трехпортовой памяти

Задание к лабораторной работе

Варианты заданий формируются для заданных значений разрядности 3-х портовой памяти

Вариант Разрядность памяти

N

12

23

34

44

53

62

73

84

93

102

113

124

2.Приведите математическую модель устройства управления трехпортовой памяти

3.Приведите VHDL модель трехпортовой памяти

4.Сформируйте тестовые сигналы.

5.Протестируйте устройство на макете FLEX8000.

Перечень используемого оборудования

1.Разработка VHDL модели цифровой системы должна проводиться в среде

GHDL.

2.VHDL модель цифровой системы должна быть верифицирована в среде

GHDL.

3.Для валидации VHDL модели цифровой системы необходимо использовать целевое устройство - лабораторный макет FLEX8000 (target).

4.Для визуального контроля за формой сигнала и оценки временных параметров необходимо использовать аналоговый осциллограф С1-93.

5.Разработка VHDL модели цифровой системы должна проводиться на IBM совместимых ПК с использованием операционной системы Windows XP (host PC).

Основные определения

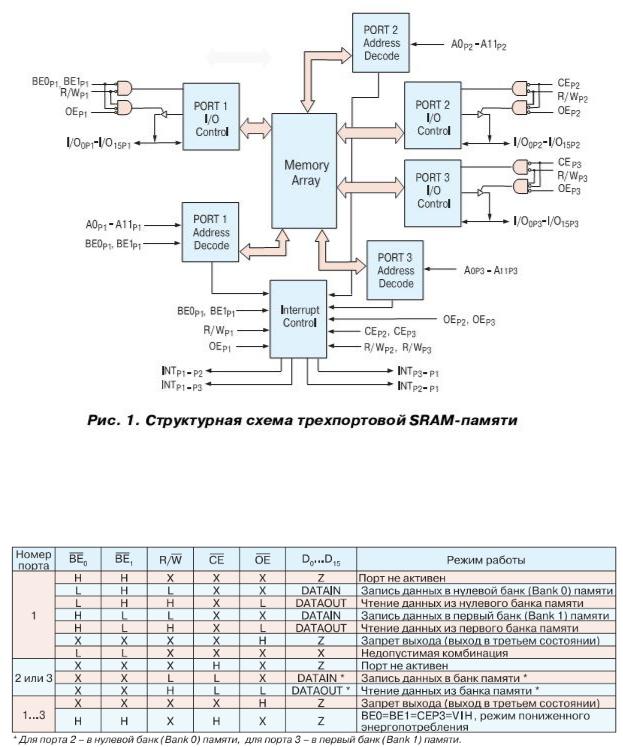

Структурная схема трехпортовой памяти приведена на рис.1

Поведенческая модель устройства управления задается таблицей истинности Таблица истинности устройства управления трехпортовой памяти

Порядок выполнения лабораторной работы

1.В соответствии с вариантом сформируйте тестовый пример.

2.Составьте граф переходов устройства управления.

3.Используя результаты предыдущих лабораторных работ, составьте иерархическую структурную схему устройства управления многопортовой памятью

4.Составьте поведенческие модели элементов структурной схемы.

5.Составьте математическую модель устройства управления.

6.Составьте VHDL модель устройства управления.

7.Сформируйте тестовые сигналы и протестируйте многопортовую память в

GHDL.

8.Проведите валидацию умножителя на лабораторном макете FLEX8000.

9.Оформите результаты лабораторной работы.

Порядок проведения работы на макете

1. Подготовка к выполнению лабораторной работы.

Разработка VHDL моделей дешифраторов и мультиплексоров и их верификация должны быть проведены в среде OrCAD (host PC)

Выполнение лабораторной работы проводится в аудитории под контролем преподавателя.

Перед выполнением лабораторной работы необходимо проверить наличие защитного заземления, исправность схем аварийного отключения питания.

2. Порядок выполнения лабораторной работы:

-в соответствии с разработанной принципиальной электрической схемой, выполнить необходимые коммутации на макетной плате FLEX8000 (target);

-подсоединить к контрольным точкам щупы осциллографа;

-включить питание (подсоединить FLEX8000 к удлинителю USB);

-при правильном соединении загорается светодиод HL1;

-при возникновении проблем с соединением необходимо обратиться к преподавателю;

-сконфигурировать ПЛИС FLEX8000 в среде MAX PLUS (Host PC + target);

-наблюдать временные диаграммы в контрольных точках, обеспечивая синхронизацию органами управления осциллографа;

-при несоответствии наблюдаемых осциллограмм заданию, необходимо повторить синтез VHDL моделей схем с учетом отмеченных недостатков; затем необходимо провести верификацию VHDL модели. Внесенные изменения необходимо согласовать с преподавателем и повторить валидацию VHDL модели

(Host PC);

-скопировать временные диаграммы с экрана осциллографа.

Содержание отчета

Отчет к лабораторной работе должен содержать:

1.Задание на разработку многопортовой памяти заданной разрядности.

2.Математическую модель устройства управления многопортовой памяти.

3.Структурную схему VHDL модели цифровой системы

4.Граф переходов устройства. Программную модель цифровой системы.

5.Временной анализ верификации VHDL модели в среде GHDL.

6.Принципиальную электрическую схему валидации VHDL модели на макете

FLEX8000.

7.Временной анализ валидации VHDL модели цифровой системы.

8.Оценку коэффициентов управляемости и коэффициентов наблюдаемости схемы

9.Оценку длины критического пути

10.Рекомендации по совершенствованию системы тестирования

11.Выводы по лабораторной работе.

Контрольные вопросы

1.Опишите назначение многопортовой памяти

2.Опишите отличительные особенности многопортовой памяти от однопортовой

3.Приведите структурную схему многопортовой памяти

4.Опишите назначение устройства управления многопортовой памятью.

5.Приведите поведенческую модель устройства управления

6.Приведите ГСА управления многопортовой памятью

7.Приведите примеры аппаратной реализации многопортовой памяти.

Литература

1.Т. Кормен. И др. Алгоритмы: построение и анализ / Пер. с англ. Под ред. А.Шеня.-

М.: МЦНМО, 2002.- 960 с.

2.Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах.- М.: Радио и связь, 1990.- 304 с.

Оглавление |

|

Наименование работы............................................................................................................... |

1 |

Цель работы.............................................................................................................................. |

1 |

Перечень используемого оборудования .................................................................................. |

1 |

Основные определения............................................................................................................. |

2 |

Порядок выполнения лабораторной работы............................................................................ |

3 |

Порядок проведения работы на макете................................................................................ |

3 |

Содержание отчета ................................................................................................................... |

3 |

Контрольные вопросы.............................................................................................................. |

4 |

Литература ................................................................................................................................ |

4 |

Оглавление................................................................................................................................ |

4 |