ВМСиС_1 / ВМСиС / лабораторные / lab13_2012

.pdf

Лабораторная работа №10

Наименование работы

Разработка VHDL модели арбитра шины

Цель работы

1.Закрепить понятие конечного автомата на примере разработки арбитра шины 8289

2.Изучить функции арбитра шины в многопроцессорной системе

Задание к лабораторной работе

Варианты заданий формируются для заданного количества микропроцессоров n

Вариант Количество микропроцессоров

N

12

23

34

45

54

63

72

83

94

105

114

123

2.Приведите математическую модель арбитра шины

3.Приведите VHDL модель арбитра шины.

4.Сформируйте тестовые сигналы.

5.Протестируйте арбитр шины на макете FLEX8000.

Перечень используемого оборудования и программного обеспечения

1.Разработка VHDL модели цифровой системы должна проводиться в среде

GHDL.

2.VHDL модель цифровой системы должна быть верифицирована в среде

GHDL.

3.Для валидации VHDL модели цифровой системы необходимо использовать целевое устройство - лабораторный макет FLEX8000 (target).

4.Визуальный контроль за формой сигнала и оценки временных параметров проводится с использованием аналогового осциллографа С1-93.

5.Разработка VHDL модели цифровой системы должна проводиться на IBM совместимых ПК с использованием операционной системы Windows XP (host PC).

6.Отчет по лабораторной работе должен выполняться в Open Office.

Основные определения

Арбитр шины 8289 управляет доступом к общей коллективно используемой шине. Каждому возможному владельцу шины или микропроцессору необходим арбитр для сопряжения с общей, коллективно используемой шиной, которую корпорация Intel называет Multibus, а фирма IВМ именует Micro Channel.

Общая шина используется не только для передачи информации от одного микропроцессора к другому, а и во всех других случаях, когда каждый возможный владелец шины работает со своими локальными шинами с использованием своих локальных программ, локальной памяти и устройств ввода-вывода. Микропроцессоры, соединенные в системе подобным образом, часто называют параллельными или распределенными (рагаllel/distributed) процессорами, поскольку они выполняют программу и задачи параллельно.

Организация арбитра шины 8289

На рис. 1 приведены блок-схема арбитра шины 8289. На левой стороне блок-схемы показаны выводы и соответствующие сигналы для подключения к ведущему (главному) микропроцессору. С правой стороны показаны сигналы арбитра шины 8289, предназначенные для управления общей коллективно используемой шиной или, иначе, шиной Multibus.

Арбитр шины 8289 управляет обшей шиной, переводя вывод READY микропроцессора на низкий логический уровень (нет готовности) в том случае, если доступ к обшей шине для него должен быть закрыт. Такая блокировка (blocking) происходит при каждом получении доступа к обшей шине со стороны другого микропроцессора. В результате микропроцессор, запрашивающий доступ к шине, может быть заблокирован подаваемым на его вывод READY сигналом нулевого логического уровня. Микропроцессор и выполняемая им программа, при наличии на выводе READY сигнала низкого логического уровня, находятся в состоянии ожидания, пока арб не даст разрешение на доступ к общей шине. Таким образом, доступ в данный момент времени к общей шине получает только один микропроцессор. Следует отметить, что для разрешения конфликтных ситуаций с шиной при наличии арбитра шины 8289 не требуется никаких специальных команд, поскольку арбитраж выполняется аппаратно.

Рис.1. Блоксхема арбитра шины 8289

Назначение выводов и сигналов

АЕN выходной сигнал на выводе АЕN (address enable) переключает выходы буферов адреса в системе в третье состояние, т. е. состояние высокого импеданса.

ANYRQST входной сигнал на выводе ANYRQST (any request) предназначен для предотвращения получения доступа к общей шине со стороны микропроцессора, имеющего более низкий приоритет. При наличии сигнала низкого логического уровня на этом выводе осуществляется нормальный арбитраж, и микропроцессор с более низким приоритетом может получить доступ к общей шине в том случае, когда CBRQ также имеет низкий логический уровень.

BCLK входной тактирующий сигнал BCLK (bus сlосk) предназначен для синхронизации всех интерфейсных сигналов системы со многими потенциальными владельцами общей шины.

BPRN входной сигнал BPRN (bus priority input) позволяет арбитру шины 8289 запрашивать общую шину при следующем заднем фронте сигнала

BCLK.

ВРRО выходной сигнал BPRO (bus priority output), предназначенный для разрешения конфликтных ситуаций, связанных с приоритетом в системе, содержащей несколько потенциальных владельцев обшей шины.

BREQ выходной сигнал на одноименном выводе BREQ (bus request) используется для запроса доступа к общей шине.

BUSY двунаправленные сигналы на выводе BUSY (busy) указывают, что арбитр шины 8289 владеет общей шиной в случае выходного сигнала, а в случае входного сигнала используется для обнаружения того, что другой арбитр шины 8289, получил доступ к общей шине.

CBRQ двунаправленные сигналы на выводе CBRQ (common bus request) применяются в том случае, когда микропроцессор с более низким приорите-

том запрашивает использование общей шины. Когда арбитр шины 8289 запрашивает общую шину, то сигнал на выводе CBRQ имеет низкий логический уровень и в этом состоянии, пока арбитр шины 8289 не получит доступ к шине.

CLK сигнал на выводе CLK (с1оск) генерируется синхрогенератором 8284А и обеспечивает внутреннюю синхронизацию арбитра шины 8289.

CRQLCK сигнал на вводе CRQLCK (common request lock) предотвращает передачу арбитром шины 8289 общей шины какому-либо другому арбитру 8289 в системе. Этот сигнал функционирует вместе с сигналом на выводе

CBRQ.

INIT сигнал на выводе INIT (initialization) переводит арбитр шины 8289 в исходное состояние и обычно подсоединяется к системному сигналу сброса

RESET.

IOB сигнал на выводе IOB (I/O bus) определяет: работает ли устройство в системе с общей шиной (если выбирается по RESB) с устройствами ввода-вывода (IOB = 0) или с памятью и устройствами ввода-вывода (IOB = 1).

LOCK сигнал от ведущего микропроцессора, поступающий на ввод LOCK (1оск), не позволяет арбитру шины 8289 предоставлять другому микропроцессору доступ к обшей шине. У микропроцессоров 8086/8088 имеется ряд команд, которые совместно с префиксом LOCK препятствуют получению другими микропроцессорами доступа к общей шине. Этот префикс можно использовать только с командами add, adc, and, btc, btr, bts, cmpxchg, dec, inc, neg, not, or, sbb, sub, xor, xadd, xchg.

RESB входной сигнал на выводе RESB (resident bus) позволяет арбитру шины 8289 работать в системах с обшей шиной или локальной шиной. Если сигнал на выводе RESB имеет высокий логический уровень, то арбитр шины 8289 имеет конфигурацию мастера обшей шины. Если сигнал имеет низкий логический уровень, то арбитр шины 8289 конфигурирован как мастер локальной шины. Когда арбитр конфигурирован как мастер общей шины, то доступ к конкретной шине определятся с помощью сигнала, поступающего на вывод SYSB/RESB.

S2, S1 и S0 cигналы состояния процессора, поступающие на одноименные выводы S2—S0 (status) арбитра шины, инициируют запросы и отказы на использование обшей шины. Эти выводы подсоединяются также к аналогичным выводам контроллера 8288.

SYSB/RESВ сигнал, поступающий на вывод SYSB/RESB (system bus/resident bus), выбирает доступ к обшей шине при наличии сигнала высокого логического уровня или локальной шине при сигнале низкого уровня.

Принцип работы арбитра шины 8289

Как показывает описание назначения выводов и соответствующих сигналов, арбитр шины 8289 может функционировать и трех основных режимах: 1) режиме работы с периферийной шиной устройств ввода-вывода; 2)

режиме работы с локальной шиной и 3) одношинном режиме работы (табл. 1).

В режиме работы с периферийной шиной ввода-вывода (I/O peripheral bus mode) все устройства на локальной шине рассматриваются как устройства ввода-вывода, включая память, и доступ к ним осуществляется по командам ввода-вывода. При всех обращениях к памяти реализуется доступ к общей шине и при всех обращениях к устройствам ввода-вывода к шине.

Режим работы с локальной шиной (геsident bus mode) предоставляет процессору доступ как к локальной, так и к общей шине. В этом режиме имеется только одно ведущее устройство.

Наконец, одношинный режим (single bus mode) осуществляет связь микропроцессора с общей шиной, но при этом микропроцессор не имеет локальной памяти или локальных устройств ввода-вывода.

Во многих системах один микропроцессор устанавливается как мастер (хозяин, владелец) общей шины (в одношинном режиме работы арбитра) для того, чтобы управлять обшей шиной и становиться ее владельцем.

Мастер общей шины (shared bus master) управляет системой с помощью совместно используемой памяти и устройств ввода-вывода. Дополнительные микропроцессоры подключаются к общей шине в качестве мастеров локальной или периферийной шины устройств ввода-вывода. Эти дополнительные мастера шины обычно выполняют независимые задачи, результаты которых по общей шине сообщаются ведущему мастеру шины.

Таблица 1. Режимы работы арбитра шины 8289

Режим |

|

|

Подключение выводов |

|

Одношинный |

|

|

IOB =1 и RESB =0 |

|

С локальной шиной |

|

|

IOB =1 и RESB =1 |

|

С |

периферийной |

шиной |

ввода- |

IOB =0 и RESB =0 |

вывода |

|

|

|

|

С |

периферийной |

шиной |

ввода- |

IOB =0 и RESB =1 |

вывода и локальной шиной |

|

|

||

При одношинном режиме работы арбитра микропроцессор сопрягается с общей шиной, которая содержит устройства ввода-вывода и память, которые совместно используются и другими микропроцессорами.

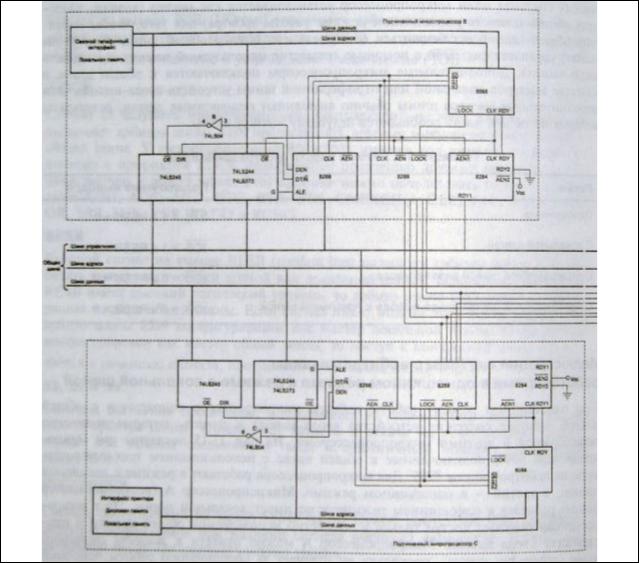

На рис. 2 показаны три микропроцессора 8088, подключенные к общей шине с использованием трех соответствующих арбитров шины 8289. Два микропроцессора работают в режиме с локальной шиной, а третий — в одношинном режиме.

Микропроцессор А (ведущий, мастер шины) работает в одношинном режиме и не имеет локальной шины. Этот микропроцессор получает доступ только к совместно используемой общей памяти и пространству вводавывода. Микропроцессор А можно считать мастером системной шины (system bus master), поскольку он отвечает за координацию работы основной памяти и выполнение задач ввода-вывода.

Другие два подчиненных микропроцессора В и С работают в режиме с локальной шиной, позволяющем им иметь доступ как к обшей шине, так и к своим локальным шинам. Подчиненные микропроцессоры используются для выполнения задач, которые не зависят от мастера системной шины.

Рис.2. Соединение трех микропроцессоров

Фактически, ведущий микропроцессор прерывается от выполнения своей задачи только в том случае, когда одному из подчиненных микропроцессоров необходимо осуществить передачу данных между ним и общей шиной. Такая схема соединения позволяет всем трем микропроцессорам выполнять задачи одновременно, кроме того, при необходимости данные могут быть использованы всеми микропроцессорами.

Ведущий микропроцессор А предоставляет пользователю возможность работы с видеотерминалом, который позволяет выполнять программы и, в целом, управляет системой.

Микропроцессор В управляет всей телефонной связью и передает полученную информацию блоками на общую шину. Это означает, что микропроцессор В ожидает, пока каждый символ не будет передан или принят и управляет протоколом, используемым при передаче.

Допустим, например, что через связной телефонный интерфейс передается блок данных в 1 Кбайт со скоростью 100 символов/с. Это означает, что для передачи данных потребуется чуть более 10 с. Микропроцессор В, не обременяя мастера шины (ведущий микропроцессор А) в течение 10 с, последовательно передает данные, используя свою локальную память и связной интерфейс. Это освобождает ведущий микропроцессор для выполнения других задач. Микропроцессор В прерывает его только один раз во время передачи данных между совместно используемой общей памятью и его локальной запоминающей системой. На такую передачу данных требуется всего несколько сотен микросекунд, а переданными данными впоследствии может

воспользоваться и ведущий микропроцессор, так что это, по сути, передача данных между подчиненным микропроцессором В и ведущим.

Микропроцессор С используется как спулер печати (print spooler). Его единственная задача заключается в распечатке данных на принтере. Каждый раз, когда ведущему микропроцессору требуется отпечатать выходные данные, то эта задача переадресовывается подчиненному микропроцессору С. После этого микропроцессор С получает доступ к совместно используемой общей памяти, читает из нее данные, предназначенные для печати, и накапливает их в своей локальной памяти. Затем эти данные распечатываются, освобождая тем самым ведущий микропроцессор для выполнения других задач.

Таким образом, представленная схема позволяет выполнять программу ведущему микропроцессору, передавать данные через связной интерфейс, с помощью микропроцессора В, а также распечатывать информацию на принтере под управлением микропроцессора С. Фактически количество подсоединяемых к системе микропроцессоров и число одновременно выполняемых задач при использовании подобной схемы ничем не ограничено.

Обслуживание приоритетов для арбитров шин 8289

В практических применениях арбитра шины 8289 к общей шине всегда подключается более одного микропроцессора. И поскольку в определенный момент времени только один микропроцессор может получать доступ к общей шине, то должен применяться некий метод по разрешению возможных конфликтных ситуаций. Схемы обслуживания приоритетов и предназначены для препятствия одновременному получению доступа к шине более чем одним микропроцессором. При использовании арбитра шины 8289 существует два способа разрешения проблемы: схема с последовательным опросом и схема параллельного обслуживания приоритетов.

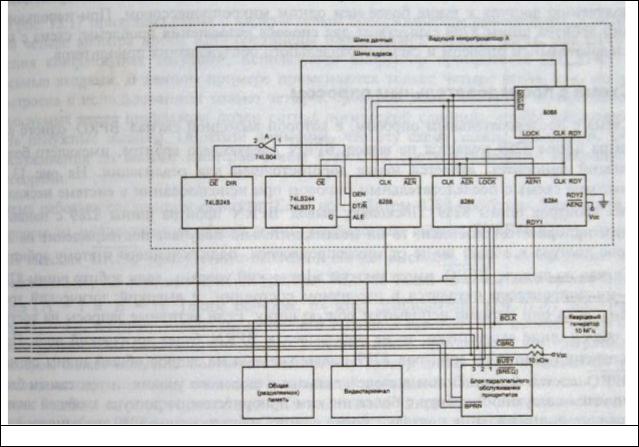

Схема с последовательным опросом

Схема с последовательным опросом, в которой выходной сигнал BPRO одного арбитра шины 8289 подается на вывод BPRN следующего арбитра, имеющего более низкий приоритет, является менее дорогостоящей для реализации. На рис. 3 показана схема с последовательным опросом при использовании в системе нескольких арбитров шины 8289. Поскольку вывод BPRN арбитра шины 8289 с наивысшим приоритетом заземлен, то он незамедлительно получает подтверждение на запрос доступа к обшей шине от микропроцессора, подключенного к этому арбитру.

Рис.3. Схема с последовательным опросом

Сигнал на выводе BPRO имеет низкий логический уровень, если арбитр шины 8289 и микропроцессор находятся в пассивном состоянии, и высокий логический уровень, если они активно используют общую шину. Если активные запросы на доступ к обшей шине отсутствуют, то на всех выводах BPRN будет логический ноль. При получении одним из арбитров 8289 подтверждения на запрос общей шины сигнал BPRO на его одноименном выводе становится высокого уровня, и тем самым блокируется следующий арбитр с более низким приоритетом от доступа к общей шине. Если же подтверждение получают более одного арбитра шины 8289, то одновременно могут функционировать более одного арбитра. Такая схема обслуживания приоритетов используется редко, т. к. в одно и то же время доступ к общей шине могут получить два микропроцессора. Поэтому корпорация Intel рекомендует ограничить такую схему до трех арбитров 8289 в системе, в которой используется тактовая частота шины около 10 МГц или меньше. Конфликтные ситуации при такой частоте шины не происходят, и доступ к общей шине в любой момент времени получает только один микропроцессор.

При подключении большего числа арбитров корпорация Intel предлагает разрешение конфликтных ситуаций путем использования схемы с параллельным обслуживанием.

Схема с параллельным обслуживанием приоритетов

На рис. 4 приведена схема с параллельным обслуживанием приоритетов, в которой четыре арбитра шины 8289 соединены параллельной схемой. Здесь, для разрешения конфликтных ситуаций, используется шифратор приоритетов (74LS148) с восьмью входами. В данном примере применяются только четыре входа, т. к. схема построена с использованием только четырех арбитров шины 8289. На четыре неиспользуемых входа шифратора подан сигнал логической единицы, чтобы заблокировать ненужные выводы. Обратите внимание, что эту схему можно расширить для обслуживания до восьми арбитров шины 8289 с их соответствующими микропроцессорами.

Схема работает следующим образом. Если все арбитры 8289 пассивны (отсутствуют запросы на использование обшей шины посредством вывода

SYSB/RESВ), то на всех выводах BREQ присутствует выходной сигнал высокого логического уровня и, следовательно, на всех выходах шифратора 74LS148 также имеется логическая единица (А = 1 и В = 1). Таким образом, на вход дешифратора (74LS138) поступит код 112 = 310 поэтому только на одном его выходе 3 будет сигнал низкого логического уровня. Это означает, что доступ к общей шине при запросе его микропроцессором может получить соответствующий ему арбитр шины 8289, подключенный к этому выходу и поэтому имеющий наивысший приоритет.

С другой стороны, если запрос исходит от микропроцессора с более низким приоритетом, то соответствующий ему арбитр шины формирует сигнал низкого логического уровня на выводе BREQ. Это приводит к тому, что на входе BPRN только этого арбитра схемой будет сформирован сигнал низкого логического уровня, который и разрешит доступ к обшей шине. Например, если крайний справа арбитр 8289 устанавливает сигнал низкого логического уровня на своем выводе BREQ, который поступит на вход 3 шифратора. В этом случае шифратор 74LS148 генерирует выходной код 002 = 010. При подаче этого кода на вход дешифратора 74LS138 только на одном его выводе 0 будет присутствовать сигнал логического нуля, который поступит на вывод BPRN крайнего справа арбитра шины 8289, предоставляя ему тем самым доступ к общей шине. При этом также блокируются все другие запросы, поскольку сигнал BUSY тоже становится низкого логического уровня. В случае нескольких одновременных запросов схема автоматически формирует только один сигнал BPRN, предупреждая возникновение конфликтных ситуаций, независимо от количества подключенных к системе арбитров 8289.