- •Наименование работы

- •Цель работы

- •Задание к лабораторной работе

- •Перечень используемого оборудования и программного обеспечения

- •Основные определения

- •Основные операции

- •Контроллер DМА 8237

- •Назначение выводов и сигналов

- •Порядок выполнения лабораторной работы

- •Порядок проведения работы на макете

- •Содержание отчета

- •Контрольные вопросы

- •Литература

Лабораторная работа №14

Наименование работы

Разработка VHDL модели контроллера прямого доступа к памяти

Цель работы

1.Закрепить понятие конечного автомата на примере разработки контроллера прямого доступа к памяти (ПДП).

2.Изучить применение контроллера ПДП (DMA).

3.Изучить принцип обмена данными с использованием DМА.

4.Изучить действие управляющих сигналов HOLD и HLDA, используемых для прямого доступа к памяти.

4.Изучить функции контроллера DМА 8237 при обмене данными в составе ВМ.

Задание к лабораторной работе

Варианты заданий формируются для заданного режима работы контроллера DMA

№ варианта |

Функции ПДП |

1 |

Передача данных «память - память» |

|

|

2 |

Передача данных «память - принтер» |

|

|

3 |

Передача данных «у.ввода - память» |

|

|

4 |

Передача данных «память — у.вывода» |

|

|

5 |

Передача данных «память - дисплей» |

|

|

6 |

Передача данных «у.ввода — у.вывода» |

|

|

2.Приведите математическую модель контроллера DMA.

3.Приведите VHDL модель контроллера DMA.

4.Сформируйте тестовые сигналы.

5.Протестируйте контроллер DMA на макете FLEX8000.

Перечень используемого оборудования и программного обеспечения

1.Разработка VHDL модели цифровой системы должна проводиться в среде GHDL.

2.VHDL модель цифровой системы должна быть верифицирована в среде

GHDL.

3.Для валидации VHDL модели цифровой системы необходимо использовать целевое устройство - лабораторный макет FLEX8000 (target).

4.Визуальный контроль за формой сигнала и оценки временных параметров проводится с использованием аналогового осциллографа С1-93.

5.Разработка VHDL модели цифровой системы должна проводиться на IBM совместимых ПК с использованием операционной системы Windows XP (host PC).

6.Отчет по лабораторной работе должен выполняться в Open Office.

Основные определения

В лабораторной работе представлена последняя (наряду с программным

обменом и использованием прерываний) разновидность системы ввода-вывода с использованием прямого доступа к памяти (ПДП) или, иначе, по-английски DМА (Direct memory ассеss).

Метод ввода-вывода с использованием DМА обеспечивает устройствам прямой доступ к памяти без участия микропроцессора, т.е. в течение временного отключения микропроцессора от процесса обмена. Это позволяет осуществлять передачу данных между памятью и устройством ввода-вывода со скоростью, которая ограничивается только элементами памяти в системе или контроллером DМА. Скорость передачи при использовании DМА может достигать 32—40 Мбайт/с.

Передачи ПДП используются для многих целей, но наиболее часто для регенерирования динамической памяти, обновления информации на экране видеодисплея и в системах внешней памяти на дисках. Кроме того, DМА-пере- дачи используются для организации высокоскоростных передач типа "памятьпамять".

Основы процесса прямого доступа к памяти

Для запроса и подтверждения процесса ПДП в системе на базе микропроцессора используются два управляющих сигнала. Сигнал HOLD (hold) — это входной сигнал для микропроцессора на одноименном его выводе, используемый для запроса системной шины со стороны устройства для выполнения им процесса прямого доступа к памяти, а сигнал HLDA (hold acknowledge) является выходным сигналом микропроцессора, подтверждающим предоставление системной шины для выполнения процесса DМА.

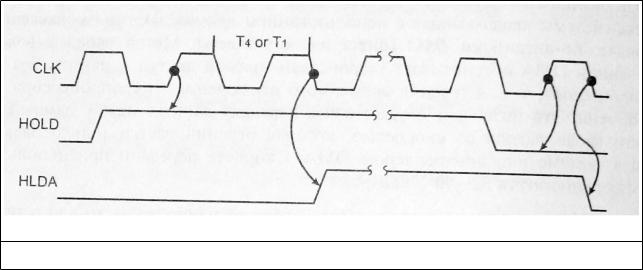

На рис. 1 показана типичная временная диаграмма для этих двух управляющих сигналов микропроцессора для процесса ПДП.

Рис.1. Временная диаграмма для управляющих сигналов

Запрос на захват шины для выполнения операций DМА происходит при размещении на выводе HOLD микропроцессора сигнала высокого логического уровня. Микропроцессор (в течение нескольких тактовых импульсов) временно приостанавливает выполнение программы и освобождает шину адреса, данных и управления, переводя свои соответствующие выводы в состояние высокого импеданса. Микропроцессор в таком состоянии представляется таким, как будто бы он отсоединен от сокета (socket), в который он установлен. Это позволяет внешним устройствам ввода-вывода или другим микропроцессорам получить доступ к системной шине, для осуществления прямого доступа к памяти.

Временная диаграмма показывает, что сигнал HOLD формируется в середине периода тактового сигнала. Поэтому приостановка происходит в любое время действия любой команды из набора команд микропроцессора. Микропроцессор прекращает выполнение программы, как только он распознает сигнал HOLD, и затем переходит к освобождению шины.

Следует отметить, что сигнал НОLD имеет более высокий приоритет, чем сигналы запроса на прерывание INTR и NМI.

Прерывания выполняются после завершения команды, тогда как сигнал НОLD оказывает действие в процессе выполнения команды. Единственный сигнал, имеющий приоритет выше приоритета сигнала НОLD, — это сигнал сброса RESET. Кроме того, следует обратить внимание на то, что сигнал НОLD не может быть активирован во время действия сигнала RESЕТ, иначе выполнение сброса не гарантируется.

Установка сигнала НLDA указывает на то, что микропроцессор отключился от системной шины. Следует обратить внимание, что за время от установки сигнала НОLD до установки сигнала НLDА происходят в течение нескольких периодов тактовых импульсов.

Установка сигнала НLDА является для внешнего устройства, запра-

шивающего шину признаком того, что микропроцессор уступил управление памятью и пространством ввода-вывода. Таким образом, сигнал НОLD можно назвать сигналом запроса ПДП, а сигнал HLDA — сигналом предоставления ПДП.

Основные операции

Обмен данными без использования микропроцессора с помощью прямого доступа к памяти обычно осуществляется между устройством ввода-вывода и памятью.

При выполнении процедуры DМА по команде чтения осуществляется операция передачи данных из памяти в устройство ввода-вывода, а по команде записи осуществляется обратная операция передачи данных, т.е. из устройства ввода-вывода в память. В обеих операциях управление памятью и устройством ввода-вывода осуществляется одновременно, и поэтому для них в системе имеются отдельные сигналы управления для чтения и записи.

Такая специальная структура сигналов шины управления позволяет осуществлять обмен информацией с помощью прямого доступа к памяти.

При выполнении процедуры DМА и операции чтения для передачи данных из памяти в устройство ввода-вывода одновременно активизируются сигналы МЕМR. (МRDC) и IOW (IOWC), а при операции записи активизируются сигналы МЕМW (МWTС) и IOR. (IORС). Такие сигналы шины управления имеются во всех системах на микропроцессорах семейства Intel. В частности, для микропроцессоров 8086/8088 необходимо сформировать эти сигналы или с помощью контроллера шины, или с помощью схемы, приведенной на рис. 1.2.

При обмене с помощью прямого доступа к памяти контроллер DМА для обращения к памяти формирует адрес, а установив сигнал DАСК (DМА аcknowledge), выбирает устройство ввода-вывода.