- •Лабораторная работа № 5 Наименование работы

- •Цель работы

- •Задание к лабораторной работе

- •Перечень используемого оборудования и по

- •Краткие теоретические сведения Определение.

- •Математическая модель дешифратора

- •Способы построения дешифраторов

- •Дешифраторы адреса

- •Дешифратор кода операции

- •Применение дешифраторов в схемах управления

- •Мультиплексоры

- •Требования безопасности труда

- •Порядок проведения работы

- •Пример разработкиVhdl модели дешифратора

- •Содержание отчета

- •Контрольные вопросы

- •Список литературы

Лабораторная работа № 5 Наименование работы

Разработка VHDL моделей дешифраторов и мультиплексоров

Цель работы

1. Изучить методы дешифрации, применяемые в цифровых системах;

2. Изучить особенности применения дешифраторов в вычислительных машинах (дешифратор адреса, дешифратор кода операции)

3. Изучить особенности схемотехники мультиплексоров

Задание к лабораторной работе

1. Выберите способ дешифрации и разработайте VHDL модель адресного дешифратора для выделения в адресном пространстве следующих областей

Вариант Регистр Константы ОЗУ Периферийное устройство

1 00 20-25 80-EF F0

2 01 25-2A 90-EF F1

3 02 2B-31 A0-EF F2

4 03 32-38 B0-EF F3

5 04 39-40 C0-EF F4

6 05 41-47 D0-EF F5

7 06 48-4D 80-A0 F6

8 07 4E-5A 90-B0 F7

9 08 5B-60 A0-D0 F8

10 09 61-66 80-B0 F9

11 0A 67-7A 90-DO FA

12 0B 7B-7F A0-E0 FB

2. Разработайте VHDL модель дешифратора кода команды для микроконтроллера

Z80 /4/.

№ Команда Код Операция

1 ADD A,r 11000rrr A ← A + r

2 ADC A,n 11000110 A ← A + n + СY

3 SUB s 00010000 A ← A - s

4 SBC A,s 00011000 A ← A – s - CY

5 AND s 00100000 A ← A ∩ s

6 OR s 00110000 A ← A U s

7 XOR s 00101000 A ← A●s

8 INC r 00rrr100 r ← r + 1

9 CPL 00101111 A ← not A

10 NEG 11101101 A ← 0 - A

11 DEC r 11111101 r ← r - 1

12 SET b,r 11001011 rb ← 1

3. Разработайте VHDLмодель мультиплексоров

№ Микросхема

1 155 КП5

2 176 ЛС1

3 155 КП5

4 155 КП1

5 555 КП2

6 555 КП7

7 555 КП16

8 561 ЛС2

9 564 ИК1

10 555 КП11

11 555 КП12

12 555 КП15

4. Для приведенных заданий следует разработать набор тестовых сигналов и рассчитать коэффициенты управляемости и наблюдаемости.

5. Для выполнения лабораторной работы следует использовать приложение GHDLв ОСWindows.

Перечень используемого оборудования и по

1. Разработка VHDLмодели цифровой системы должна проводиться в средеGHDL.

2. VHDLмодель цифровой системы должна быть верифицирована в средеGHDL.

3. Для валидации VHDLмодели цифровой системы необходимо использовать целевое устройство - лабораторный макетFLEX8000 (target).

4. Для визуального контроля за формой сигнала и оценки временных параметров необходимо использовать аналоговый осциллограф С1-93.

5. Разработка VHDLмодели цифровой системы должна проводиться наIBMсовместимых ПК с использованием операционной системыWindowsXP(host PC).

6. Отчет по лабораторной работе оформляется в OpenOffice.

7. Принципиальная схема устройства составляется в KiCAD.

Краткие теоретические сведения Определение.

Адресное пространство представляет собой упорядоченное множество кодов 0, 1, 2,…, (2n-1), где n – число адресных линий.

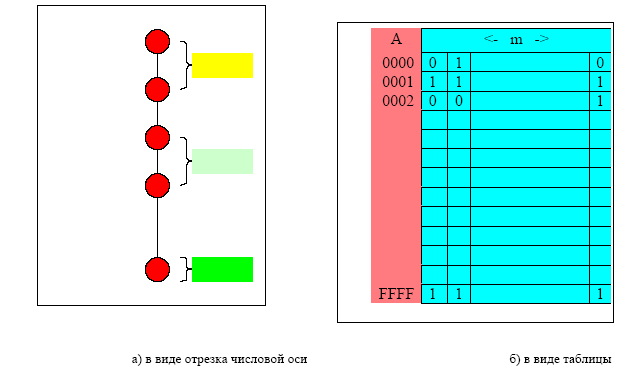

Представим адресное пространство в виде отрезка числовой оси либо в виде

таблицы (см. рис.1 а) и б) соответственно).

Нумерация точек, или «ячеек» адресного пространства при его графическом

представлении производится снизу вверх или сверху вниз (что удобнее) в десятичной,

восьмеричной или шестнадцатеричной форме.

Адресное пространство определяет число возможных отличных друг от друга

кодовых комбинации (адресов), которое может выдать на адресную шину активное

устройство.

Соответственно, старший двоичный разряд адреса делит адресное пространство на

две равные части, два старших разряда делят его на четыре равные части. Шестнадцать

разрядов адреса делят адресное пространство емкостью 64К на 64К частей по одной

ячейке.

Понятие адресного пространства позволяет наглядно представлять размещение в

нем различных программно-доступных объектов: областей памяти, таймеров, портов и т.д.

|

|

|

Рис.1. Изображение адресного пространства (m – разрядность шины данных) |