- •Лабораторная работа № 10

- •Наименование работы

- •Исследование последовательностных схем

- •Цель работы

- •Задание к лабораторной работе

- •Варианты заданий

- •Перечень используемого оборудования Краткие теоретические сведения

- •Основная модель асинхронного потенциального автомата

- •Пример последовательностной схемы

- •Разработка vhdl модели последовательностных схем

- •Порядок проведения работы

- •Содержание отчета

- •Контрольные вопросы

- •Список литературы

- •Приложение 1 Варианты последовательностных схем

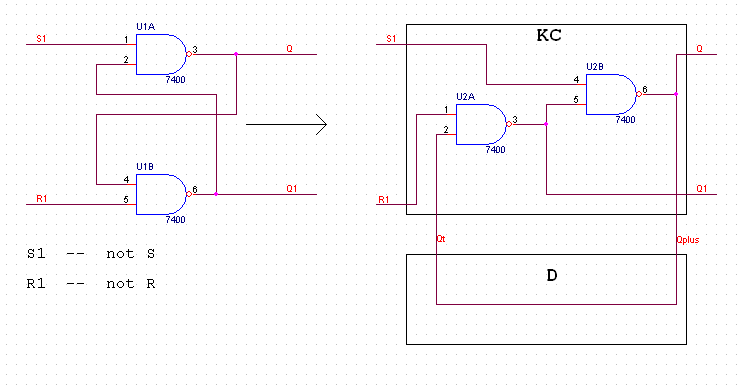

Пример последовательностной схемы

Рассмотрим в качестве примера R-S триггер

|

|

|

Рис.2. Преобразование функциональной схемы R-S триггера |

Приведем таблицу истинности для схемы рис.2.

|

Входы |

Выход |

Примечание |

||||

|

R |

S |

Q |

Q+ |

|

||

|

0 |

0 |

0 |

0 |

Сохранение |

||

|

0 |

0 |

1 |

1 |

Сохранение |

||

|

0 |

1 |

0 |

1 |

Изменение |

||

|

0 |

1 |

1 |

1 |

Сохранение |

||

|

1 |

0 |

0 |

0 |

Сохранение |

||

|

1 |

0 |

1 |

0 |

Изменение |

||

|

1 |

1 |

0 |

XX |

Запрещено |

||

|

1 |

1 |

1 |

XX |

Запрещено |

||

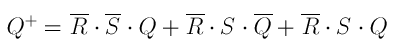

С учетом введенных обозначений математическая модель ЭП типа R-S имеет вид

|

|

После упрощения имеем

Для реализации ЭП типа R-S в базисе И-НЕ представим первое соотношение в виде

Второе соотношение определяет запрещенную комбинацию входных сигналов (R=1, S=1)

Разработка vhdl модели последовательностных схем

При

разработке VHDL

моделей последовательностных схем

задержка на

моделируется оператором wait,

который обеспечивает прекращение

оператора процесса или процедуры после

истечения времени, указанного в параметрах

оператора.

моделируется оператором wait,

который обеспечивает прекращение

оператора процесса или процедуры после

истечения времени, указанного в параметрах

оператора.

Определение

wait_statement :: = wait [sensitivity_clause]

[condition_clause];

[timeout_clause];

sensitivity_clause :: = on sensitivity_list

condition_clause :: = until Boolean_expression

timeout_clause :: = for time_expression.

Sensitivity_list список чувствительности.

Примеры оператора wait:

wait for 10 ns; -- ждем 10 ns

wait until clk=’1’; -- ждем сигнала clk равного 1

wait on clk; -- ждем активности сигнала clk

Порядок проведения работы

1. Подготовка к выполнению лабораторной работы.

Разработка VHDL моделей дешифраторов и мультиплексоров и их верификация должны быть проведены в среде OrCAD (host PC)

Выполнение лабораторной работы проводится в аудитории под контролем преподавателя.

Перед выполнением лабораторной работы необходимо проверить наличие защитного заземления, исправность схем аварийного отключения питания.

2. Порядок выполнения лабораторной работы:

- в соответствии с разработанной принципиальной электрической схемой, выполнить необходимые коммутации на макетной плате FLEX8000 (target);

- подсоединить к контрольным точкам щупы осциллографа;

- включить питание (подсоединить FLEX8000 к удлинителю USB);

- при правильном соединении загорается светодиод HL1;

- при возникновении проблем с соединением необходимо обратиться к преподавателю;

- сконфигурировать ПЛИС FLEX8000 в среде MAX PLUS (Host PC + target);

- наблюдать временные диаграммы в контрольных точках, обеспечивая синхронизацию органами управления осциллографа;

- при несоответствии наблюдаемых осциллограмм заданию, необходимо повторить синтез VHDL моделей схем с учетом отмеченных недостатков; затем необходимо провести верификацию VHDL модели. Внесенные изменения необходимо согласовать с преподавателем и повторить валидацию VHDL модели (Host PC);

- скопировать временные диаграммы с экрана осциллографа.