Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4 по дисциплине «Электроника и схемотехника»

вариант № 17

Студент гр.

..2022

Руководитель

..2022

Томск 2022

Введение

Целью данной работы является изучение основных типов триггеров, их принципов построения и работы.

Поставленные задачи:

1. Составить таблицы функционирования для схем согласно варианту.

Таблица 1 – Задание по варианту

Тип |

Триггер |

Базис |

|

|

|

S1 |

RS |

И-НЕ |

|

|

|

S2 |

Т |

ИЛИ-НЕ |

|

|

|

d |

D |

ИЛИ-НЕ |

|

|

|

2.Собрать схемы на холстах bdf. согласно варианту.

3.Промоделировать работу всех схем в двух режимах: Timing и

Functional. Сравнить результаты моделирования с составленными таблицами

истинности.

4. Описать устройства, используя заданный вариантом HDL.

Вариант HDL: System Varilog.

2

1ОДНОСТУПЕНЧАТЫЙ RS-ТРИГГЕР НА БАЗИСЕ И-НЕ

1.1Таблица истинности

Втаблице 1.1 представлена таблица функционирования триггера s1-RS

Таблица 1.1 – Таблица функционирования триггера s1-RS

Одноступенчатый RS

|

Входы |

|

Выходы |

Переход |

Режим работы |

|

|

|

|

|

|

|

|

С |

R |

S |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

0 1 |

установка в 1 |

|

|

|

|

|

|

|

0 |

X |

X |

1 |

1 |

1 1 |

хранение |

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

0 |

1 0 |

установка в 0 |

|

|

|

|

|

|

|

0 |

X |

X |

1 |

0 |

0 0 |

хранение |

|

|

|

|

|

|

|

1.2 Функциональная схема

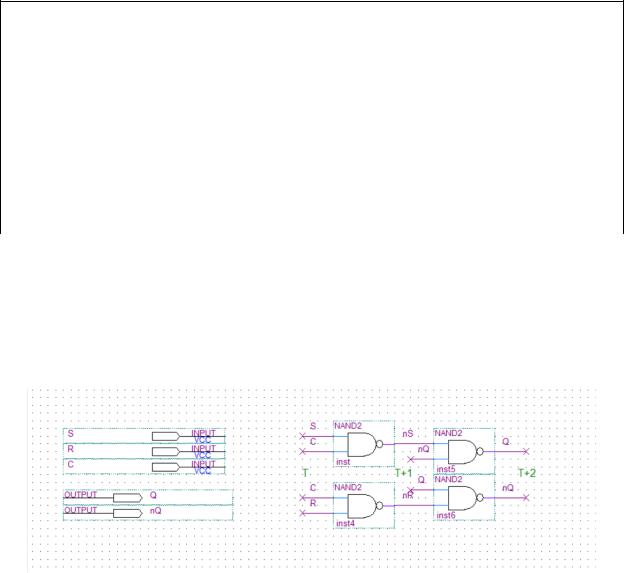

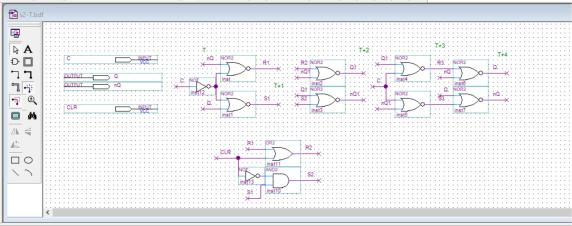

На рисунке 1.2.1 представлена функциональная схема s1-RS.

Рисунок 1.2.1 - схема s1-RS

1.3 Формула

Ниже представлены формулы для схемы s1-RS на базисе И-НЕ:

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

Q(t + 2) = S(t + 1) Q(t + 1)

̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

Q(t + 2) = R(t + 1) Q(t + 1)

3

̅ |

̅̅̅̅̅̅̅̅̅̅̅̅ |

S(t + 1) = S(t) C(t) |

|

̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅ |

R(t + 1) = R(t) C(t)

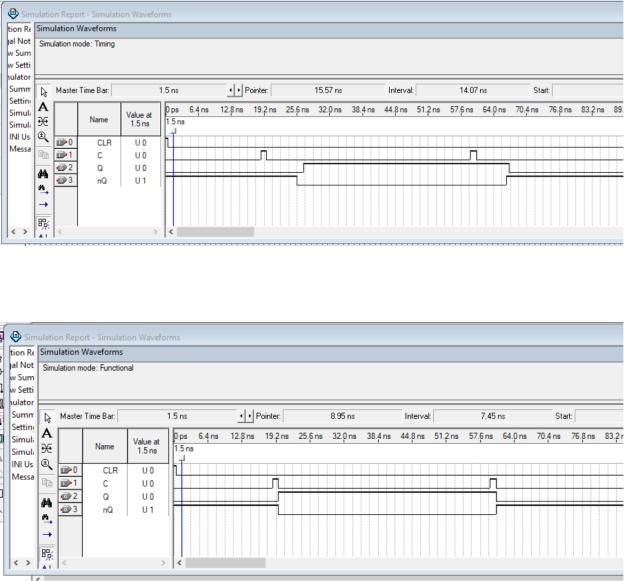

1.4 Моделирование функциональной схемы

На рисунке 1.4.1 представлен результат моделирования в режиме

Timing.

Рисунок 1.4.1 – Результат моделирования s1-RS в режиме Timing

На рисунке 1.4.2 представлен результат моделирования в режиме

Functional.

Рисунок 1.4.2 - Результат моделирования s1-RS в режиме Functional

4

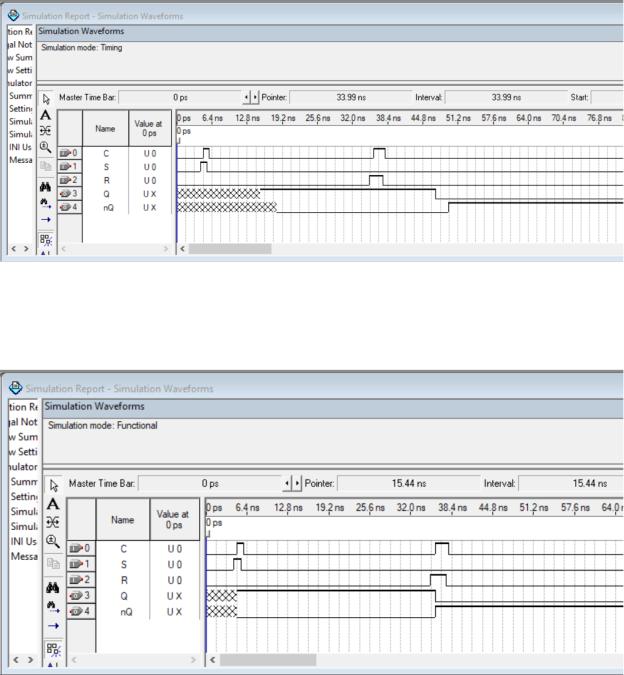

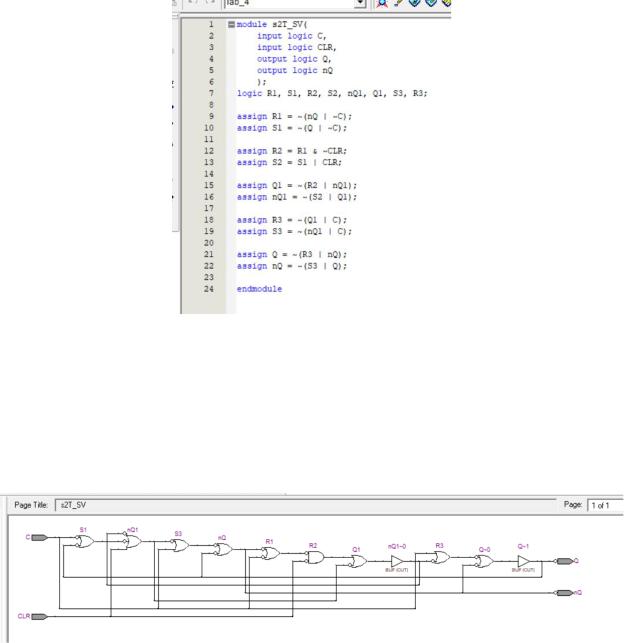

1.5 Код на HDL

На рисунке 1.5.1 представлен код описания s1-RS на System Verilog.

Рисунок 1.5.1 – Код описания s1-RS на SV

1.6 Схема из RTL Viewer для кода на HDL

На рисунке 1.6.1 представлена схема из RTL viewer для кода,

написанного на SV.

Рисунок 1.6.1 – Схема из RTL viewer для кода s1-RS

1.7 Моделирование устройства, описанного кодом HDL

На рисунках 1.7.1 и 1.7.2 – представлен результат моделирования s1-RS,

описанного на SV.

5

Рисунок 1.7.1 – Результат моделирования s1-RS в режиме Timing.

Рисунок 1.7.2 – Результат моделирования s1-RS в режиме Functional

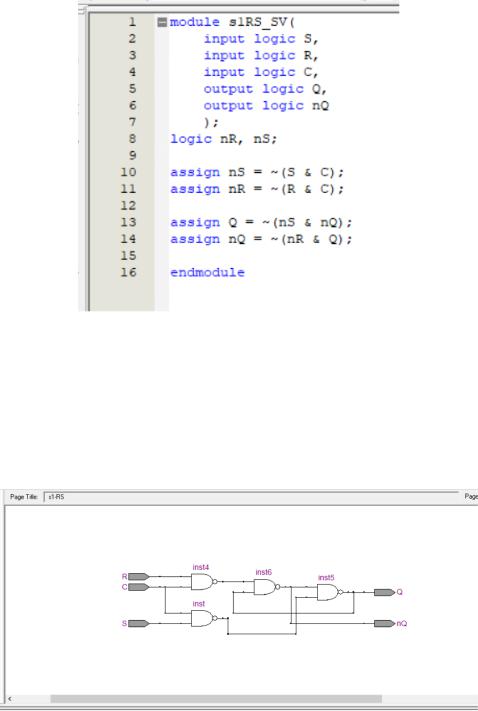

1.8 Исследование минимального порога длительности активного

уровня управляющего сигнала

На рисунке 1.8.1 представлен результат моделирования s1-RS при длительности активного уровня сигнала С = 1,1 нс.

Рисунок 1.8.1 – Моделирование при С = 1.1

6

На рисунке 1.8.2 представлен результат моделирования s1-RS при длительности активного уровня С = 1 нс.

Рисунок 1.8.2 – Моделирование при С = 1

Как можно наблюдать из рисунков 1.8.2 длины сигнала в 1 нс не хватает,

для корректной работы s1-RS.

2 ДВУХСТУПЕНЧАТЫЙ Т-ТРИГГЕР НА БАЗИСЕ ИЛИ-НЕ

2.1Таблица истинности

Втаблице 2.1 представлена таблица функционирования s2-T.

Таблица 2.1 – Таблица функционирования s2-T

Двухступенчатый

Вход |

Выходы |

Переход |

Режим работы |

|

|

|

|

|

|

С |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

|

1 |

0 |

1 |

0 1 |

счётный из 0 в 1 |

|

|

|

|

|

0 |

1 |

1 |

1 1 |

хранение |

|

|

|

|

|

1 |

1 |

0 |

1 0 |

счетный из 1 в 0 |

|

|

|

|

|

0 |

0 |

0 |

0 0 |

хранение |

|

|

|

|

|

2.2 Функциональная схема

На рисунке 2.2.1 – представлена функциональная схема s2-T.

7

Рисунок 2.2.1 – Схема s2-T

2.3 Формула

Ниже представлены формулы схемы для s2-T на базисе ИЛИ-НЕ:

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

Q(t + 4) = R3(t + 3) Q(t + 3) |

||

̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

Q(t + 4) = S3(t + 3) Q(t + 3) |

||

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

R3(t + 3) = Q1(t + 2) C(t + 2) |

||

|

̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

S3(t + 3) = Q̅̅1(t + 2) C(t + 2) |

||

Q |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅ |

|

(t + 2) = |

(t + 1) Q̅̅ (t + 1) |

|

1 |

2 |

1 |

̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

̅̅ |

|

Q1 |

(t + 2) = 2(t + 1) Q1(t + 1) |

|

|

2(t + 1) |

̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

= Q(t) C( ) |

|

|

2(t + 1) |

̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

= Q(t) C( ) |

|

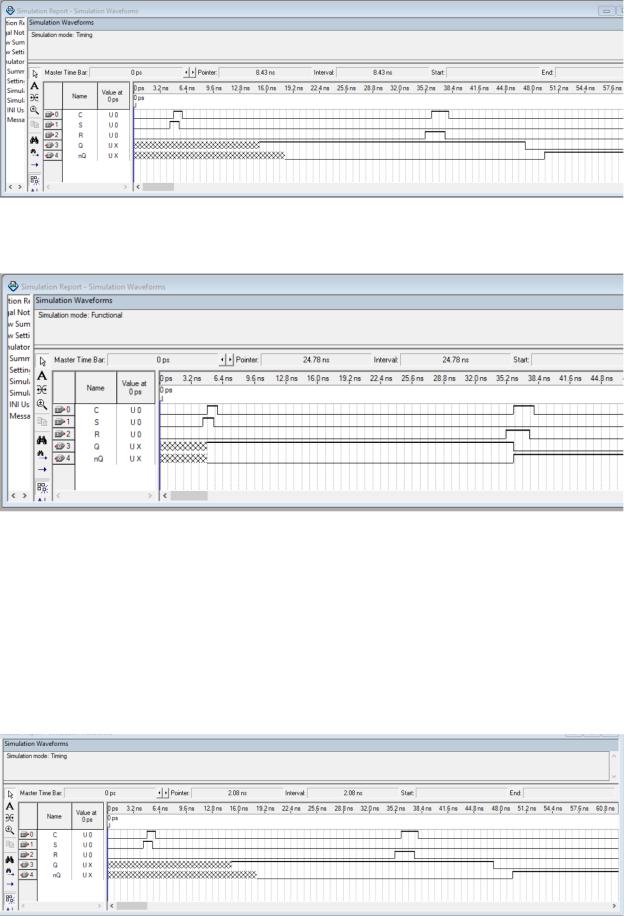

2.4 Моделирование функциональной схемы

На рисунках 2.4.1 и 2.4.2 представлены результаты моделирования s2-T

в двух режимах.

8

Рисунок 2.4.1 – Результат моделирования s2-T в режиме (Timing)

Рисунок 2.4.2 – Результат моделирования s2-T в режиме (Functional)

Результат моделирования совпадает со значениями из таблицы функционирования, представленной в таблице 2.1.

2.5 Код на HDL

На рисунке 2.5.1 представлен код описания s2-T на SV

9

Рисунок 2.5.1 – Код описания s2-T на SV

2.6 Схема из RTL viewer для кода HDL

На рисунке 2.6.1 представлена схема из RTL viewer для кода,

написанного на SV. Схема соответствует функциональной схеме.

Рисунок 2.6.1 – Схема из RTL viewer для кода 2s-T

2.7 Моделирование устройства, описанного кодом HDL

На рисунках 2.7.1 и 2.7.2 представлены результаты моделирования 2s-T,

описанного на SV, в двух режимах.

10