Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1

по дисциплине «Электроника и схемотехника»

вариант № 17

Студент гр.

__.__.2022

Руководитель

__.__.2022

Томск 2022

Введение

Цель работы: целью данной работы является изучение основных инструментов САПР QuartusII и получение навыков моделирования в ней работы схем на основе простых логических элементов.

Задачи:

1)Собрать на холсте программы Quartus схемы 2И, 2ИЛИ, 2искл.ИЛИ, 2И-НЕ и 2ИЛИ-НЕ, а также описать элементы на VHDL и

промоделировать работы схем.

2)Собрать на холсте программы Quartus схему, для выражения, заданного по варианту №17, после чего описать элементы на VHDL и

промоделировать работоспособность схемы.

2

1 УСТРОЙСТВО « 2И »

1.1 Таблица истинности Для данного устройства «2И» была создана таблица истинности, которая

представлена ниже. Данное устройство имеет два входа, а именно: (input) x1 и x2, а также один выход (output) y.

Таблица 1.1.1 - Таблица истинности для устройства "2И"

x1 |

x2 |

y |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1.2 Формула Ниже представлена формула, для описания устройства «2И» Формула имеет следующий вид : y = x1 x2

1.3 Функциональная схема Функциональная схема для данного устройства «2И» была разработана

в программе Quartus, изображение схемы можно наблюдать на рисунке 1.3.1.

Рисунок 1.2.1 – Функциональная схема устройства «2И»

3

Как было описано в пункте 1.1, данное устройство имеет два входа: x1 и x2, а также один выход y. Так как данная схема работает по принципу 2И,

можно наблюдать следующее: если на вход в данное устройство подается хотя бы один логический 0, то на выходе мы будем иметь 0, 1 будет подаваться на выход только в том случае, когда на обеих входах будет поданы 1.

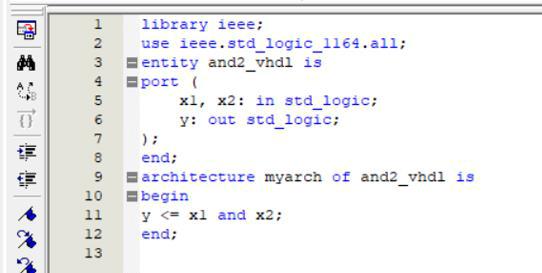

1.4 Код на VHDL

Для данного устройства был написан код на VHDL, который представлен ниже, на рисунке 1.4.1.

Рисунок 1.4.1 – Код на VHDL устройства «2И»

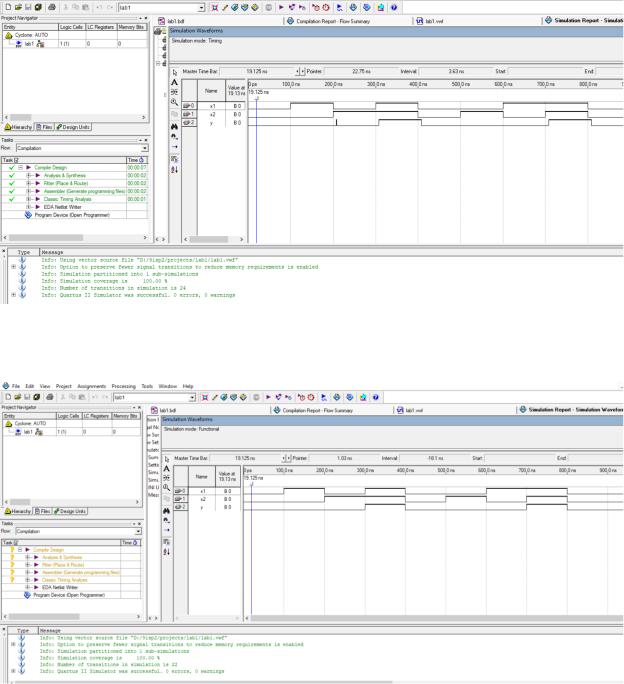

1.5 Моделирование Ниже, на рисунках 1.5.1 и 1.5.2 представлены изображения

моделирования устройства «2И» для функциональной схемы в двух режимах,

а именно Timing и Functional, после чего представлено моделирование того же устройства, но для кода VHDL, в тех же двух режимах работы, моделирование для кода VHDL представлено на рисунках 1.5.3 и 1.5.4.

4

Рисунок 1.5.1 – Моделирование в режиме Timing

Рисунок 1.5.2 – Моделирование в режиме Functional

Далее представлено моделирование для кода VHDL.

5

Рисунок 1.5.3 – Моделирование в режиме Timing

Рисунок 1.5.4 - Моделирование в режиме Functional

Как можно наблюдать из рисунков 1.5.1, 1.5.2, 1.5.3 и 1.5.4

моделирование в режиме Timing и Functional связано это с тем, что логические элементы и входы расположены на разном расстоянии, в следствии чего, в

режиме Timing можно заметить ситуацию, при которой один сигнал успевает поменять значение с 1 на 0, в то время как второй сигнал всё ещё принимает значение 1.

Как можно наблюдать из данных рисунков, моделирования отображают

таблицу истинности, что доказывает верность выполненной работы.

6

2 УСТРОЙСТВО «2ИЛИ»

2.1 Таблица истинности Ниже приведена таблица истинности, для устройства «2ИЛИ». Данной

устройство также, как и предыдущее имеет два входа и один выход.

Таблица 2.1 - таблица истинности для устройства "2ИЛИ"

x1 |

x2 |

y |

|

|

|

0 |

0 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

1 |

|

|

|

2.2 Формула

Ниже представлена формула для устройства «2ИЛИ» Формула имеет следующий вид: y = x1 x2

2.3 Функциональная схема Функциональная схема для данного устройства «2ИЛИ» была

разработана в программе Quartus, изображение схемы можно наблюдать на рисунке 2.3.1.

Рисунок 2.3.1 – Функциональная схема устройства «2ИЛИ»

7

Для данной схемы устройства, как можно наблюдать из пункта 2.1,

достаточно подать на вход хотя бы одну 1, чтобы получить на выходе 1, в

случае когда на обеих входах х1 и х2 будут 0, на выходе будет подан 0.

2.4 Код на VHDL

Ниже, на рисунке 2.4.1 представлено изображение кода для VHDL, для устройства «2ИЛИ»

Рисунок 2.4.1 – Устройство «2ИЛИ» на языке описания аппаратуры

2.5 Моделирование

Ниже, на рисунках 2.5.1 и 2.5.2 представлено моделирование устройства

«2ИЛИ» для функциональной схемы. Для рисунка 2.5.1 это моделирование в режиме Timing, для рисунка 2.5.2 моделирование в режиме functional.

Рисунок 2.5.1 – Моделирование режиме Timing 8

Рисунок 2.5.2 – Моделирование в режиме Functional

Ниже, на рисунках 2.5.3 и 2.5.4 представлено моделирование для

VHDL.

Рисунок 2.5.3 – Моделирование в режиме Functional

Рисунок 2.5.4 – Моделирование в режиме Timing 9

3 УСТРОЙСТВО «2ИСКЛ.ИЛИ»

3.1 Таблица истинности Ниже, приведена таблица 3.1.1, таблица истинности для данного

устройства.

Таблица 3.1.1 - таблица истинности для устройства "2ИСКЛ.ИЛИ"

x1 |

x2 |

y |

|

|

|

0 |

0 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

3.2 Формула Ниже представлена формула для устройства «2ИСКЛ.ИЛИ» Формула имеет следующий вид: y = x1 x2

3.3 Функциональная схема На рисунке 3.3.1 представлена функциональная схема устройства

«2ИСКЛ.ИЛИ» Для данного устройства также имеется 2 входа и 1 выход, при этом, единицу на выходе мы можем получить только в таком случае, когда на входе мы имеем

Рисунок 3.3.1 – Функциональная схема устройства «2ИСКЛ.ИЛИ»

10