Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ РЕГИСТРОВ И СЧЁТЧИКОВ

Отчет по лабораторной работе №7

по дисциплине «Электроника и схемотехника» вариант № 17

Студент гр.

Руководитель

..2022

Томск 2022

Введение

Цель работы – овладеть навыками совместного применения регистров и счётчиков.

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1. Составить таблицу истинности для функций, представленных ниже

====

2. Собрать схему, используя встроенные блоки регистров, для выполнения 4-х параллельных операций полубайтом. Организовать приём и выдачу данных согласно варианту, который указан на рисунке 1.

Рисунок 1 – Вариант задания

3.Спроектировать схемы, которые с помощью регистров обеспечат «чистый» выходной сигнал для асинхронных счётчиков из лабораторной работы №5

4.Промоделировать работу всех схем в двух режимах: Timing и

Functional, а также сравнить результаты моделирования с составленными таблицами истинности.

5. Используя заданный вариантом язык описания аппаратуры, описать и промоделировать устройства. Вариант: VHDL.

2

1 ВЫЧИСЛИТЕЛЬ ФУНКЦИИ

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности для вычисляемых функций.

Таблица 1.1 – Таблица истинности для вычисляемых функций

|

|

Входы |

|

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

|

|

X |

Y |

|

Z |

W |

F18 |

F17 |

|

F16 |

F15 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

1 |

1 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

1 |

1 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

1 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

1.2 Функциональная схема

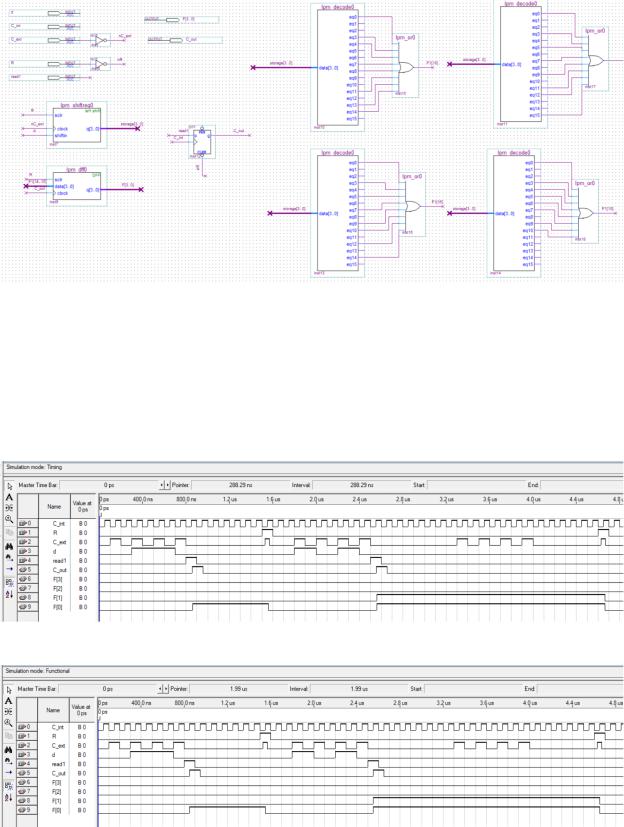

На рисунке 1.2.1 представлена функциональная схема для вычислителя

функций.

3

Рисунок 1.2.1 – Функциональная схема для вычислителя функций

1.3 Моделирование функциональной схемы

На рисунках 1.3.1 и 1.3.2 представлено моделирование функциональной схемы, в двух режимах работы.

Рисунок 1.3.1 – Моделирование в режиме Timing

Рисунок 1.3.2 – Моделирование в режиме Functional

4

1.4 Код на HDL

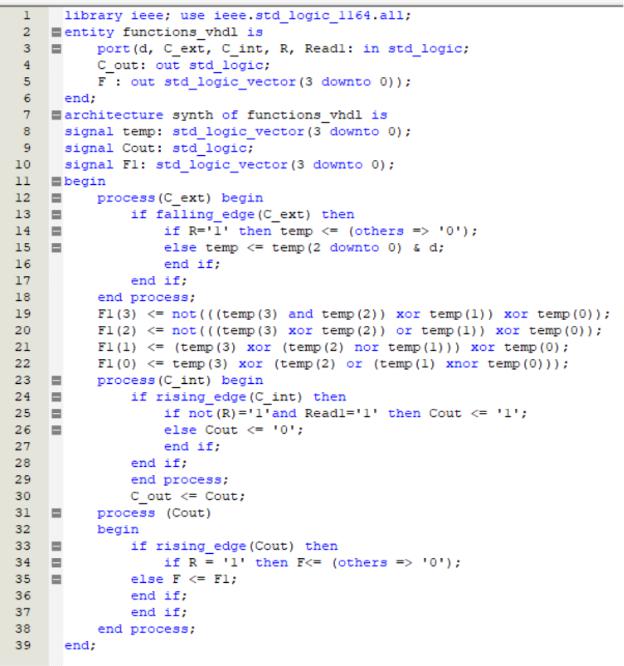

На рисунке 1.4.1 представлено изображение кода описания устройства на VHDL.

Рисунок 1.4.1 – Код описания устройства на VHDL

1.5 Схема из RTL viewer для кода на HDL

На рисунке 1.5.1 представлена схема из RTL для кода, написанного на

VHDL.

5

Рисунок 1.5.1 – Схема из RTL viewer для кода на VHDL

1.6 Моделирование устройства, описанного кодом HDL

На рисунке 1.6.1 представлено моделирование устройства, описанного кодом VHDL, в двух режимах работы Timing и Functional.

Рисунок 1.6.1 – Моделирование в режиме Timing

Рисунок 1.6.2 – Моделирование в режиме Functional

6

2 АСИНХРОННЫЙ СЧЁТЧИК С ВЫХОДНЫМ БУФЕРОМ

2.1 Таблица истинности

В таблице 2.1 представлена таблица истинности асинхронного счётчика.

Таблица 2.1 – Таблица истинности для асинхронного счётчика

№ сигнала |

Выходы |

|

|

|

|

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

1 |

1 |

1 |

1 |

16 |

1 |

0 |

0 |

0 |

0 |

17 |

1 |

0 |

0 |

0 |

1 |

18 |

1 |

0 |

0 |

1 |

0 |

19 |

1 |

0 |

0 |

1 |

1 |

20 |

1 |

0 |

1 |

0 |

0 |

21 |

1 |

0 |

1 |

0 |

1 |

22 |

1 |

0 |

1 |

1 |

0 |

23 |

1 |

0 |

1 |

1 |

1 |

24 |

1 |

1 |

0 |

0 |

0 |

25 |

1 |

1 |

0 |

0 |

1 |

26 |

1 |

1 |

0 |

1 |

0 |

27 |

1 |

1 |

0 |

1 |

1 |

28 |

1 |

1 |

1 |

0 |

0 |

29 |

1 |

1 |

1 |

0 |

1 |

30 |

0 |

0 |

0 |

0 |

0 |

31 |

0 |

0 |

0 |

0 |

1 |

32 |

0 |

0 |

0 |

1 |

0 |

7

2.2 Функциональная схема

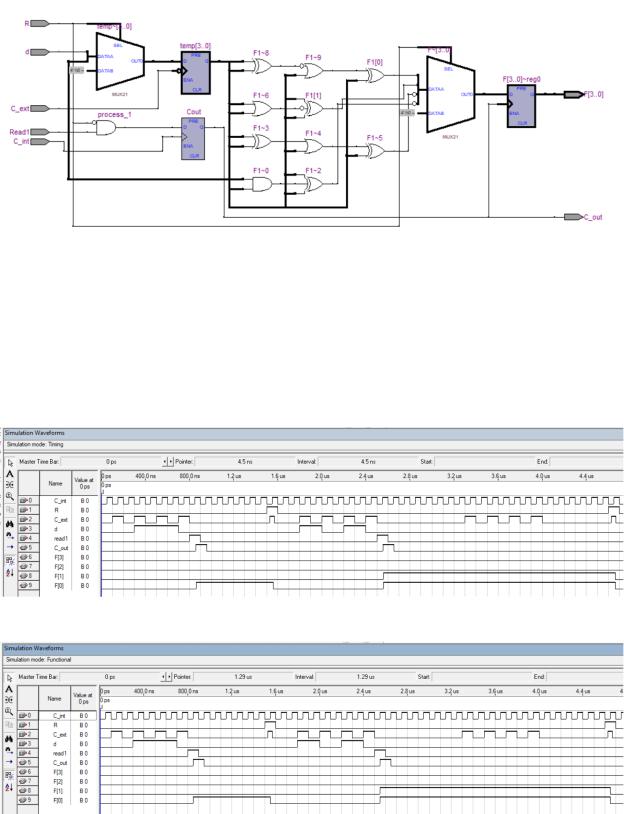

На рисунке 2.2.1 представлено изображение функциональной схемы асинхронного счётчика.

Рисунок 2.2.1 – Функциональная схема асинхронного счётчика

2.3 Моделирование функциональной схемы

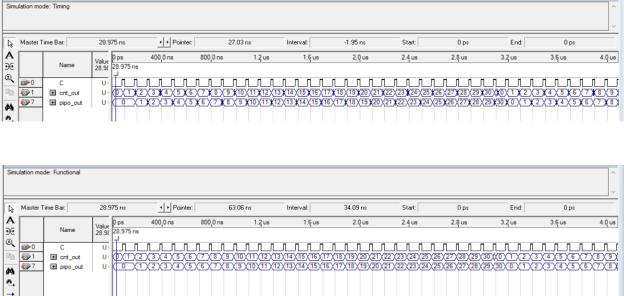

На рисунке 2.3.1 и 2.3.2 представлено моделирование функциональной схемы асинхронного счётчика, в двух режимах работы.

Рисунок 2.3.1 – Моделирование в режиме Timing

Рисунок 2.3.2 – Моделирование в режиме Functional

2.4 Код на HDL

На рисунке 2.4.1 представлен код описания устройства на VHDL. 8

Рисунок 2.4.1 – Код описания устройства на VHDL

2.5 Схема из RTL viewer для кода на HDL

На рисунке 2.5.1 представлено изображение схемы из RTL viewer для кода на VHDL.

Рисунок 2.5.1 – Схема RTL viewer

2.6 Моделирование устройства, описанного кодом VHDL

На рисунках 2.6.1 и 2.6.2 представлено изображение моделирования асинхронного счётчика, описанного на VHDL, в двух режимах работы.

9

Рисунок 2.6.1 – Моделирование асинхронного счётчика в режиме Timing

Рисунок 2.6.2 – Моделирование асинхронного счётчика в режиме Functional

3 СИНХРОННЫЙ СЧЁТЧИК С ВЫХОДНЫМ БУФЕРОМ

3.1Таблица истинности

Втаблице 3.1 представлена таблица истинности, для синхронного счётчика с выходным буфером.

Таблица 3.1 – таблица истинности для синхронного счётчика

№ |

Вход |

Входы |

|

|

|

|

|

сигнала |

RP |

Q4 |

|

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

2 |

0 |

1 |

|

1 |

0 |

0 |

0 |

3 |

0 |

1 |

|

0 |

1 |

1 |

1 |

4 |

0 |

1 |

|

0 |

1 |

1 |

0 |

5 |

0 |

1 |

|

0 |

1 |

0 |

1 |

6 |

0 |

1 |

|

0 |

1 |

0 |

0 |

7 |

0 |

1 |

|

0 |

0 |

1 |

1 |

8 |

0 |

1 |

|

0 |

0 |

1 |

0 |

9 |

0 |

1 |

|

0 |

0 |

0 |

1 |

10 |

0 |

1 |

|

0 |

0 |

0 |

0 |

11 |

0 |

0 |

|

1 |

1 |

1 |

1 |

12 |

0 |

0 |

|

1 |

1 |

1 |

0 |

13 |

0 |

0 |

|

1 |

1 |

0 |

1 |

14 |

0 |

0 |

|

1 |

1 |

0 |

0 |

15 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

|

|

|

10 |

|

|

|