Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

Отчет по лабораторной работе №3

по дисциплине «Электроника и схемотехника» вариант № 17

Студент гр.

..2022

Руководитель

..2022

Томск 2022

Введение

Цель работы: научиться создавать мультиплексоры и демультиплексоры на разных базисах, а также реализовывать функцию на мультиплексоре и дешифраторе.

Постановка задачи:

1. Составьте таблицы истинности для схем из таблицы согласно варианту. Напишите формулы для всех выходов в СДНФ или СКНФ.

Приведите формулы к требуемому базису согласно варианту.

2.Соберите схемы согласно полученным формулам. Согласно варианту создайте блок большей размерности на основе полученного блока.

3.Создайте две схемы, которые реализуют функцию по формуле из варианта задания ЛБ1: одна схема на основе мультиплексора, а вторая схема на основе дешифратора.

4.Промоделируйте работу всех схем в двух режимах. Сделайте предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5.Сверьте результаты моделирования с составленными таблицами истинностями.

6.Повторите п. 2, только для описания устройств вместо схем на холстах

.bdf используйте заданный вариантом HDL. При масштабировании используйте модульное подключение.

Функция по варианту: F x y w z .

Таблица 1 – задание по варианту

|

MUX |

|

|

|

DMX |

|

|

|

|

|

|

|

|

тип |

базис |

Нарастить |

|

тип |

базис |

Нарастить |

|

|

до |

|

|

|

до |

|

|

|

|

|

|

|

8-1 |

И-НЕ |

16-1 |

|

1-4 |

И,ИЛИ,НЕ |

2-8 |

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

1 МУЛЬТИПЛЕКСОР 8-1

1.1 Таблица истинности

Таблица 2 – Таблица истинности мультиплексора 8-1

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

A2 |

A1 |

A0 |

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

B0 |

0 |

0 |

0 |

B0 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

B1 |

x |

0 |

0 |

1 |

B1 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

B2 |

x |

x |

0 |

1 |

0 |

B2 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

B3 |

x |

x |

x |

0 |

1 |

1 |

B3 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

B4 |

x |

x |

x |

x |

1 |

0 |

0 |

B4 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

B5 |

x |

x |

x |

x |

x |

1 |

0 |

1 |

B5 |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

B6 |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

B6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

B7 |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

B7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1.2 Формула

adr0 E x0 A2 A1 A0 adr1 E x1 A2 A1 A0 adr2 E x2 A2 A1 A0 adr3 E x3 A2 A1 A0 adr4 E x4 A2 A1 A0 adr5 E x5 A2 A1 A0 adr6 E x6 A2 A1 A0 adr7 E x7 A2 A1 A0

F adr0 adr1 adr2 adr3 adr4 adr5 adr6 adr7

3

1.3 Функциональная схема

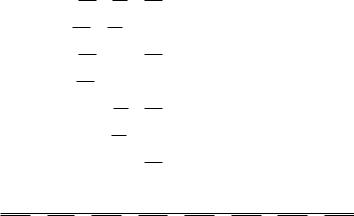

На рисунке 1.3.1 представлена функциональная схема мультиплексора 8-1.

Рисунок 1.3.1 – Функциональная схема мультиплексора 8-1

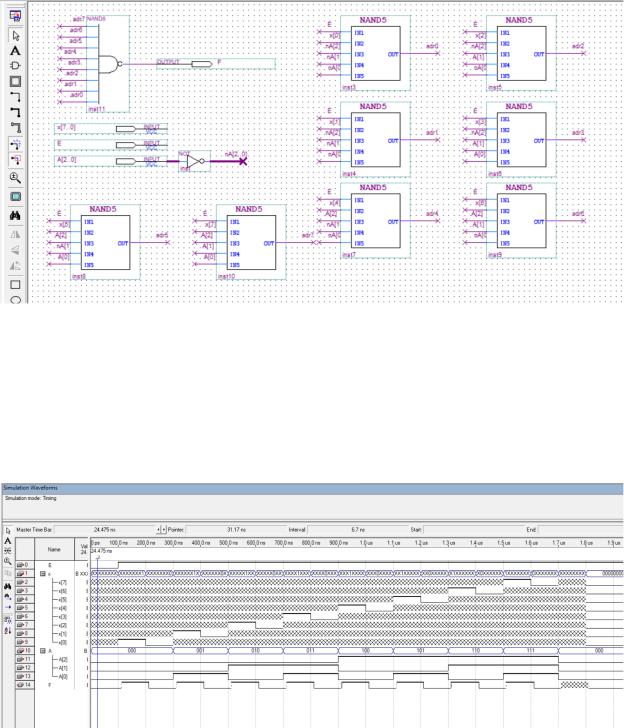

1.4 Моделирование

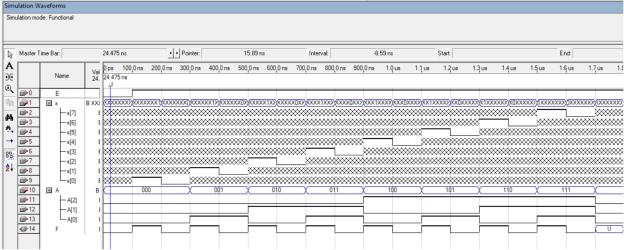

На рисунках 1.4.1 и 1.4.2 представлено моделирование схемы в режиме

Timing и Functional

Рисунок 1.4.1 – Результат моделирования мультиплексора 8-1 в режиме

Timing

Так как моделирование в режиме Timing приближено к реальности и

отображает задержки переключателя, из-за чего результат немного искажается от

идеального.

4

Рисунок 1.4.2 – Результат моделирования мультиплексора 8-1 в режиме

Functional

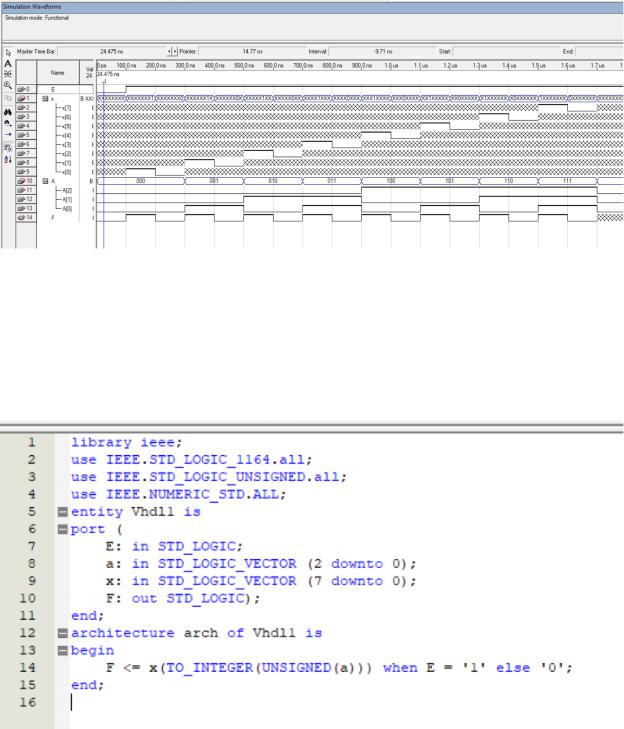

1.5 Код на HDL

На рисунке 1.5.1 представлен код представлен код схемы на VHDL.

Рисунок 1.5.1 - Код схемы

5

1.6 Схема из RTL viewer для кода HDL

Рисунок 1.6.1 – Схема из RTL viewer для кода HDL мультиплексора 8-1

1.7 Моделирование устройства, описанного кодом HDL

На рисунке 1.7.1 b 1.7.2 представлено моделирование устройства,

описанного на VHDL, в режиме Timing и Functional.

Рисунок 1.7.1 – Результат моделирования на VHDL мультиплексора 8-1 в

режиме Timing

6

Рисунок 1.7.2 – Результат моделирования на VHDL мультиплексора 8-1 в

режиме Functional

1.8Таблица истинности масштабируемого устройства

Втаблице 3 представлена таблица истинности масштабируемого устройства.

Таблица 3 -Таблица истинности масштабируемого мультиплексора 16-1

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|||||

E |

x |

x |

x |

x |

x |

x |

x9 |

x8 |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

A3 |

A2 |

A1 |

A0 |

F |

15 |

14 |

13 |

12 |

11 |

10 |

||||||||||||||||

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B0 |

0 |

0 |

0 |

0 |

B0 |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B1 |

x |

0 |

0 |

0 |

1 |

B1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B2 |

x |

x |

0 |

0 |

1 |

0 |

B2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B3 |

x |

x |

x |

0 |

0 |

1 |

1 |

B3 |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B4 |

x |

x |

x |

x |

0 |

1 |

0 |

0 |

B4 |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B5 |

x |

x |

x |

x |

x |

0 |

1 |

0 |

1 |

B5 |

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B6 |

x |

x |

x |

x |

x |

x |

0 |

1 |

1 |

0 |

B6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

x |

B7 |

x |

x |

x |

x |

x |

x |

x |

0 |

1 |

1 |

1 |

B7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

x |

x |

B8 |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

0 |

0 |

0 |

B8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

||||

1 |

x |

x |

x |

x |

x |

x |

B9 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

0 |

0 |

1 |

B9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

x |

x |

x |

x |

x |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

0 |

1 |

0 |

B10 |

10 |

|||||||||||||||||||||

1 |

x |

x |

x |

x |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

0 |

1 |

1 |

B11 |

11 |

|||||||||||||||||||||

1 |

x |

x |

x |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

0 |

B12 |

12 |

|||||||||||||||||||||

1 |

x |

x |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

0 |

1 |

B13 |

13 |

|||||||||||||||||||||

1 |

x |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

0 |

B14 |

14 |

|||||||||||||||||||||

1 |

B |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

1 |

1 |

1 |

1 |

B15 |

15 |

|||||||||||||||||||||

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

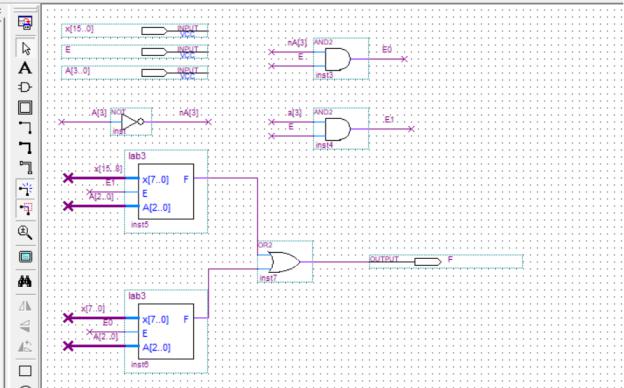

1.9 Функциональная схема масштабируемого устройства

На рисунке 1.9.1 представлена схема масштабируемого устройства

мультиплексора 16-1.

Рисунок 1.9.1 – Функциональная схема масштабируемого мультиплексора

16-1

8

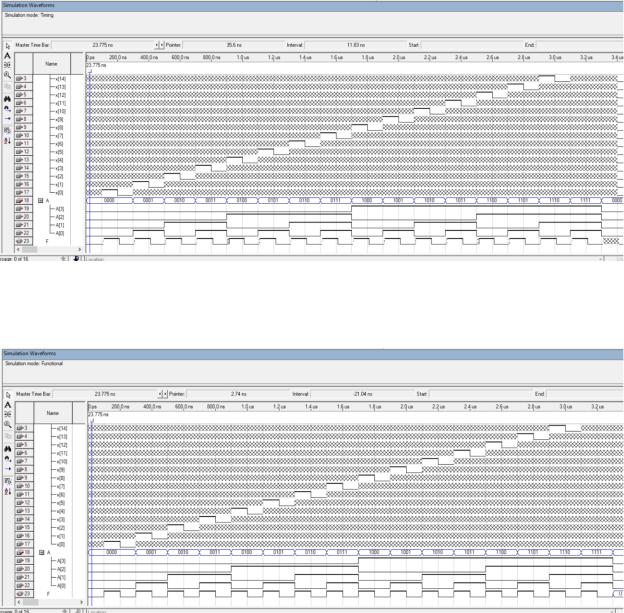

1.10 Моделирование масштабируемого устройства

На рисунках |

1.10.1 |

и 1.10.2 |

представлено |

моделирование |

масштабируемого мультиплексора 16-1 в двух режимах.

Рисунок 1.10.1 - Результат функционального моделирования масштабируемого мультиплексора 16-1 в режиме Timing

Рисунок 1.10.2 - Результат функционального моделирования масштабируемого мультиплексора 16-1 в режиме Functional

9

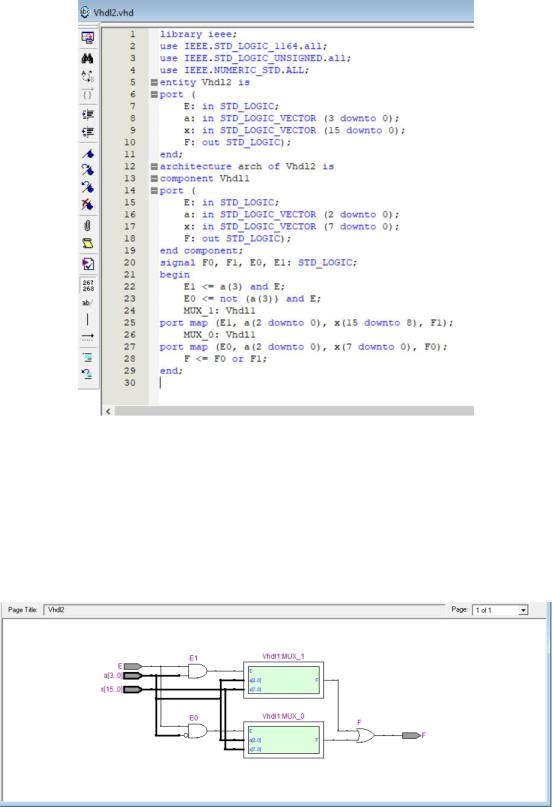

1.11 Код на HDL масштабируемого устройства

На рисунке 1.11.1 представлено описание устройства на VHDL.

Рисунок 1.11.1 - VHDL масштабируемого мультиплексора 16-1

1.12 Схема из RTL viewer для кода HDL масштабируемого устройства

На рисунке 1.11 представлена схема для устройства масштабируемого мультиплексора 16-1 из RTL viewer.

Рисунок 1.12.1 – Схема из RTL viewer для кода HDL масштабируемого мультиплексора 16-1

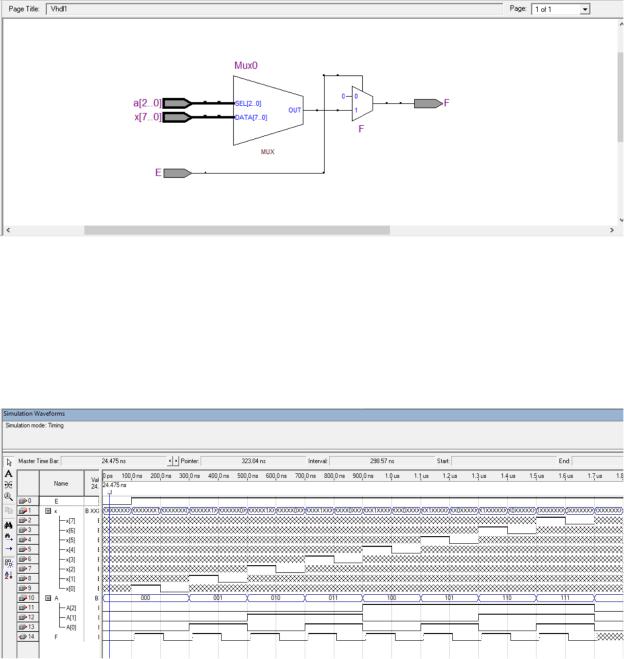

10