Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №6

по дисциплине «Электроника и схемотехника»

вариант № 17

Студент гр.

..2022

Руководитель

..2022

Томск 2022

Введение

Цель работы – изучение регистров, их принципов построения и работы.

В ходе выполнения данной лабораторной работы требуется выполнить следующие задачи:

1) Составить таблицы истинности для схем по варианту.

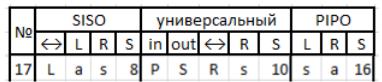

Вариант задания представлен на рисунке 1.

Рисунок 1 – Вариант задания

2)Собрать схемы заданных регистров на холстах bdf.

3)Продемонстрировать работу всех схем в двух режимах: Timing и

Functional.

4) Используя заданный вариантом HDL, описать и продемонстрировать

устройства.

2

1 РЕГИСТР ТИПА SISO

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности для устройства типа

siso.

Таблица 1.1 Таблица истинности устройства типа SISO

SISO

№ сигнала |

|

Входы |

|

Выход |

|

Load |

R |

sin |

sout |

1 |

0 |

0 |

b0 |

0 |

2 |

0 |

0 |

b1 |

0 |

3 |

0 |

0 |

b2 |

0 |

4 |

0 |

0 |

b3 |

0 |

5 |

0 |

0 |

b4 |

0 |

6 |

0 |

0 |

b5 |

0 |

7 |

0 |

0 |

b6 |

0 |

8 |

0 |

0 |

b7 |

b0 |

9 |

0 |

0 |

b8 |

b1 |

10 |

0 |

0 |

b9 |

b2 |

11 |

0 |

0 |

b10 |

b3 |

12 |

0 |

0 |

b11 |

b4 |

13 |

0 |

0 |

b12 |

b5 |

14 |

0 |

1 |

b13 |

0 |

15 |

0 |

0 |

b14 |

0 |

16 |

0 |

0 |

b15 |

0 |

17 |

0 |

0 |

b16 |

0 |

1.2 Функциональная схема

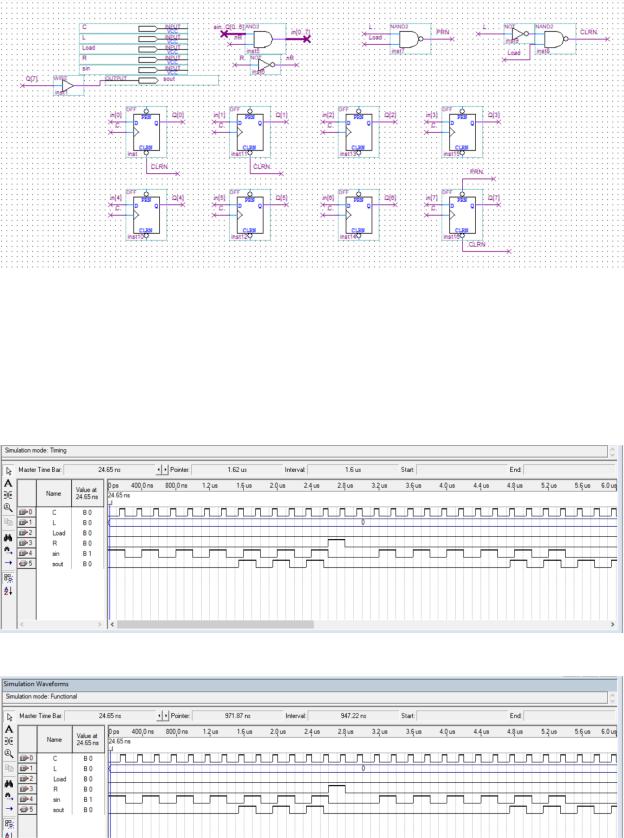

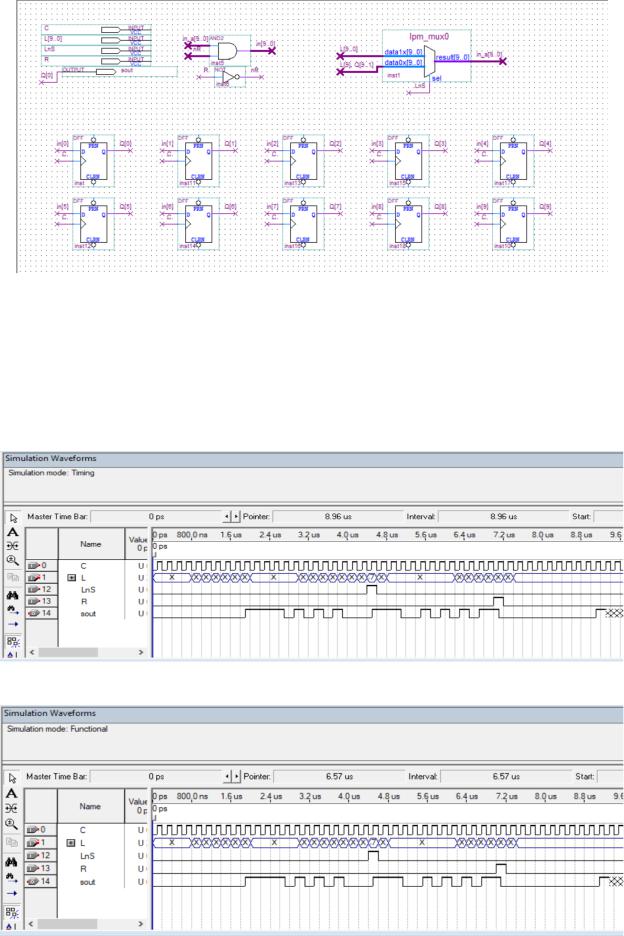

На рисунке 1.2.1 представлена функциональная схема устройства.

3

Рисунок 1.2.1 – Функциональная схема регистра SISO

1.3 Моделирование функциональной схемы

На рисунке 1.3.1 и 1.3.2 представлено моделирование функциональной схемы в двух режимах Timing и Functional.

Рисунок 1.3.1 – Моделирование в режиме Timing

Рисунок 1.3.2 – Моделирование в режиме Functional

1.4 Код на HDL

4

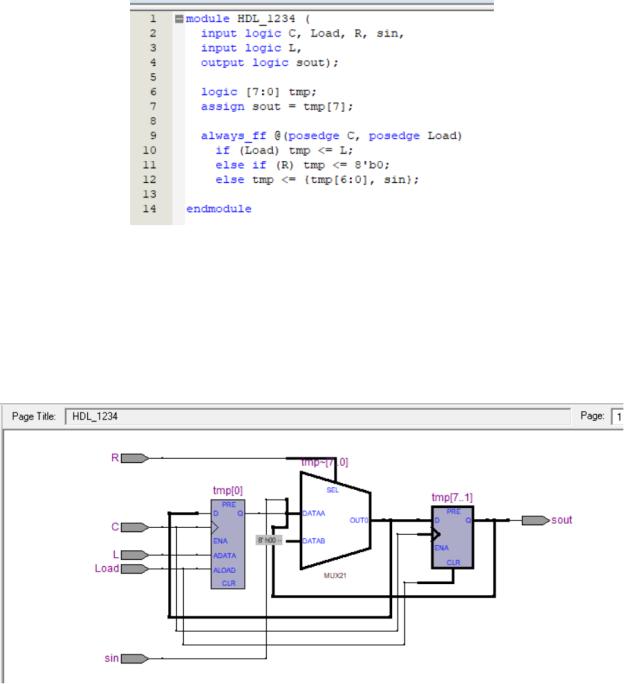

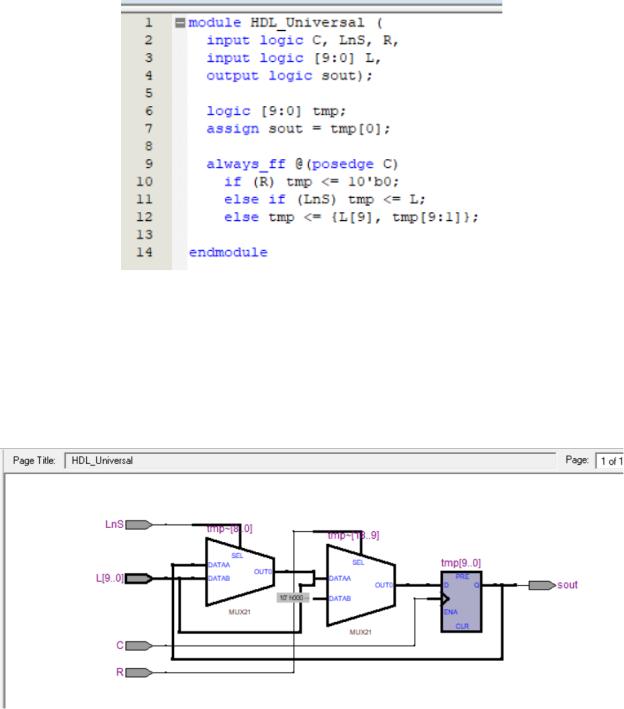

На рисунке 1.4.1 представлен код на языке описания SV.

Рисунок 1.4.1 – Код описания устройства на SV

1.5 Схема из RTL viewer

На рисунке 1.5.1 представлена схема из RTL viewer для кода,

написанного на SV.

Рисунок 1.5.1 - Схема из RTL viewer

1.6 Моделирование устройства описанного кодом SV

На рисунке 1.6.1 и 1.6.2 представлено моделирование регистра siso,

описанного кодом SV, в двух режимах.

5

Рисунок 1.6.1 – Моделирование устройства в режиме Timing

Рисунок 1.6.2 – Моделирование устройства в режиме Functional

2 РЕГИСТР ТИПА PISO

2.1 Таблица истинности

Ниже представлена таблица истинности, для регистра PISO.

Таблица 2.1 - Таблица истинности для регистра PISO

Универсальный (PISO)

№ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Выход |

Сигнала |

L9 |

L8 |

L7 |

L6 |

L5 |

L4 |

|

L3 |

L2 |

L1 |

L0 |

L_ns |

R |

sout |

1 |

a0 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

2 |

а1 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

3 |

а2 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

4 |

а3 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

5 |

а4 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

6 |

а5 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

7 |

а6 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

8 |

а7 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

9 |

а8 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

10 |

а9 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

a0 |

11 |

а10 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

0 |

0 |

a1 |

12 |

а11 |

x |

x |

x |

x |

x |

|

x |

x |

x |

X |

0 |

0 |

a2 |

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

№ |

L9 |

L8 |

L7 |

L6 |

L5 |

L4 |

L3 |

L2 |

L1 |

L0 |

L_ns |

R |

sout |

сигнала |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

а12 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a3 |

14 |

а13 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a4 |

15 |

а14 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a5 |

16 |

а15 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a6 |

17 |

а16 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a7 |

18 |

а17 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a8 |

19 |

а18 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a9 |

20 |

а19 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a10 |

21 |

а20 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a11 |

22 |

а21 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

a12 |

23 |

b9 |

b8 |

b7 |

b6 |

b5 |

b4 |

b3 |

b2 |

b1 |

b0 |

1 |

0 |

b9 |

24 |

c0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b8 |

25 |

c1 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b7 |

26 |

c2 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b6 |

27 |

c3 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b5 |

28 |

c4 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b4 |

29 |

c5 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b3 |

30 |

c6 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b2 |

31 |

c7 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b1 |

32 |

c8 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

b0 |

33 |

c9 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

c0 |

34 |

c10 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

c1 |

35 |

c11 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

c2 |

36 |

c12 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

1 |

0 |

37 |

c13 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

2.2 Функциональная схема

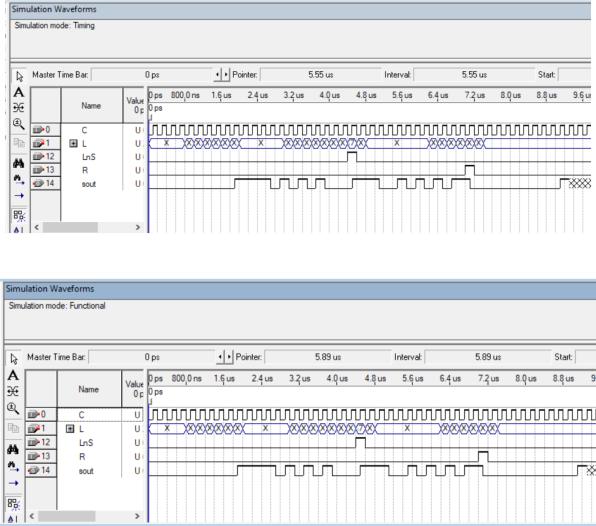

На рисунке 2.2.1 представлено изображение функциональной схемы.

7

Рисунок 2.2.1 – Функциональная схема регистра PISO

2.3 Моделирование функциональной схемы

На рисунке 2.3.1 представлено моделирование функциональной схемы регистра PISO, в двух режимах работы Timing и Functional.

Рисунок 3.2.1 – Моделирование в режиме Timing

Рисунок 3.2.2 – Моделирование в режиме Functional 8

2.4 Код на HDL

На рисунке 2.4.1 представлено изображение кода устройства, на SV.

Рисунок 2.4.1 – Код описания устройства на SV

2.5 Схема из RTL viewer для кода описанного на SV

На рисунке 2.5.1 представлено изображение схемы из RTL viewer, для кода, написанного на SV.

Рисунок 2.5.1 – Схема из RTL viewer

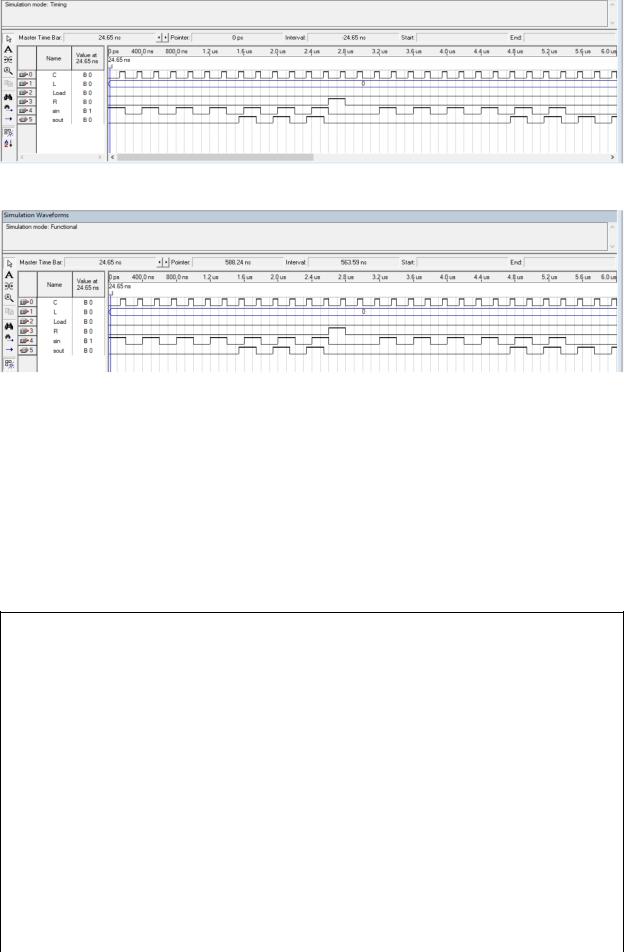

2.6 Моделирование устройства, описанного кодом HDL

На рисунках 2.6.1 и 2.6.2 представлено моделирование устройства, в

двух режимах работы Timing и Functional. 9

Рисунок 2.6.1 – Моделирование устройства, в режиме Timing

Рисунок 2.6.2 – Моделирование устройства в режиме Functional

3 РЕГИСТР ТИПА PIPO

3.1 Таблица истинности

Ниже, в таблице 3.1 представлена таблица истинности для регистра типа

PIPO.

Таблица 3.1 – Таблица истинности для регистра типа PIPO

№ |

|

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

||

сигнал |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

L |

L |

L |

L |

L |

L |

L9 |

|

L8 |

|

L7 |

L6 |

L5 |

L4 |

L3 |

L2 |

L1 |

L0 |

|

|

|

15 |

14 |

13 |

12 |

11 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

X |

X |

X |

X |

X |

X |

X |

|

X |

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

X |

X |

X |

X |

X |

X |

X |

|

X |

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

z15 |

z14 |

z13 |

z12 |

z11 |

z10 |

z9 |

|

z8 |

|

z7 |

z6 |

z5 |

z4 |

z3 |

z2 |

z1 |

z0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

X |

X |

X |

X |

X |

X |

X |

|

X |

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10