Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ СЧЁТЧИКОВ

Отчет по лабораторной работе №5 по дисциплине «Электроника и схемотехника»

вариант № 17

Студент гр.

Руководитель

.

..2022

Томск 2022

Введение

Цель работы – изучить двоичные счётчики, их принципы построения и работы.

Постановленные задачи:

1. Составить таблицы истинности для схем согласно варианту.

Таблица 1 – Вариант задания

|

Асинхронный |

|

|

Синхронный |

|

|||

|

|

|

|

|

|

|

|

|

тип |

|

счёт |

|

М |

фронт |

сброс |

счет |

М |

|

|

|

|

|

|

|

|

|

Т |

|

+ |

|

31 |

- |

s |

- |

26 |

|

|

|

|

|

|

|

|

|

2.Собрать схемы заданных счётчиков на холстах bdf.

3.Привести расчёты для задач делителя частоты и формирования задержки.

4.Собрать схемы делителя частоты и задержки.

5.Промоделировать работу всех схем в двух режимах и сравнить результаты с данными в таблице истинности.

6.Описать данные устройства используя VHDL.

2

1 АСИНХРОННЫЙ СЧЁТЧИК

1.1Таблица истинности

Втаблице 1.1 представлена таблица истинности для асинхронного счётчика.

Таблица 1.1 – Таблица истинности

№ сигнала |

|

|

Выходы |

|

|

|

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

1 |

1 |

1 |

1 |

16 |

1 |

0 |

0 |

0 |

0 |

17 |

1 |

0 |

0 |

0 |

1 |

18 |

1 |

0 |

0 |

1 |

0 |

19 |

1 |

0 |

0 |

1 |

1 |

20 |

1 |

0 |

1 |

0 |

0 |

21 |

1 |

0 |

1 |

0 |

1 |

22 |

1 |

0 |

1 |

1 |

0 |

23 |

1 |

0 |

1 |

1 |

1 |

24 |

1 |

1 |

0 |

0 |

0 |

25 |

1 |

1 |

0 |

0 |

1 |

26 |

1 |

1 |

0 |

1 |

0 |

27 |

1 |

1 |

0 |

1 |

1 |

28 |

1 |

1 |

1 |

0 |

0 |

29 |

1 |

1 |

1 |

0 |

1 |

30 |

0 |

0 |

0 |

0 |

0 |

31 |

0 |

0 |

0 |

0 |

1 |

32 |

0 |

0 |

0 |

1 |

0 |

|

|

3 |

|

|

|

1.2 Функциональная схема

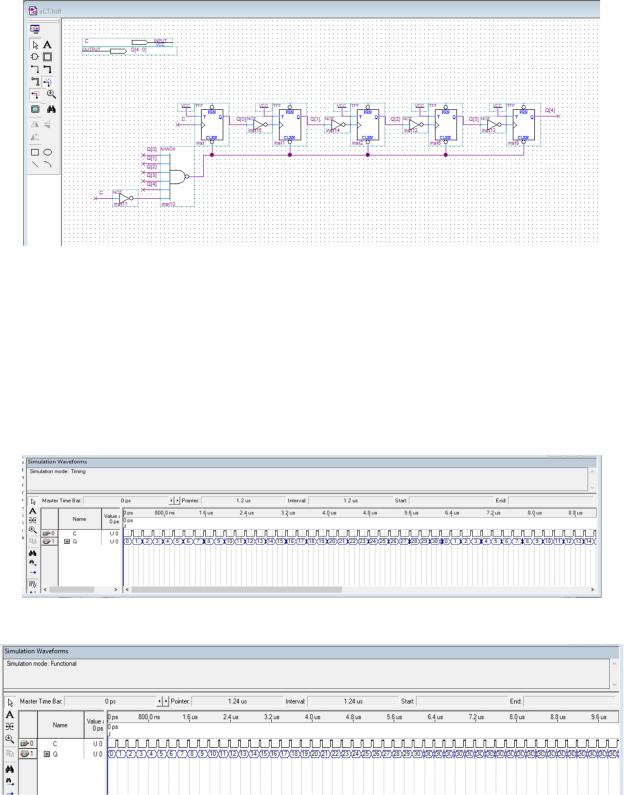

На рисунке 1.2.1 представлена функциональная схема асинхронного счётчика.

Рисунок 1.2.1 – схема асинхронного счётчика

1.3 Моделирование функциональной схемы

На рисунке 1.3.1 и 1.3.2 представлено моделирование функциональной схемы асинхронного счётчика в двух режимах. Так как счётчик асинхронный,

моделирование в режиме Functional работает некорректно.

Рисунок 1.3.1 – Моделирование асинхронного счётчика в режиме Timing

Рисунок 1.3.2 – Моделирование асинхронного счётчика в режиме Functional 4

1.4 Код на VHDL

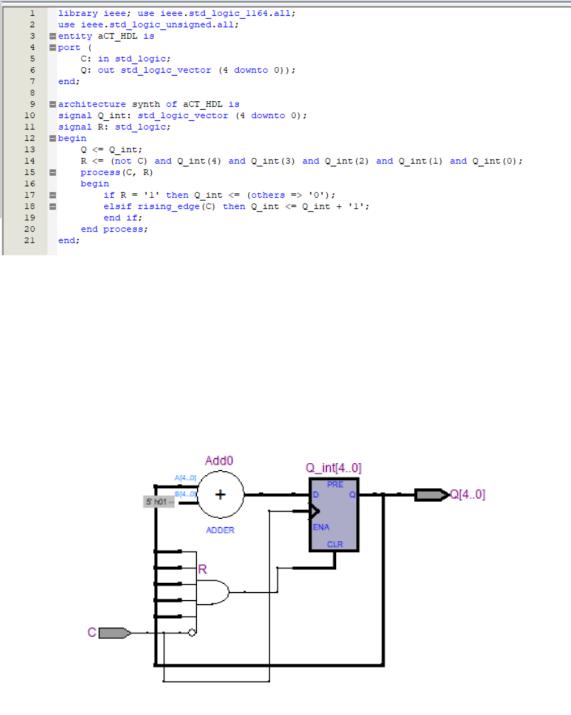

На рисунке 1.4.1 представлен код описания на VHDL.

Рисунок 1.4.1 – Код описания устройства на VHDL

1.5 Схема из RTL viewer для кода VHDL

На рисунке 1.5.1 представлена схема из RTL viewer для кода,

написанного на VHDL.

Рисунок 1.5.1 – Схема из RTL viewer

1.6 Моделирование устройства, описанного кодом VHDL

На рисунках 1.6.1 и 1.6.2 представлены результаты моделирования

асинхронного счётчика, описанного на VHDL. 5

Рисунок 1.6.1 – Моделирование в режиме Timing

Рисунок 1.6.2 – Моделирование в режиме Functional

2 СИНХРОННЫЙ СЧЁТЧИК

2.1Таблица истинности

Втаблице 2.1 представлена таблица истинности синхронного счётчика. Таблица 2.1 – Таблица истинности для синхронного счётчика

№ |

Вход |

|

|

Входы |

|

|

сигнала |

RP |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

1 |

0 |

0 |

0 |

3 |

0 |

1 |

0 |

1 |

1 |

1 |

4 |

0 |

1 |

0 |

1 |

1 |

0 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

0 |

1 |

0 |

0 |

7 |

0 |

1 |

0 |

0 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

1 |

0 |

9 |

0 |

1 |

0 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

0 |

0 |

0 |

11 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

6 |

|

|

|

№ |

RP |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

сигнала |

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

0 |

0 |

1 |

1 |

1 |

0 |

13 |

0 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

0 |

1 |

1 |

0 |

0 |

15 |

0 |

0 |

1 |

0 |

1 |

1 |

16 |

0 |

0 |

1 |

0 |

1 |

0 |

17 |

0 |

0 |

1 |

0 |

0 |

1 |

18 |

0 |

0 |

1 |

0 |

0 |

0 |

19 |

0 |

0 |

0 |

1 |

1 |

1 |

20 |

0 |

0 |

0 |

1 |

1 |

0 |

21 |

0 |

0 |

0 |

1 |

0 |

1 |

22 |

0 |

0 |

0 |

1 |

0 |

0 |

23 |

0 |

0 |

0 |

0 |

1 |

1 |

24 |

0 |

0 |

0 |

0 |

1 |

0 |

25 |

0 |

0 |

0 |

0 |

0 |

1 |

26 |

0 |

0 |

0 |

0 |

0 |

0 |

27 |

0 |

1 |

1 |

0 |

0 |

1 |

28 |

0 |

1 |

1 |

0 |

0 |

0 |

29 |

0 |

1 |

0 |

1 |

1 |

1 |

30 |

1 |

1 |

1 |

0 |

0 |

1 |

31 |

0 |

1 |

1 |

0 |

0 |

0 |

2.2 Функциональная схема

На рисунке 2.2.1 представлена функциональная схема синхронного счётчика.

7

Рисунок 2.2.1 – Схема синхронного счётчика

2.3 Моделирование функциональной схемы

На рисунках 2.3.1 и 2.3.2 представлено моделирование функциональной схемы синхронного счётчика в двух режимах.

Рисунок 2.3.1 – Моделирование функциональной схемы в режиме Timing

Рисунок 2.3.2 – Моделирование функциональной схемы в режиме Functional

2.4 Код на VHDL

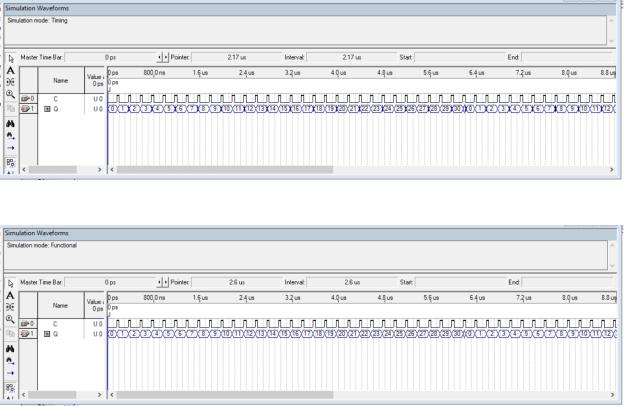

На рисунке 2.4.1 представлен код на VHDL для синхронного счётчика.

8

Рисунок 2.4.1 – Код описания устройства на VHDL

2.5 Схема из TRL viewer для схемы VHDL

На рисунке 2.5.1 представлена схема из TRL viewer для кода,

написанного на VHDL.

Рисунок 2.5.1 – Схема из TRL viewer для кода VHDL

2.6 Моделирование устройства, описанного кодом VHDL

На рисунке 2.6.1 и 2.6.2 представлено моделирование устройства синхронного счётчика описанного кодом VHDL, в двух режимах работы.

9

Рисунок 2.6.1 – Моделирование устройства в режиме Timing

Рисунок 2.6.2 – Моделирование устройства в режиме Functional

3 ДЕЛИТЕЛЬ ЧАСТОТЫ

3.1 Расчёты

Ниже приведены расчёты для делителя частоты:

Период входного сигнала: T = 20 нс.

Период выходного сигнала: t = 1 / 1666667 Гц = 600 нс.

Модуль счёта: t / T = 30.

Сброс для Т-триггера должен быть на 14, а изменение состояния на 29.

3.2 Функциональная схема

На рисунке 3.2.1 представлена функциональная схема для делителя частоты.

10