Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №8

по дисциплине «Электроника и схемотехника» вариант № 17

Студент гр.

Руководитель

Томск 2022

Введение

Цель работы – овладеть навыками совместного применения устройств

средней степени интеграции.

В ходе данной лабораторной работы требуется выполнить следующие

задачи:

1.Разработать обобщённую функциональную схему устройства и описать составные части схемы.

2.Составить таблицы функционирования операционного блока.

Логическая операция:

А ∩ B

Арифметическая операция:

А+В+1

3.Организовать приём и выдачу данных согласно варианту для выполнения 4-х операций, используя встроенные блоки регистров и счётчиков.

4.Создать схему реализации вычислительного блока, выполняющего заданные операции и осуществляющего приём входных данных и выдачу результата согласно варианту.

5.Составить план моделирования. Использовать для каждой операции по два различных набора данных.

6.Промоделировать работу схемы в двух режимах работы и сравнить результаты моделирования с составленным планом моделирования.

7.Используя заданный вариантом HDL, описать и промоделировать то же устройство.

Вариант HDL: SV.

2

1 ВЫЧИСЛИТЕЛЬ ФУНКЦИИ

1.1 Обобщённая функциональная схема

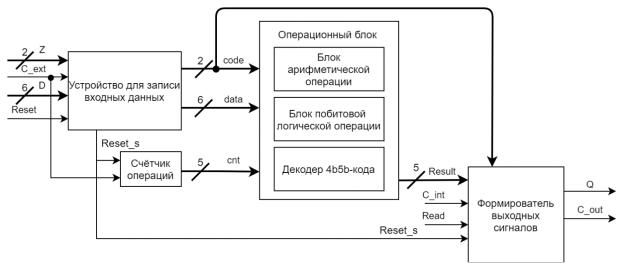

На рисунке 1.1.1 предоставлена обобщенная функциональная схема.

Рисунок 1.1.1 – Обобщённая функциональная схема

Устройство на вход получает параллельный код, после чего передает его в операционный блок. В операционном блоке выполняются требуемые по варианту задачи и их результаты переходят в выходной блок. В выходном блоке полученный код формируется в последовательный и выводится в зависимости от кода операции Z.

3

1.2Таблица истинности

Втаблице 1.2.1 представлена таблица истинности для декодирования устройства 4b5b-кода в двоичное число.

Таблица 1.2.1 – Декодирование 4b5b в двоичное число

Декодирование 4b5b-кода в двоичное число

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

X |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

X |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

X |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

X |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

X |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

X |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

X |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

X |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

X |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

X |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

X |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

4

В таблице 1.2.2 представлена таблица истинности для логической

операции А и (НЕ В).

Таблица 1.2.2 – Таблица истинности для логической операции

A И (НЕ В)

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

|

|

Выходы |

|

|

|||

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

Q4 |

|

|

Q3 |

Q2 |

Q1 |

Q0 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

X |

0 |

0 |

0 |

0 |

|

|

0 |

|

|

0 |

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X |

X |

b0 |

0 |

0 |

1 |

0 |

|

|

0 |

|

|

|

|

|

- |

- |

||||

|

|

|

|

|

b0 |

|||||||||||||||

X |

b1 |

X |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

0 |

|

- |

- |

|||

|

|

|

|

b1 |

|

|||||||||||||||

X |

b3 |

b2 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

- |

- |

||

|

|

|

|

b3 |

|

b2 |

||||||||||||||

b4 |

X |

X |

1 |

0 |

0 |

|

|

|

|

|

0 |

|

|

0 |

|

- |

- |

|||

|

|

b4 |

|

|

|

|

||||||||||||||

b6 |

X |

b5 |

1 |

0 |

1 |

|

|

|

|

|

0 |

|

|

|

|

|

- |

- |

||

|

|

b6 |

|

|

|

|

b5 |

|||||||||||||

b8 |

b7 |

X |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

0 |

|

- |

- |

|

|

|

b8 |

|

|

|

b7 |

|

|||||||||||||

b11 |

b10 |

b9 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

- |

|

b11 |

|

|

b10 |

|

b9 |

||||||||||||||

0 |

0 |

0 |

a2 |

a1 |

a0 |

|

|

a2 |

|

|

|

a1 |

|

a0 |

- |

- |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

0 |

1 |

a4 |

a3 |

X |

|

|

a4 |

|

|

|

a3 |

0 |

|

- |

- |

||||

0 |

1 |

0 |

a6 |

X |

a5 |

|

|

a6 |

|

0 |

|

|

|

a5 |

- |

- |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

1 |

1 |

a7 |

X |

X |

|

|

a7 |

|

0 |

|

|

0 |

|

- |

- |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

1 |

0 |

0 |

X |

a9 |

a8 |

0 |

|

|

|

|

a9 |

|

a8 |

- |

- |

|||||

1 |

0 |

1 |

X |

a10 |

X |

0 |

|

|

|

a10 |

0 |

|

- |

- |

||||||

1 |

1 |

0 |

X |

X |

a11 |

0 |

|

|

0 |

|

|

a11 |

- |

- |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

1 |

1 |

1 |

X |

X |

X |

0 |

|

|

0 |

|

|

0 |

|

- |

- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В таблице 1.2.3 представлена таблица истинности для арифметической

операции А+В+1.

Таблица 1.2.3 – Таблица истинности для арифметической операции

A+B+1

|

|

Входы |

|

|

|

|

Выходы |

|

|

|||

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

Q3 |

|

Q2 |

|

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

1 |

- |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

|

0 |

- |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

|

1 |

- |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

|

0 |

- |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

|

1 |

- |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

|

0 |

- |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

|

1 |

- |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

0 |

|

0 |

- |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

0 |

- |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

|

1 |

- |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

|

0 |

- |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

|

1 |

- |

|

|

|

|

|

5 |

|

|

|

|

|

|

|

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

- |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

- |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

- |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

- |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

- |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

- |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

- |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

- |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

- |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

- |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

- |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

- |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

- |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

- |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

- |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

- |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

- |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

- |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

- |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

- |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

- |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

- |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

- |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

- |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

- |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

- |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

- |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

- |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

- |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

- |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

- |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

- |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

- |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

- |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

- |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

- |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

- |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

- |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

- |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

- |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

- |

|

|

|

|

|

6 |

|

|

|

|

|

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

- |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

- |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

- |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

- |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

- |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

- |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

- |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

- |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

- |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

- |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

- |

1.3 Функциональная схема

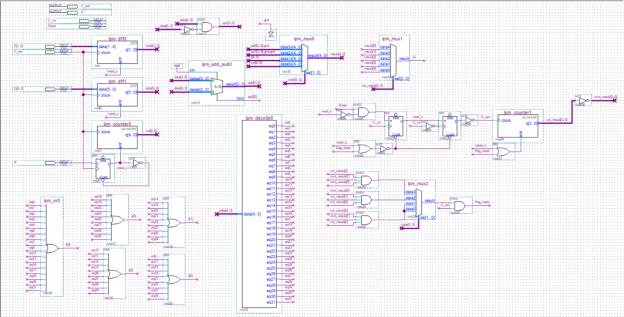

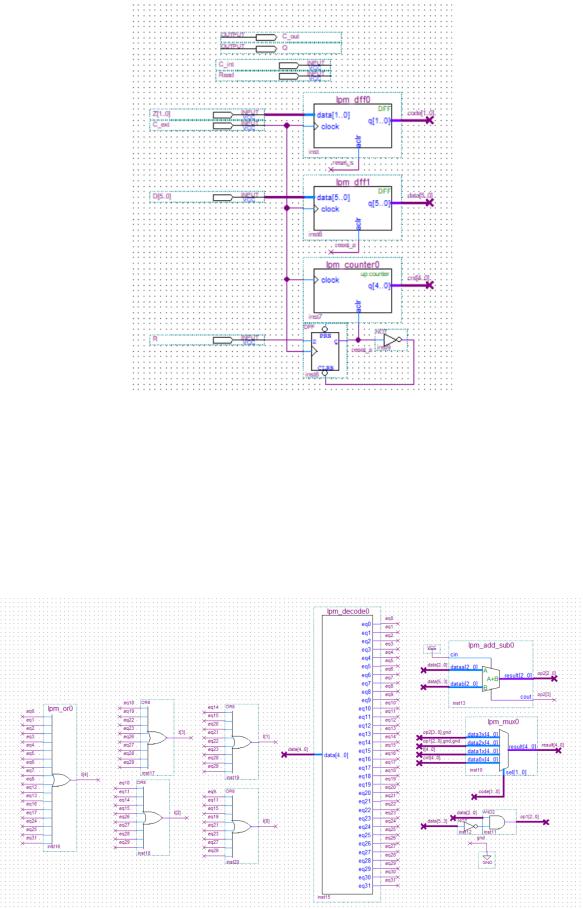

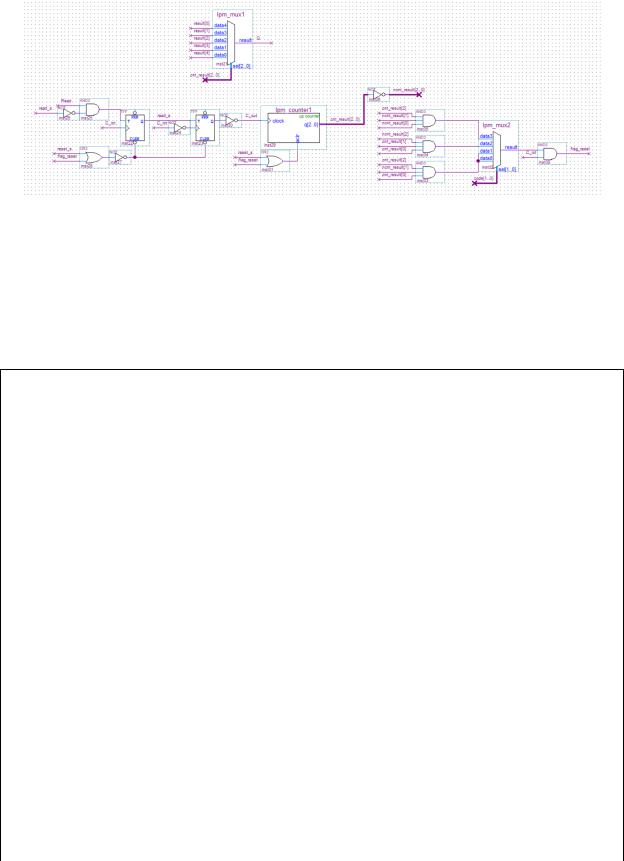

На рисунке 1.3.1 представлено изображение для функциональной схемы из CАПР Quartus2.

Рисунок 1.3.1 – Функциональная схема На рисунке 1.3.2 представлен входной блок схемы. В регистры по

убывающему фронту внешнего синхросигнала С_ext сохраняются входные данные, данные для выполнения операции и код операции.

7

Рисунок 1.3.2 – Входной блок совместно со счётчиком На рисунке 1.3.3 представлен операционный блок. С помощью

дешифратора и функций ИЛИ выполнена задача. При помощи элементов

AND и NOT выполнена логическая операция. Элемент add_sub0 выполняет арифметическую операцию, а lpm_mux0 определяет, какой ответ нужно подать на выходной блок.

Рисунок 1.3.3 – Операционный блок

8

На рисунке 1.3.4 представлен выходной блок. При подачи сигнала Read,

формируется выход C_out. Мультиплексор выбирает какая из функций будет выводится.

Рисунок 1.3.4 – Выходной блок

1.4Моделирование

Втаблице 1.4.1 представлен план моделирования. Таблица 1.4.1 – План моделирования

План

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

№ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сигнал |

Сбро |

|

Код |

|

|

Данные |

|

|

|

|

|

|

|

|

|||

с |

операции |

|

|

|

|

|

|

|

|

|

|

|

|

а |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

Z |

|

Z0 |

D |

D |

D |

D |

D |

D |

Q |

Q |

|

Q |

Q |

Q |

|

|

1 |

|

|

5 |

4 |

3 |

2 |

1 |

0 |

4 |

3 |

|

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

X |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

X |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

- |

- |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

- |

- |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

- |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

- |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

|

1 |

1 |

1 |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

X |

|

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

|

0 |

0 |

0 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

|

0 |

0 |

1 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

На рисунке 1.4.1 и 1.4.2 представлены результаты моделирования в двух режимах.

В промежутке 430-3200нс промоделирована работа первого сигнала,

3400-6200нс промоделирована работа второго сигнала, 6400-8200нс промоделирована работа третьего сигнала, 8400-10200 моделирование работы четвёртого сигнала, 10400-13200нс промоделирована работа пятого сигнала,

13500-16200нс промоделирована работа шестого сигнала, 16300-19200нс промоделирована работа седьмого сигнала, 19400-20200 восьмого сигнала,

20400-22800 девятого сигнала.

Рисунок 1.4.1 – Результат моделирования в режиме Timing

Рисунок 1.4.2 – Результат моделирования в режиме Functional

Результаты моделирования совпадают с планом моделирования, представленном в таблице 1.4.1.

1.5 Описание программы

Ниже приведен листинг кода, на языке описания аппаратуры SV.

module SVlabor8 (

input logic C_ext, C_int, R, Read, input logic [1:0] Z,

input logic [5:0] D, output logic Q, C_out);

10