1.13 Моделирование масштабируемого устройства, описанного кодом

HDL

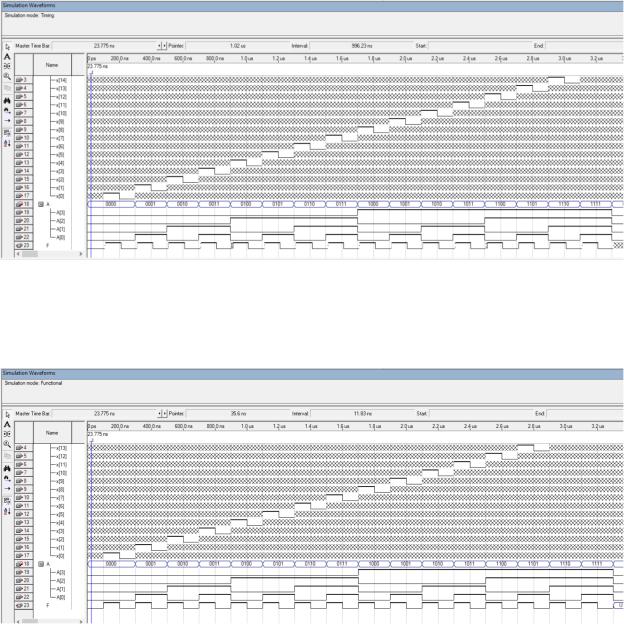

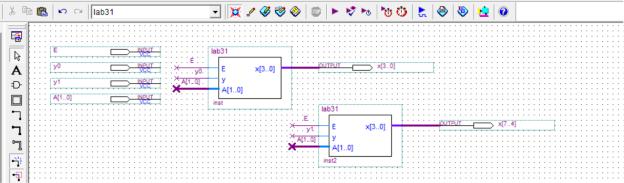

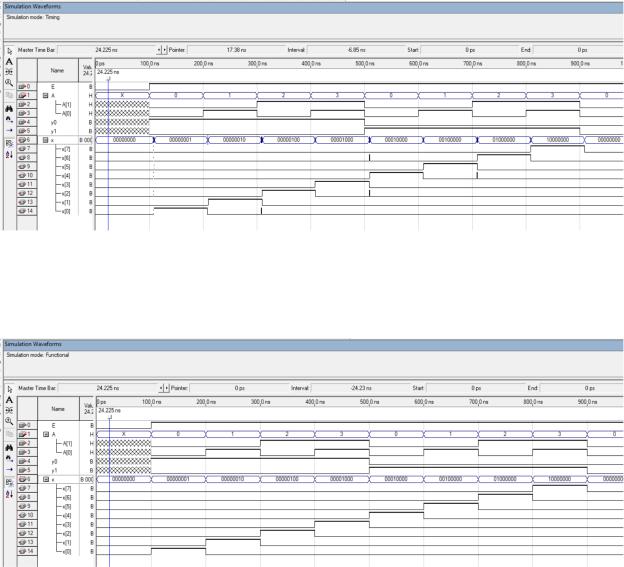

На рисунках 1.13.1 и 1.13.2 представлено моделирование устройства,

описанного на VHDL, в режиме Timing и Functional.

Рисунок 1.13.1 – Результат моделирования на VHDL масштабируемого мультиплексора 16-1 в режиме Timing

Рисунок 1.13.2 – Результат моделирования на VHDL масштабируемого мультиплексора 16-1 в режиме Functional

11

2 ДЕМУЛЬТИПЛЕКСОР 1-4

2.1 Таблица истинности

На приемной стороне канала передачи данных требуется выполнить обратную операцию – демультиплексирование. Эту операцию выполняют демультиплексоры, которые передают данные поступающие в последовательные моменты времени, из одного входного канал в один из нескольких каналов-приемников

Таблица 4 отражает таблицу истинности для демультиплексора 1-4.

Таблица 4 - Таблица истинности демультиплексора 1-4

|

Входы |

|

|

Выходы |

|

||

|

|

|

|

|

|

|

|

E |

A1 |

A0 |

y |

x3 |

x2 |

x1 |

x0 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

B0 |

0 |

0 |

0 |

B0 |

|

|

|

|

|

|

|

|

1 |

0 |

1 |

B1 |

0 |

0 |

B1 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

0 |

B2 |

0 |

B2 |

0 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

1 |

B3 |

B3 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

2.2 Формула

x0 E A1 A0 y x1 E A1 A0 y x2 E A1 A0 y x3 E A1 A0 y

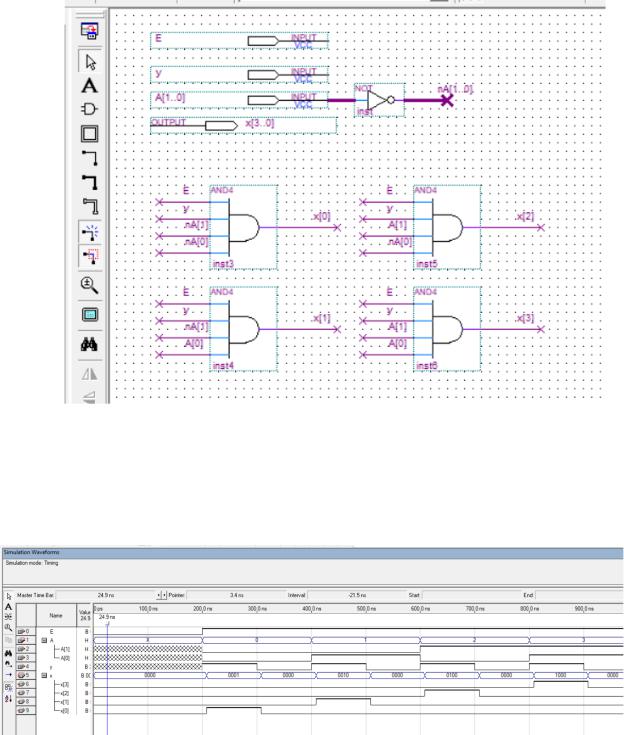

2.3 Функциональная схема

На рисунке 2.3.1 представлена функциональная схема демультиплексора 1–4

12

Рисунок 2.3.1 – Функциональная схема демультиплексора 1-4

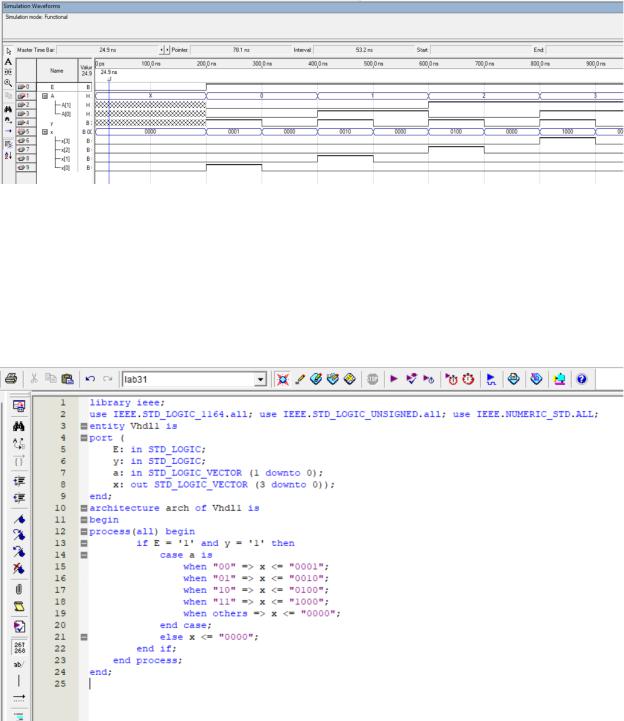

1.4 Моделирование

На рисунках 1.4.1 и 1.4.2 представлено моделирование в двух режимах.

Рисунок 2.4.1 – Результат функционального моделирования демультиплексора 1-4 в режиме Timing

13

Рисунок 2.4.2 – Результат функционального моделирования демультиплексора 1-4 в режиме Functional

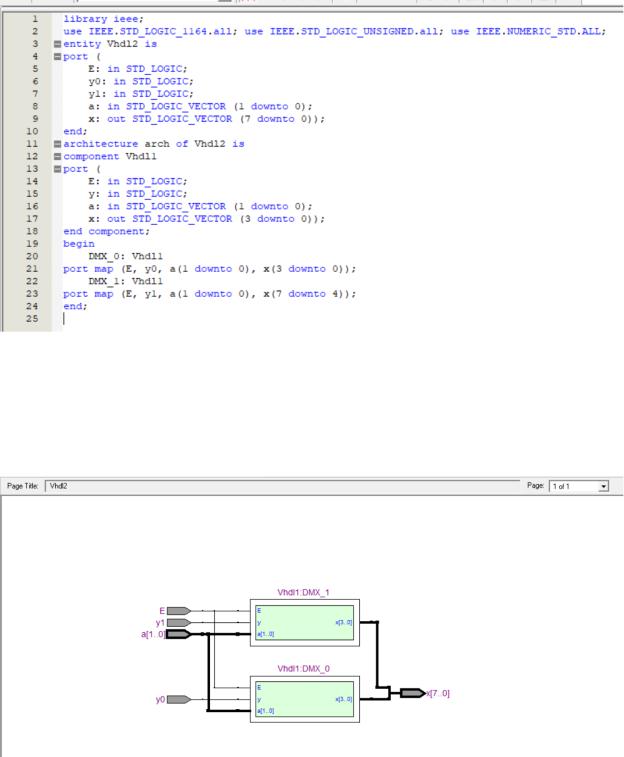

1.5 Код на HDL

На рисунке 1.5.1 представлено описание устройства на VHDL.

Рисунок 1.5.1 – Код демультиплексора 1-4 на VHDL

14

2.6 Схема из RTL viewer для кода HDL

Рисунок 2.6.1 – Схема из RTL viewer для кода HDL демультиплексора 1-4

2.7 Моделирование устройства, описанного кодом HDL

На рисунке 2.7.1 представлено моделирование устройства, описанного на VHDL, в режиме Timing

Рисунок 2.7.1 – Результат моделирования на VHDL демультиплексора 1-4

15

2.8Таблица истинности масштабируемого устройства

Втаблице 5 представлена таблица истинности масштабируемого устройства демультиплексора 2-8

Таблица 5 - Таблица истинности масштабируемого демультиплексора

2-8

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

A1 |

|

A0 |

|

y0 |

y1 |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

B0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

B0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

|

B1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

B1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

|

B2 |

0 |

0 |

0 |

0 |

0 |

0 |

B2 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

|

B3 |

0 |

0 |

0 |

0 |

0 |

B3 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|

0 |

B4 |

0 |

0 |

0 |

B4 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

|

0 |

B5 |

0 |

0 |

B5 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

|

0 |

B6 |

0 |

B6 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

|

0 |

B7 |

B7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

|

x |

|

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

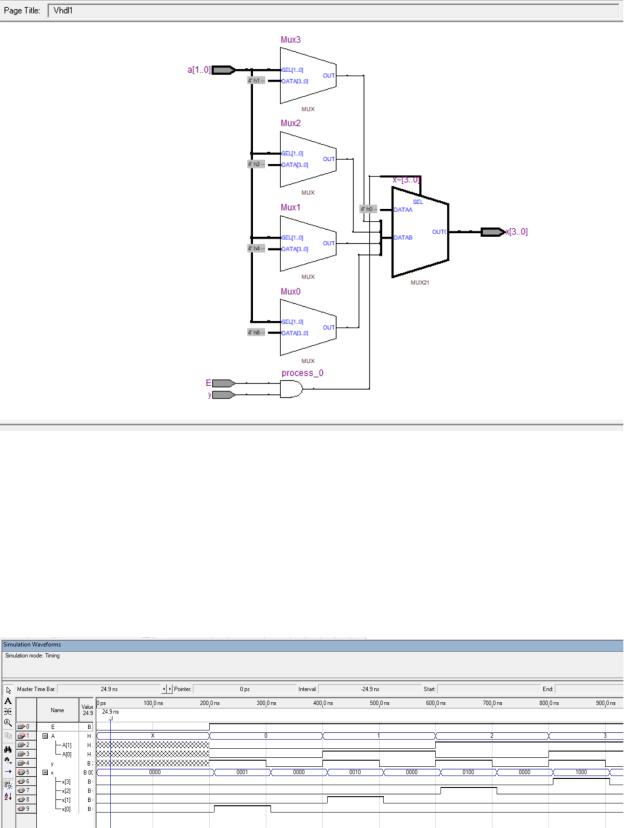

2.9 Функциональная схема масштабируемого устройства

На рисунке 2.7 представлена схема масштабируемого демультиплексора

2-8.

Рисунок 2.9.1 – Функциональная схема масштабируемого демультиплексора

2-8

16

2.10 Моделирование масштабируемого устройства

На рисунках 2.10.1 и 2.10.2 представлено моделирование демультиплексора 2-8 в двух режимах.

Рисунок 2.10.1 - Результат функционального моделирования масштабируемого демультиплексора 2-8 в режиме Timing

Рисунок 2.10.2 - Результат функционального моделирования масштабируемого демультиплексора 2-8 в режиме Functional

2.11 Код на HDL масштабируемого устройства

На рисунке 2.11.1 представлено описание устройства на VHDL.

17

Рисунок 2.11.1 – Код демультиплексора 2-8 на VHDL

2.12 Схема из RTL viewer для кода HDL масштабируемого устройства

На рисунке 2.12.1 представлена схема для устройства из RTL viewer.

Рисунок 2.12.1 – Схема из RTL viewer для кода HDL масштабируемого демультиплексора 2-8

18

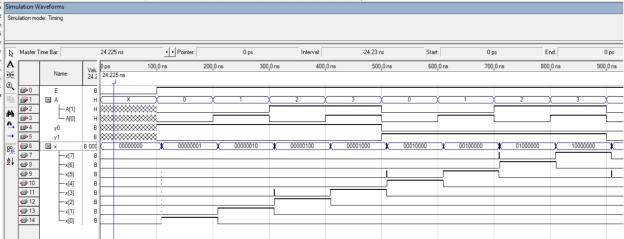

2.13 Моделирование масштабируемого устройства, описанного кодом

HDL

На рисунке 2.13.1 представлено моделирование устройства, описанного на HDL, в режиме Timing.

Рисунок 2.13.1 – Результат моделирования на VHDL масштабируемого демультиплексора 2-8

19

3 РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ МУЛЬТИПЛЕКСОРА

3.1Таблица истинности

Втаблице 6 представлена таблица истинности функции.

Таблица 6 - Таблица истинности для заданной вариантом функции

|

|

Входы |

|

Выход |

|

x |

y |

|

z |

w |

F |

0 |

0 |

|

0 |

0 |

1 |

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

0 |

0 |

|

1 |

1 |

1 |

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

0 |

1 |

0 |

|

|

|

|

|

|

0 |

1 |

|

1 |

0 |

0 |

|

|

|

|

|

|

0 |

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

1 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

1 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

1 |

0 |

|

1 |

0 |

0 |

|

|

|

|

|

|

1 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

1 |

1 |

|

0 |

0 |

1 |

|

|

|

|

|

|

1 |

1 |

|

0 |

1 |

0 |

|

|

|

|

|

|

1 |

1 |

|

1 |

0 |

0 |

|

|

|

|

|

|

1 |

1 |

|

1 |

1 |

1 |

|

|

|

|

|

|

3.2 Формула

Формула для выхода F будет иметь вид: F x y w z

20