- •Раздел 1. Виды мпт-средств, используемых в качестве ядра мпу.

- •Раздел 2. Функциональная схема мпу

- •2.1. Адресные пространства и их взаимодействие

- •2.1.1. Параллельные адресные пространства

- •2.1.2. Совмещенные адресные пространства

- •2.1.3. Смешанные адресные пространства

- •2.2. Расширенное адресное пространство.

- •2.2.1. Метод регистровых пар

- •2.2.2. Метод оконного доступа

- •2.2.3. Доступ с помощью сегментных регистров

- •Раздел 3. Структурная схема мпу.

- •Раздел 4. Блоки питания мпу

- •4.1. Общие требования

- •4.2. Общие вопросы электропитания и заземления

- •4.3. Гальваническая развязка

- •Раздел 5. Память мпу.

- •5.1. Память программ мпу

- •5.1.1. Пзу масочного типа

- •5.1.2. Ппзу

- •5.1.3. Уфппзу

- •5.1.4. Эппзу

- •5.2. Память данных

- •5.3. Энергонезависимая память

- •5.3.1. Микросхемы памяти fram

- •5.3.1.1. История создания

- •5.3.1.2. Принцип работы fram

- •5.3.2. Микросхемы памяти mram

- •5.3.2.1. Принципы работы

- •5.3.2.2. Сравнение с другими типами памяти

- •5.3.2.2. Общее сравнение

- •Раздел 6. Схемотехническая реализация автомата

- •Раздел 7. Шины мпу.

- •7.1. Шины микропроцессорной системы

- •7.2. Циклы обмена информацией

- •Раздел 8. Системы отладки мпу

- •8.1. Основные понятия и термины

- •8.2. Процесс отладки мпу

- •8.3. Функция средств отладки

- •8.3.1. Автоматизация программирования мпу или разработки пс.

- •8.3.2. Управление прототипом мпу при комплексной отладке.

- •8.3.3. Контроль функционирования и регистрации состояния мпу.

- •8.3.4 Запись отлаженных программных средств в бис ппзу.

- •8.4. Мпу как объект отладки

- •8.5. Требования, предъявляемые к системе отладки

- •8.5.1. Требования невидимости

- •8.5.2. Требования к предоставляемому сервису

- •8.5.3. Требование прозрачности.

- •8.6. Режимы работы отлаживаемых мпу.

- •8.6.1. Процессор контрольных точек (точек останова)

- •8.6.2. Трассировка.

- •8.6.3. Частичная эмуляция ас.

- •8.7. Инструментальные средства отладки

- •8.7.1. Общие сведения об отладочных средствах

- •8.7.2. Внутрисхемный эмулятор

- •8.7.3. Интегрированная среда разработки

- •8.7.4. Отладочный монитор

- •8.7.5. Эмуляторы пзу

- •8.7.6. Встроенные средства отладки

2.2.2. Метод оконного доступа

Метод оконного доступа является единственным процессор-независимым методом, его можно адаптировать практически к любой архитектуре системы.

Суть метода сводится к тому, что в непосредственно адресуемом пространстве выделяется область, называемая окном, размер которой равен степени двойки. Расширенное пространство разбивается на области, равные по размеру окну, которые нумеруются.

При обращении в регистр ДП записывается номер области, проекцию которой в область окна нужно получить.

При обращении к адресу, не попадающему в область окна диспетчер памяти не включается и логический адрес совпадает с физическим.

Если же адрес ячейки, к которой идет обращение, находится в области окна, диспетчер памяти производит пересчет таким образом, чтобы адрес ячейки совпал с адресом на требуемой странице. Например, если адресуется 5 ячейка окна, а в диспетчере памяти указана область 3, то адрес пересчитывается таким образом, чтобы попасть на 5 ячейку от начала 3 области.

Рис 2.7. Метод оконного доступа

2.2.3. Доступ с помощью сегментных регистров

Суть этого способа доступа заключается в том, что диспетчер памяти имеет регистры, определяющие адрес, с которого начинается проекция логического адресного пространства на физическое. Каждый из регистров, как показано на рисунке 2.8, дает собственную проекцию. Проекции, даваемые с помощью различных регистров, независимы, в том числе – могут совпадать.

Рис 2.8. Доступ с помощью сегментных регистров

Механизм вычисления адреса проекции на примере содержащего логический адрес регистра BX и сегментного регистра DS показан на рисунке 2.9.

Рис 2.9. Вычисление физического адреса с помощью сегментного регистра

Из примера, приведенного на рисунке 2.9 можно сделать ряд выводов, касающихся особенностей этого метода.

Во-первых, поскольку перенос при сложении не учитывается, то физическое адресное пространство оказывается «склеено» в кольцо. То есть, если проекция начинается меньше чем за 64 Кб от верхнего адреса – 0FFFFFh, то она будет продолжена с адреса 0.

Во-вторых, поскольку к младшей тетраде логического адреса прибавляется значение, равное нулю, то проекция может начинаться только с физического адреса, кратного 16.

Раздел 3. Структурная схема мпу.

Структурная схема используется для того, чтобы показать, какие устройства входят в данное конкретное МПУ и как они взаимодействуют (через какие шины, интерфейсы и т.д.). Пример структурной схемы, включающей в себя типовые компоненты, показан на рисунке 3.1.

Рис 3.1. Пример структурной схемы МПУ

Рассмотрим назначение устройств, показанных на этой структурной схеме.

Центральный процессорный блок (ЦП) – включает в себя как ядро системы, так и вспомогательные узлы, обеспечивающие функционирование МПТ в целом, как системы. К ним могут быть отнесены микросхемы обрамления (приёмопередатчики и т.п.), генераторы сетки частот, формирователи временных последовательностей и т.д.

Память МПУ (ОЗУ и ПЗУ) – узлы и устройства памяти, обеспечивающие постоянное или временное хранение программы и данных. Эти элементы присутствуют на структурной схеме вне зависимости от применяемой архитектуры. Сравнение их относительных ёмкостей помогает понять, чем – ЭВМ общего назначения или встраиваемым устройством является данное МПУ.

ЭВМ общего назначения хранит программы и данные в ОЗУ, а ПЗУ необходимо только для начального тестирования и загрузки операционной системы. Следовательно, в этом случае ёмкость ОЗУ существенно превосходит ёмкость ПЗУ.

Встраиваемая МПУ поставляется заказчику уже укомплектованная рабочими программами, которые записаны, естественно, в ПЗУ. ОЗУ же в этом случае необходимо только для хранения переменных и, следовательно, ёмкость его должна быть существенно меньше, чем ёмкость ПЗУ. Однако, по ряду причин, чаще всего оказывается выгоднее поставить ОЗУ ёмкостью, соизмеримой с ёмкостью ПЗУ – микросхему ОЗУ на требуемые, скажем, 64 байта найти сложнее и дороже, чем выпускаемую огромными партиями ОЗУ 32Кх8. То, что реально будет использоваться незначительная часть ёмкости микросхемы, оправдывается существенно более низкой ценой.

Контроллеры ввода/вывода (КВУ) служат для логического и временного согласования шины внешнего устройства с шиной МПУ. Их устройство, схемотехника и работа рассматриваются в курсе «Схемотехника ЭВМ».

Устройство управления (УУ) – характерная особенность устройств, работающих без постоянного участия оператора. Задача этого устройства – обнаружить, что МПУ перешло в нештатный режим и подать сигнал системного сброса. Автоматизированные системы, не использующие оператора-человека, тоже подвержены ошибкам, зависаниям и другим сбоям (в том числе аппаратным).

Использование сторожевых таймеров в качестве УУ увеличивает стабильность работы — нет необходимости ручного сброса. Поэтому наиболее частое использование таких устройств — встроенные системы различного назначения.

Сторожевой таймер (контрольный таймер, англ. Watchdog timer, WDT) — аппаратно реализованная схема контроля за зависанием системы. Представляет собой таймер, который периодически сбрасывается контролируемой системой. Если сброса не произошло в течение некоторого интервала времени, происходит принудительная перезагрузка системы.

Физически УУ может быть:

• Самостоятельным устройством.

• Компонентом устройства, например, микросхемой на материнской плате.

• Частью кристалла SoC.

Блок питания (БП) микропроцессорной системы – специфический узел, к которому предъявляются специальные требования. Более подробно блок питания будет рассмотрен ниже.

Структурные схемы реальных устройств значительно сложнее, чем приведённая на рисунке 3.1. Для сравнения, на рисунках 3.2, 3.3 и 3.4. приведены структурные схемы реально существующих устройств.

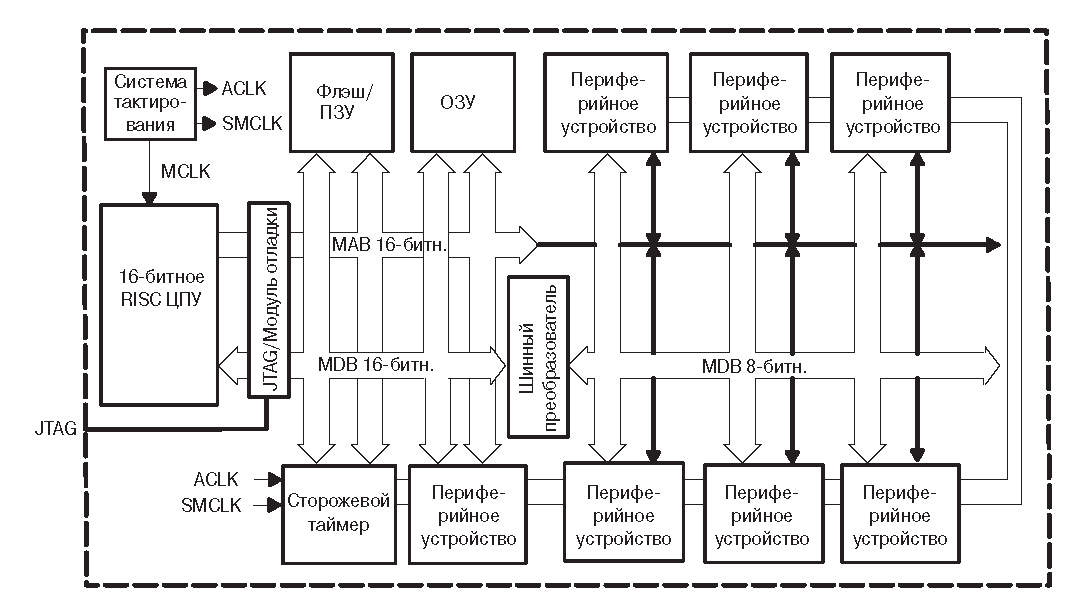

Рис 3.2. Пример структурной схемы ОЭВМ MSP430

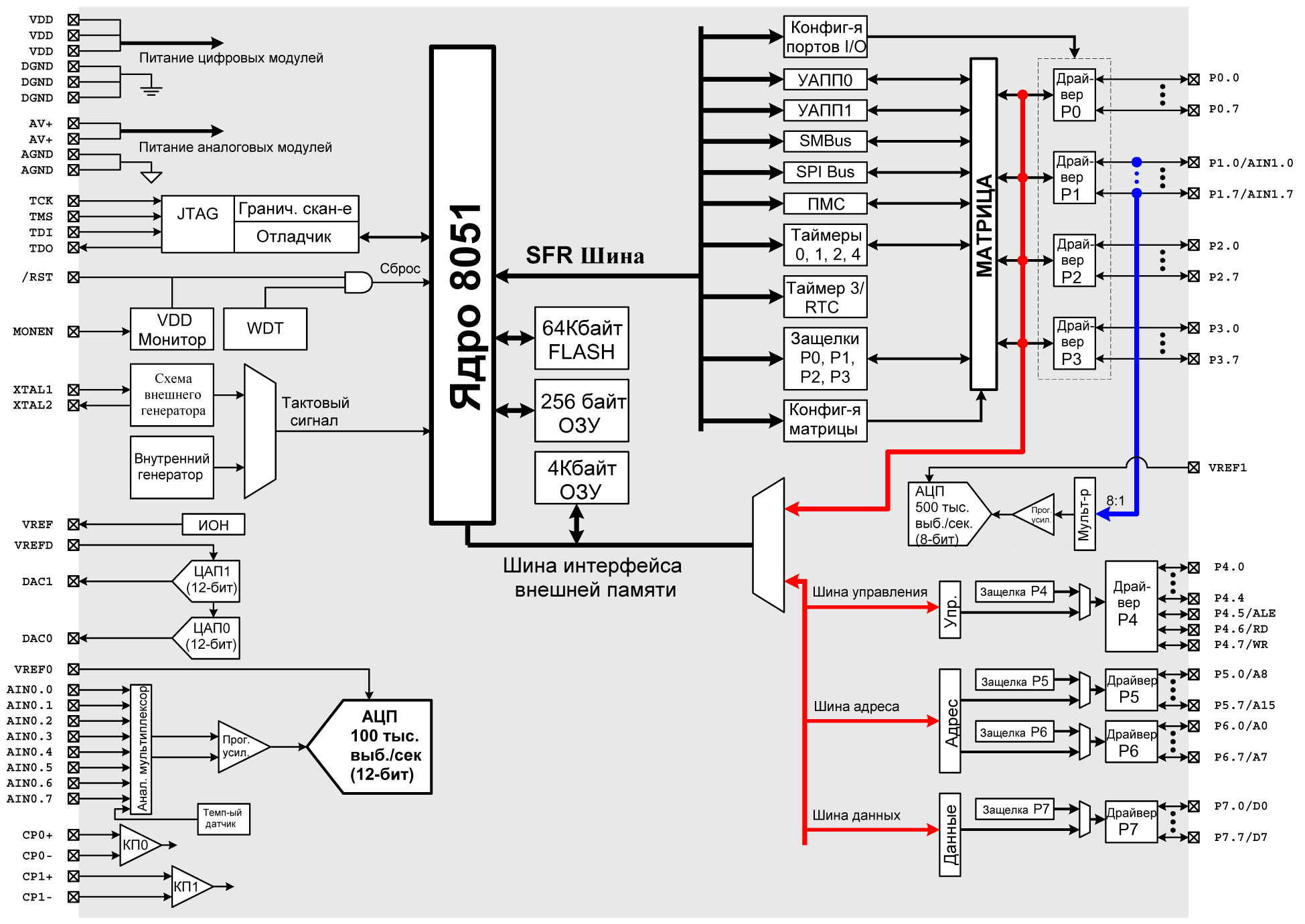

Рис 3.3. Пример структурной схемы ОЭВМ архитектуры MCS-51

Рис 3.4. Пример структурной схемы ПСНК 8051F020