- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

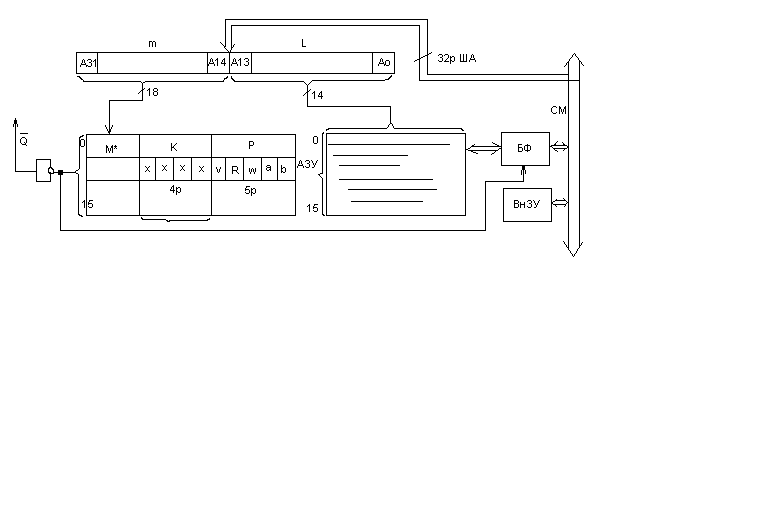

19.Организация виртуальной памяти.

Вирт память создает у польз-ля иллюзию будто бы при небольш (ограниченных) объемах физ ОЗУ, пользов-ль имееточень большие ОЗУ. Это достигается за счет использ внешних носителей инф.(напр HDD,стримеры,CD-ROM,Zip,Flash)

256К – физ ОЗУ

ША – 23-разр -> 232=4 Гб

При орг Вирт памяти физ ОЗУ разбивается на страницы (размер произв опр-ся разработчиком).

1стр-16к=214

Все адр пространство разбивается на страницы.

Nстр=232/214=218=256к страниц.

В физ ОЗУ может нах-ся 16 стр.

М-абс номер стр L-номер ячейки на стр Р-поля признаков

Ассоциативное ОЗУ- ОЗУ в котором входной инф явл-ся данные а выходом явл адрес ячейки где эти данные нах-ся.\Контроллер Вирт памяти имеет столько ячеек АЗУ сколько физ страниц может располагаться в ОЗУ. Процессор выставляет 32-р адр на ША, АЗУ сравнивает М с М* загруженными в физ ОЗУ,если М=М*, то данная страница нах-ся в физ ОЗУ и № этой стр в физ ОЗУ задается полем К(4р), поле К возбуждает эту стр в физ ОЗУ, младш часть адреса L возбуждает ячейку памяти на выбранной странице, формируется сигнал Q который открывает буфер(Эл-т с 3 сост) и подключает физ ОЗУ с СМ. Если М≠М* это означает что данной стр в физ ОЗУ нет. Формируется сигнал Q который вызывает подп-рогр прерывания проц которой требуется загр недостающую стр внешн ЗУ (HDD) в физ ОЗУ,при этом необх-мо сделать следующее:

1)Анализируется поле признаков, проверяется поле v (v по сбросу сбрас в 0 изначально ЗУ пустое).Если осущ запись стр в физ ОЗУ в v устр 1. Чтобы уничножить стр достаточно v=0. Если v=0 значит в физ ОЗУ есть своб стр и на это место можно загр стр из внеш ЗУ .

2)Если все v=1 ,анализир признак старости стр R.Обычно признак старости R периодически сбрас в 0 по таймеру,при обращении к стр R автомат уст в 1.Если R=0 это значит что к данной стр давно не было обращений и на ее место можно загр требуемую стр, при этом возм след вариант:

а)Во время работы со старой стр команда записи не проходила, признак команды записи W=0 означает что точная копия этой стр нах-ся на винте => ее можно стирать в ОЗУ(v=0).

б)Проходила команда записи(w=1) означает что инф в ОЗУ отличается от копии на винте, тогда необходимо переписать инф с данной стр обратно на винт. Затем загрузить новую стр на место старой.

3)При работе со стр анализир-ся признаки приоритетов стр a и b.

|

a |

b |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

-только для чтения ОС

-чтение + запись ОС

-чтение польз-ля + все ОС

-чт/запись польз+все ОС

Если объем стр мал, прерывание на данную стр происходит часто, “закачивается” инф маленькими порциями, но если объем стр большой прерыв происх реже, но перегоняются большие объемы инф. Для орг вирт памяти требуются средства аппаратной поддержки.

20.Общие полож.Risc-проц.Берклинская арх.

В ВТ сущ правило80/20: 80% времени уходит на выполн 20% команд отполного набора инструкций процессора. Появилась задача изобретения ориентированного процессора. Перед разрабо-тчиками RISC-проц ставятся следующие задачи:

1)Выделяется область применения и класс решаемых задач, в этих задачах выделяются наиболее часто встречающиеся команды. Выделенные команды реализуются аппаратно с max возм быстродействием, обычно одна команда выполн за 1 такт. При этом использ простые способы адресации и простые инструкции.

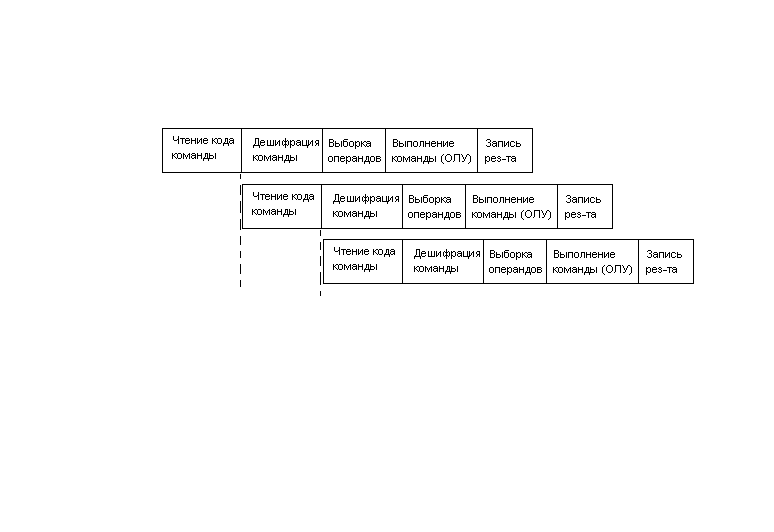

2)Если введение новых команд не требует существ аппаратных затрат, то они вводятся. Разр RISC-процессоров ориентируется на поддержку ЯВУ и на конвейерный тип выполнения команд. Условно выполнение любой команды можно разбить на фазы:

1 команда выполн 5 тактов, однако каждый след такт мы получаем рез-т. Все этапы выполн команды условно занимают одинаковый интервал времени. После заполнения конвейера за каждый такт на выходе имеем резкльтат=> высокая производительность.

Минус:команды должны быть одинаковы по времени.

Выполнение всех команд за одинаковое инт времени позволяет достигнуть высокой степени конвейеризации выполения процесса. Т.е. команды ктр не м/б выполнены за 1 такт реализуются на программном уровне с использованием стандартных библиотек. Основоположниками RISC архитектур явились ученые Берклинского и Старнфордского университетов.

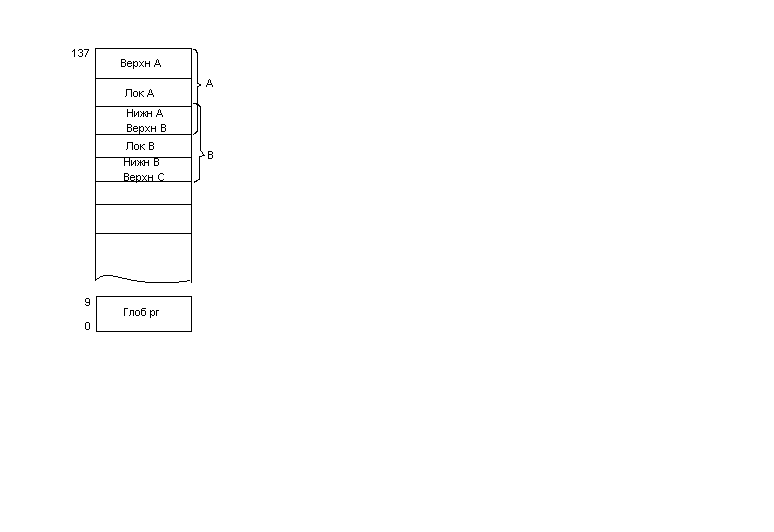

Берклинская архитектура.

Анализ работы ЭВМ показывает что основные затраты времени приходятся на обращение проц к памяти и ВУ. Разработчики Берк. арх для уменьшения числа обращений к внешн памяти решили хранить всю инф в кристалле, для этого они увеличили число РОНов.

RISC II – 138 РОНов.

При выполнении программы около 70% результатов полученных от выполн предыдущей команды использ при выполн сдлед ком-ды.

138 РОНов разбили на 8 виртуальных логических окон в каждый момент времени каждая подпрогр работает с одним Вирт окном, каждое окно содержит 32 РОНа.

|

Верхние регистры |

|

Локальные регистры |

|

Нижние регистры |

|

Глобальные регистры |

10

6

9 10

0

0

Нижн рг – результаты выполнен предыдущей команды и они явл верхн для след процедуры.

Глоб переменные доступные для всех процедур.

Все память РОНов поделена на пересекающиеся виртуальные регистровые окна, результат проц А нах-ся в нижн рег окна А которые одновр явл верхн рег окна В и служат исходной инф для процедуры В такая орг.перекр окон позволяет сократить число команд пересылок физ инф м/у РОНами.

Глобальные

регистры дотупны из любого виртуального

окна. Дальнейшее увеличение числа РОНов

приводит к увеличению паразитных

емкостей внутренне системной магистрали

(внутри кристалла). Это приводит к

снижению тактовой частоты процессора

Глобальные

регистры дотупны из любого виртуального

окна. Дальнейшее увеличение числа РОНов

приводит к увеличению паразитных

емкостей внутренне системной магистрали

(внутри кристалла). Это приводит к

снижению тактовой частоты процессора