- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

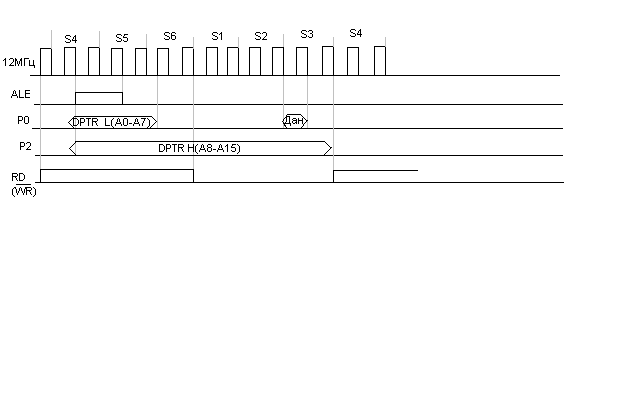

34.Протокол обмена подкл озу/пзу mcs-51

Обращение к внешней памяти данных

В протоколе обмена нет сигнала RDY (сигнал готовности для особо тупых), тактов ожидания, режима ПДП.

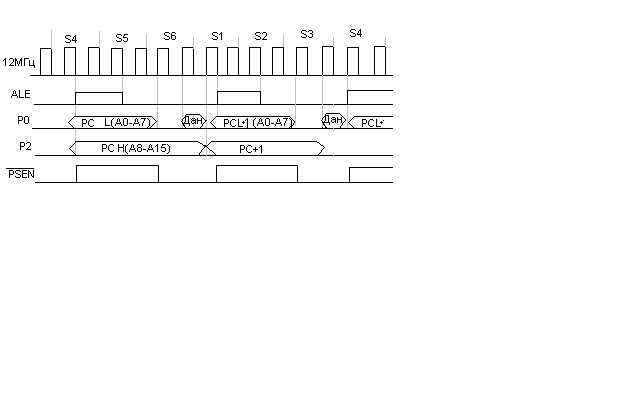

Обращение к внешней памяти прогр.

Обращение к внешней ПЗУ идет в 2 раза быстрее. При обращении к внешн памяти команд. на ША (Р0 Р2) выставл РС и считывание инф промсходит в 2 раза быстрее чем обращение к ОЗУ.

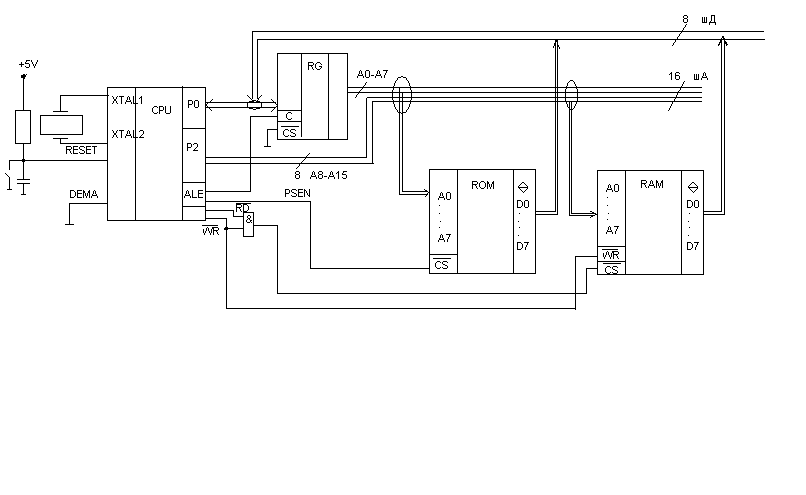

Подкл к СМ.

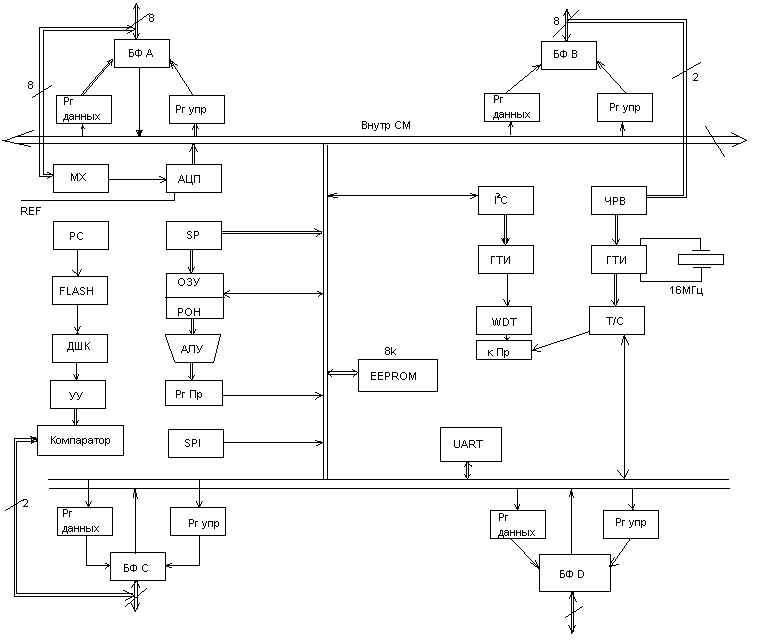

35.ATmega 32

8-разр RISC процессор с полным набором систмн команд (131 команда), включает операции * и /. Тактовая частота 16МГц, производительность 16млн опер. Опер умнож на число <1 -2 такта , остальные операции 1 такт.

Фирма совмещает 3 технологии на 1 кристалле:

Выполнен по КМОП технологии и целиком статический (частотаот 0-16МГц, в 0 почти не потребляет энергии). З2 кб флэш-память команд (структура Гарвардская). Флэш допусткает 10000 раз перепрошивку. 2кб-ОЗУ встроенное на кристалле, 32 РОНа.

2кб EEPROM – электрически стираемая и перепрограммируемая память(запись по байтам, допускает 100тыс циклов перепрограм-мирования, и служит как энергонезависимое ОЗУ (при при выкл питания хранит данные)). 10 разр встроенный АЦП (8 канальный). Встроенный аналоговый компаратор( сравнение напряжении япо уровню). 3 таймер-счетчика (2 8-ми разр,1 16-ти разр). 3 последовательных интерфейса UART, SPI, I2C. Встроенный 4 сторожевой таймер со встроенным внутр генератором. Часы реального времени. Встроенный контроллер прерываний. Все это нах-ся в корпусе DIP-40 (32 двунапр линии вв/выв с альтер-нативными функциями

![]() МХ- мультиплексор

МХ- мультиплексор

ЧРВ- часы реального времени

WDT- сторожевой таймер

к Пр- контроллер прерываний

T/C –таймер счетчик.(имеют 4 канала ЦАП постр по принципу широко-импульсной модуляции (PSW))

REF- внешнее опорное напряжение для АЦП.

36.Классификация оэвм по табл

T/C – количество таймеров

|

Фир-ма |

Тип |

Раз-рез. |

fт, МГц |

Кол-во 8р.|| п.вв-выв |

P потр. мВт |

|

Hita-chi |

H8/30 48F |

16 |

16 |

78 pin |

112 (20 мА) |

|

HD 64F 13052 |

16 |

18 |

70 pin |

120 | |

|

HD64 F7055 |

32 |

40 |

149 pin |

240 | |

|

Si-mens

|

SAKC 16316 F25F |

16 |

25 |

77 |

500 |

|

C167 |

16 |

20 |

111 |

500 | |

|

Micro-nas |

CDC 1607F |

16 |

12 |

~100 |

_ |

|

CDC 32076 |

32 |

24 |

~100 |

_ | |

|

Moto- rolla |

68HC 912D 6128 |

16 |

8 |

68 |

480 |

|

MCS- 555 |

32 |

40 |

20+ спец пор. |

1Вт |

|

Flash |

RAM |

T/C |

АЦП |

Посл. инт-с |

Прим. |

|

128кб |

4к |

6 |

10 (одн- кан) |

SCI |

кор- пуса 128 pin -40°C +85°C

|

|

512к |

8к |

9 |

8кан. ×10р |

SCI, I2C | |

|

512к |

32к |

34 |

16к. ×10р |

5 UA-RT, 2 SCI |

кор- пуса 176 pin -40°C +85°C

|

|

128к |

1к |

6 |

_ |

UA-RT, SPI |

100 pin -55° +125° |

|

128к |

4к |

10 |

16к. ×10р |

UA-RT, SCI |

144 -55° +125° |

|

256к |

6,5к |

6 |

9кан. ×10р |

UA-RT

|

128 pin -40°C +85°C

|

|

512к |

20к |

6 |

16к. ×10р |

UA-RT

| |

|

128к |

2к |

9 |

3к× 10 |

2SCI, SPI, I2C |

-40°C +85°C

|

|

448к |

26к |

До 60 |

32к× 10 |

SCI, SPI,2 CAN (лок. сети) |

275 pin |