- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

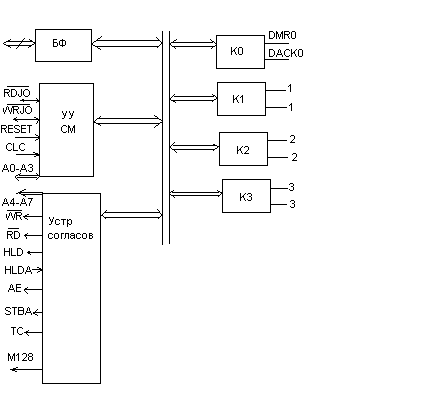

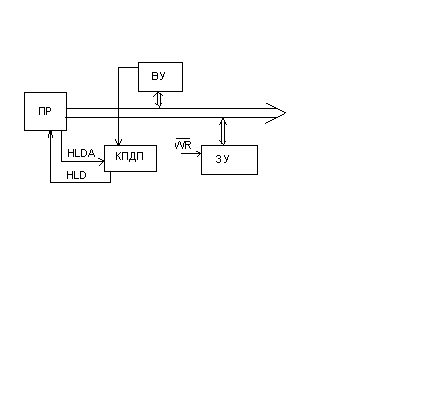

29.Контролер пдп.

Intel 82237

Центральная задача:

1)КПДП берет на себя функции управления СМ и формирование ША при отключении ЦП от СМ.

2)Осуществляет арбитраж между разными устройствами, запрашивающими режим ПДП.

Классическое периферийное устройство ВУ

DMR-запрос на ПДП от ВУ, DACK-разрешение на ПДП от ВУ, HLD-запрос от пр-ра, HLDA-разрешение от пр-ра.

Контролер всегда имеет в паре: RDJ0, WR,RD, WRJ0.

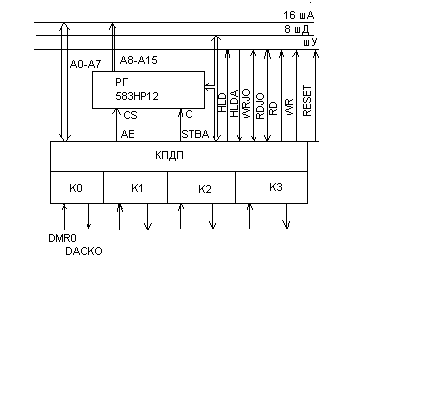

Контролер имеет 4 идент. канала К0-К3. Каждый канал содержит 16 разр. регистр адреса и 14 разр. счетчик циклов. По включении питания ЦП в программе нач. пуска (BIOS) прогр-т все периферийные микросхемы, в том числе контролер ПДП. В контролере ПДП проц для каждого канала (ВУ) задает нач. адрес (перв.ячейку памяти запис-ся в РгА канала) и задается число циклов(зап-ся число циклов в канал).Адрес формируется путем инкрементирования РгА (соот-но после каждого цикла число циклов декрементируется). Режим ПДП заканчивается, когда счетчик циклов=0. В этот момент времени формируется сигнал TC т.е. последний цикл. Максимальный размер этого блока=16 кбайт, т.к. счетчик циклов 14р, максимальный объем памяти перегоняемый в ПДП=214 или 16 кбайт (ПДП не может слишком долго, так как СМ занята и невозможна регенерация динам памяти).

Как контролер ПДП подключается к СМ: STBA-строб адреса.

При программировании контролера использ-ся разряды ША А0÷А3 и CS=0. Помимо прогр-я каждого канала в отдельности запис-ся управл-ее слово(только после того как все каналы запрогр-ся).

Управл-ее слово задает приоритеты между каналами, устанавливается флаги конца цикла ПДП в слове состояния (СС).

ЦП период-ки считывает СС контр-ра ПДП , в котором определяет происходил ли обмен инфой по конкретным каналам (т.е свежая ли проц инф и забран ли от проца готовый предыдущий рез-т). Если цикл ПДП прошел, обмен инфой состоялся, пр-р перепрограммирует контр-р по данному каналу(это делает ОС).

STBA стробирует адрес на ША.

М128-каждый 128 цикл формируется строб, длительностью один цикл.чтобы показать что система не зависла, а идут циклы ПДП.

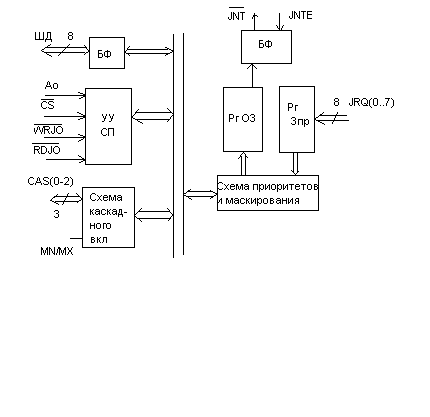

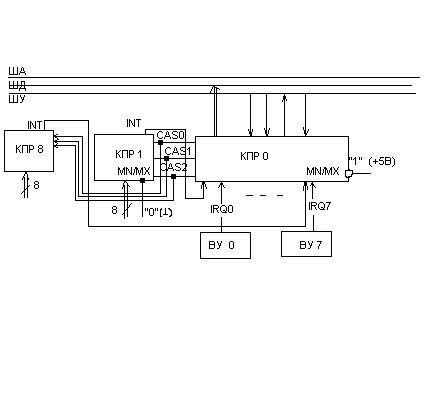

30.Прогр контр прерываний.

Intel 82259.

Контр прерываний (КП) предназначаен для задания адрес –векторов подпрогр обработки прерыванй от 8 до 64 (при каскадном включении контроллеров.

MN/MX-режим мин/макс включения(ведущий или ведомый)

Контроллер в процессе работы может нах-ся в одном из 3 реж:

1)Режим программирования, в этом реж-ме задается начальный адрес-вектор подпрогр обработки прерываний IRQ(0) каждое след прерывание отстоит от предыдущего на 8(16) адресов ячеек памяти. Задается вид приоритетов, разрешается или запрещается прерыв. Указ-ся что явл прерыв (полож фронт, отриц фронт, Ур 0, Ур 1). Если в системе нах-ся 1 контр то он явл ведущим и прор-ся своей группой команд если в сист-ме несколько контроллеров то ведущий котр и ведомый контр прогр по разному

Ведомый контроллер упр ведущим с помощью сигнала CAS0-CAS2, а их запрос на прерывание JNT поступает на один входов ведущего контроллера (а не на ЦП как у ведущего контр).

2)Режим обслуживания прерываний по опросу.

В режиме по опросу ЦП может периодически опрашивать регистр запросов и смотреть какие из ВУ требуют прерывания. Прогр высокого уровня сама определяет приоритеты и необх обслуживания поступивших запросов.

3)Режим обслуживания по запросу. ВУ выставляет запрос на прерыв ктр запоминв рег-ре запросов. Схема приоритетов и маскирования выбирает из всех поступивших запросов прерывания с высшим приоритетом, разрешенного для обслуживания. Это прерыв поступает в рег обрабатываемого запроса( РгОЗ). БФ формирует запрос на прерыв JNT=0 для ЦП. Если прерыв было разрешено на длинном участке прогр то ЦП преступает к обработке прерываний, устанавливая сигнал JNTE=0 (только после того как закончит выполнение команды). Получив сигнал JNTE=0 контр прерываний выставляет на ШД для ЦП код команды CALL (вызов подпрогр) после чего ЦП 2 раза дергает сигнал JNTEчтобы получить 16-разр адрес с 8 разр ШД. По 1 фронту выдается младший байт адреса подпрогр обработки прерыв , по2-му старший. В подпрогр о\обр прерыв в общем случае другие прерыв запрещены (вложенных прерыв нет) их можно разрешить специально) возвратиз подпрогр заканчивается командой RETI, которая разрешает следующее прерывание.