- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

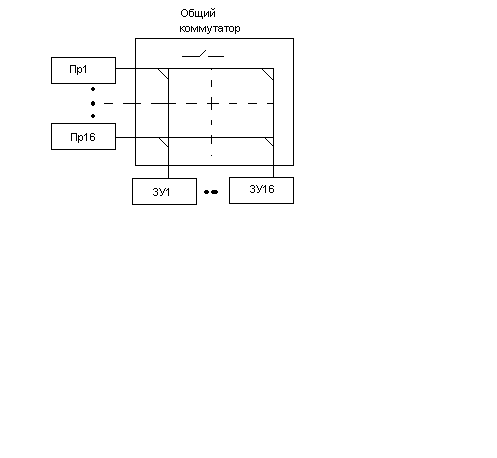

40.Архитектура Сммр,Сvмр,См.

1)Сmmр – разработчики универ Карнеги Меллона (США).

Перед разр стояла задача создать высоконадежную структуру позволяющую постепенно деградировать.

К аждый

проц может подкл к любому модулю память

и взять любые задачи для выполнения.

аждый

проц может подкл к любому модулю память

и взять любые задачи для выполнения.

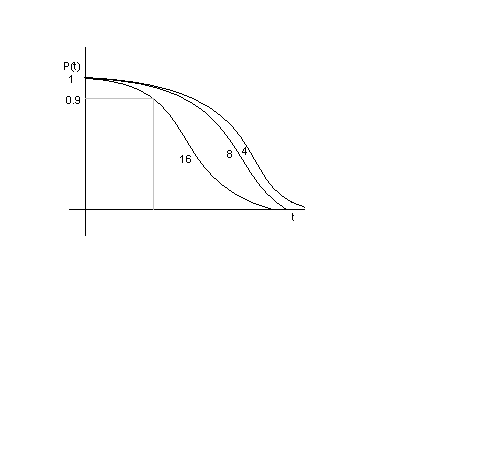

Р(t)- вероятность безотк работы системы.

8 -ми

проц сист-ма с резервированием.

-ми

проц сист-ма с резервированием.

Надежность невысокая из-за общего коммутато-ра. Резервирование с кра-

тностью более 2-х оказалось нецелесеобразн

.

С истема

с распреде-ленным коммутатором

истема

с распреде-ленным коммутатором

Увеличение надежности ≈ на порядок., но резервир с кратностью >2 все равно не целесеобразно.

-)Сложность наращивания и сложное управление комму-татором.

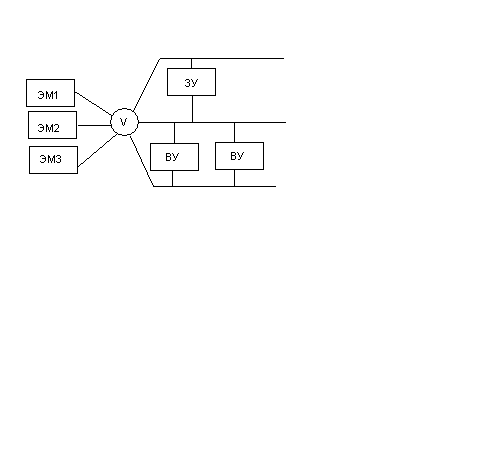

2)Cvmp- разраб те же.

Задача создать высоконадежный отказоустойчивый вычислитель при этом пользователь не должен знать что он высоконадежен.

С труктура

по принципу мажорирования, Эл-т сравненияV

который пропускает рез-т в сис-му в

случае его совпадения в 2-х машинах.

труктура

по принципу мажорирования, Эл-т сравненияV

который пропускает рез-т в сис-му в

случае его совпадения в 2-х машинах.

Осн дост:Система устой-чива к сбоям

В

ысоконадежный

вычис-литель парирует сбои в машинах.

Отказ одной машины пользователем не

замечается.

ысоконадежный

вычис-литель парирует сбои в машинах.

Отказ одной машины пользователем не

замечается.

Начиная с опр времени надежность Cmmp ста-новится выше надеж-ности Cvmp.

41.Сm структура.

1)Одномерный вариант.

+ )Легконастраиваемая

система. Каждая маш-на имеет доступ к

памяти любой другой машины.

)Легконастраиваемая

система. Каждая маш-на имеет доступ к

памяти любой другой машины.

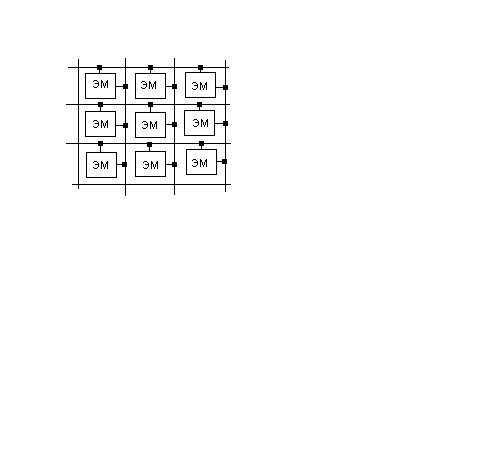

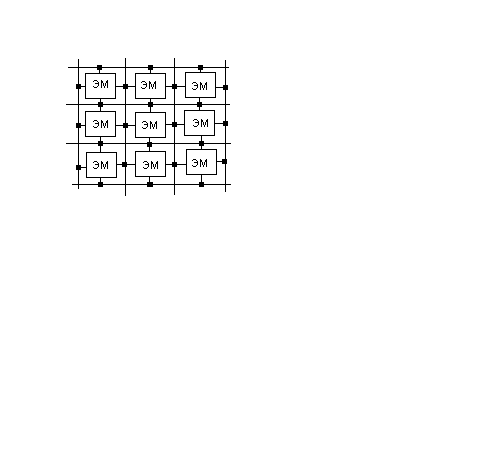

2)Двумерная структура

К аждая

машина имеет 4 порта.

аждая

машина имеет 4 порта.

(Inmos T424) –однокрист ЭВМ

(4 порта – 2 последов и 2 паралл,

8кб ОЗУ 8кб ПЗУ на кажд крист)

Высокая надежность простота распараллеливания алгоритмов.

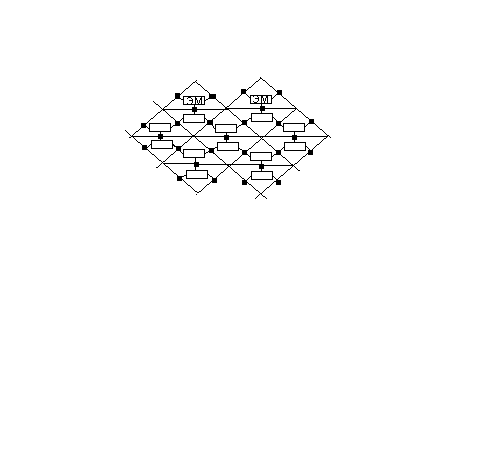

Университет города Пердью предложил структуру BlueChip :

ЭВМ с программируемой структурой.

Г отовый

набор, а конкретную структуру прожигают

под конкретный алгоритм (заказ).

отовый

набор, а конкретную структуру прожигают

под конкретный алгоритм (заказ).

Новосибирская структура “Сумма” Минимакс

![]()

1,2 –интерфейсы последователь-ные ч/з них задается как коммута-ция по параллельным интерфейсам 3,4. Перепрогр структура под конкр решаемые задачи.

В “Сумме” и “Минимаксе” с помощью последов интерфейсов зада-ется коммутация по парал интерф и под каждый конкретный алгоритм система перепрограммируется.

42. Понятие интерфейса. Виды арбитража

Интерфейс – это совок-ть аппаратных, программных и конструктивных ср-в, предназначенных для обмена инф-цией м/д различными цифровыми устр-вами. Под физ-кой линией связи понимается электропроводник, оптоволокно. Совок-ть линей связей, объединенных по функц-ному назначению наз-ся шиной.

В интерфейсе выделяют: 1)инф-ную магистраль (ША, ШД, Шсостояния) Различная информация на шинах мултиплексированна во времени, след-но исп-ся доп-ные идентифиц. сигналы. 2) ШУ инф-ной магистралью(сигналы идентификации, WR, RD, HLD, HLDA и др, Ш прерывания, Ш приоритетов (арбитража), спец-ные сигналы (биты четности))

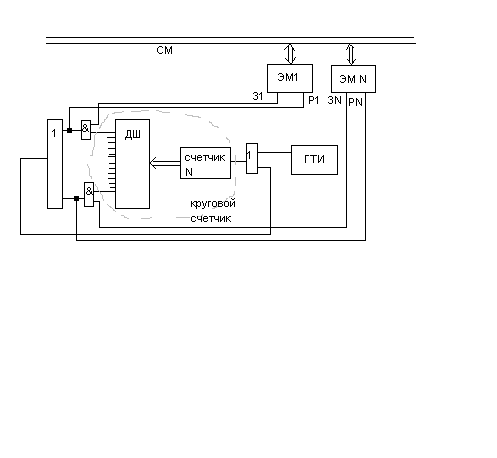

Функции арбитража

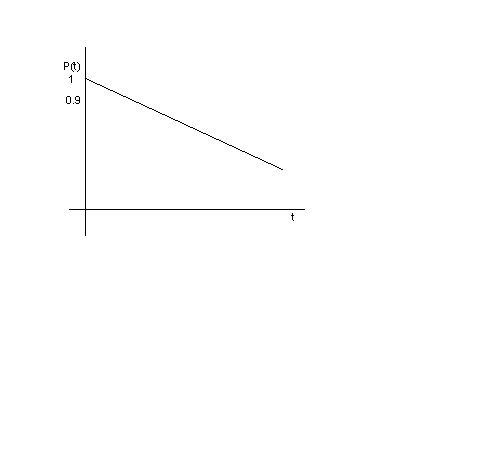

1)Временной арбитраж

Обычно интерфейс строится по принципу «ведомый-ведущий». Ведущая машина берет на себя фукции упр СМ.

ИБ каждого устр-ва имеет одинаковый счетчик, на вход к-рого подается один и тот же сигнал тактовой частоты. По RESET (системному сбросу) все счетчики сбрасываются в 0, что обозначает, что в каждый мом-т времени находится один код. Пусть счетчик 10 разрядный. 1-й машине предоставляется СМ, если код в счетчике от 0-100 и т.д. время предоставления СМ определяется важностью и объемом передаваемой информации. ДШ с выхода каждого счетчика подключает ИБ к СМ лишь в случае нахождения кода в данных пределах.

+![]() )Простота

и небольш апп затраты.

)Простота

и небольш апп затраты.

-)Нерациональн использ СМ.

2) Способ адресного сканирования

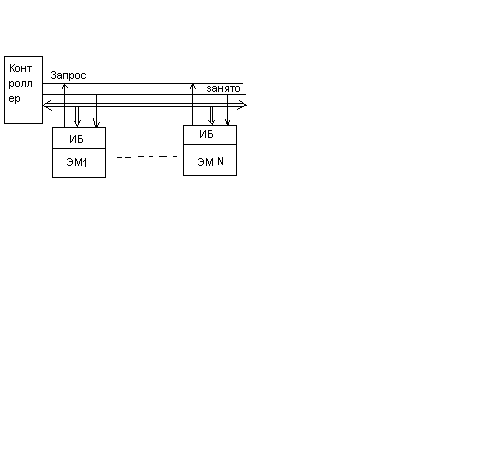

М ашинаN

выставляет запросы контроллера СМ.

Получив запрос, контроллер начинает

опрашивать по фиксированным адресам в

порядке убывания приоритетов интерфейсные

блоки машин, подключенных к СМ. При

нахождении машины, выставившей запрос,

контроллер формирует сигнал busy

и предоставляет СМ этой машине.

ашинаN

выставляет запросы контроллера СМ.

Получив запрос, контроллер начинает

опрашивать по фиксированным адресам в

порядке убывания приоритетов интерфейсные

блоки машин, подключенных к СМ. При

нахождении машины, выставившей запрос,

контроллер формирует сигнал busy

и предоставляет СМ этой машине.

+) рациональная загруженность СМ

-) интеллект. Контроллер . К-р можно перепрограммировать.

СМ освобождается при снятии запроса.

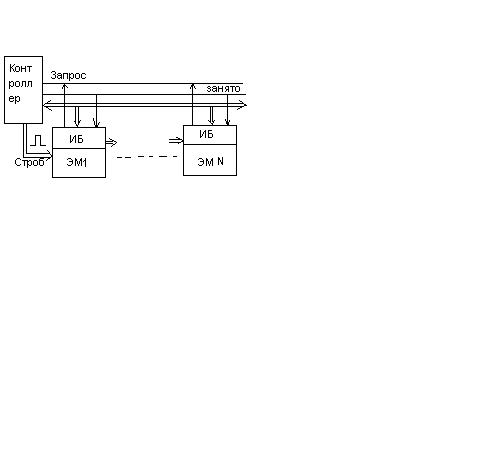

3) Цепочный арбитраж

![]()

Машина, которой необходима СМ выставляет сигнал запроса, контроллер формирует строб, который последовательно проходит через интерфейсные блоки всех машин, начиная с машины с высшим приоритетом. Если машина запрос не выставляла, интерфейсный блок пропускает его дальше и т.д. Если машина запрос выставила, интерфейсный блок блокирует дальнейшее прохождение стоба и выставляет сигнал busy.

+): аппаратные затраты минимальны, контроллер простой.

-_: устройство с низким приоритетом редко получают доступ к СМ, поэтому реально не делают больше 20 устройств

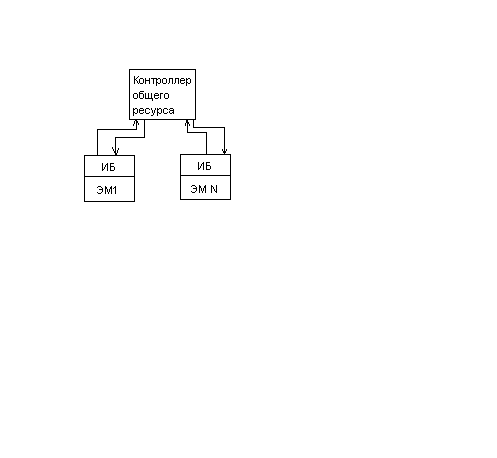

4)Способ радиальной селекции (арбитража)

Контроллер интеллектуальный, приоритеты гибкие, время доступа определено.