- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

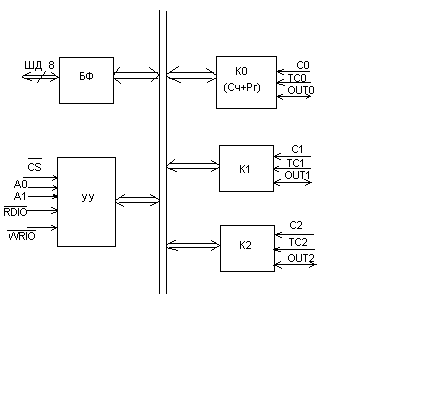

31.Таймер

82253 (580ВИ53)

Предназначен для формир временных интервалов. Использ в восновном для контроля правильности выполн программ и работоспособности прогр средств. Если через 64 такта никакого ответа на запрос не приходит выдается ошибка.

1)Вызывает прерывание при обращении к несущ и не инициализи-рованныв устройствам при отсутствии сигнала готовности.

2)Для организации контрольных точек

3)Ограничивает длительность захвата одним устр общих ресурсов.

Таймер представляет собой три независимых канала

Каждый канал содержит 16разр таймер-счетчик и регистр и может работать в двоичном коде или в двоично-десятичном коэфф пересчета 216-104. Каждый из каналов может работать в одном из 6-ти режимов

0)Программируемая задержка или режим терминального счета.С-входные импульсы(надо считать) ТС-разрешение счета OUT- выход счетчика. В счетчик загружается код,после загр кода OUT=0 по установке сигнала TC=1 счетчик начинает декрементироваться с приходом каждого тактового импульса С. Если в момент счета установит ТС=0 то счетчик прекращает реагировать на импкльсы С. По возвращении ТС=1 счетчик продолжает с того момента где остановился. По окончании счета устанавл OUT=1.

1)Режим ждущего мультивибратора. Счетчик запускается в работу полож фронтом сигнала ТС .Если во время счета приходит новый импульс ТС то счетчик перезапускается с самого начала.

2)Генератор импульсов. В счетчик загр код, OUT=1 по окончании счета в течении одного периода С устанавл OUT=0 затем счет продолжается с самого начала.

3)Генератор Миандра. Используется как делитель тактовой частоты С на коэффициент загр в счетчик. (OUT=0 по длительности равно OUT=1).

4-5)Два последних режима: управление идет от фронтов сигнала ТС (остальное как у 2,3)

32.Орг эвм типа ibm pc at

8086

80186

80286

80386

80486

L-шина обладает пониженным напряж питания(напр пит ЦП)

S-шина нормальная магистраль 5В. Первое поколение- ISA шины следующее PCI. Как вариант PCI была шина VESA.

М-шина (шина подкл памяти)

Х-шина обращения к ВУ.

ША/2-потому что динамич память (адр строки, адр столбца)

Базовый магистральный кристалл VL82C100- контроллер ВУ (84 конт, 2 контр ПДП 82237, 2 контр прерываний, таймер)

VL82C101-сист контр(генератор тактовык импульсов 8224, сист контр 88238,СППЗ 80287) с пониженным питанмем.

VL82C102-контроллер ДОЗУ

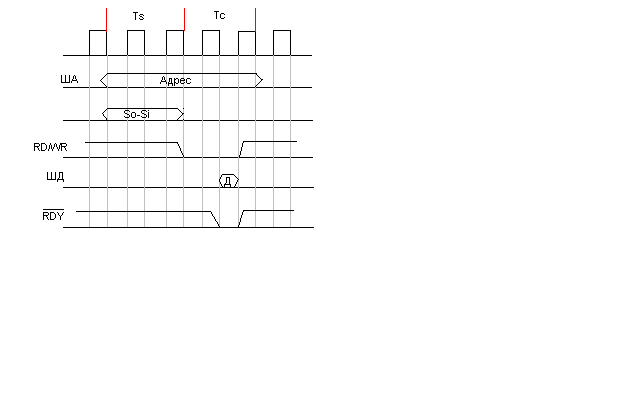

Протокол обмена по системной шине ISA (такой же как у про-цессора 1810ВМ86) каждый обмен выполн за 4 такта. 1 такт состояния 2 такт-командный.

Любая ЭВМ содержит: ЦП, ГТИ, модули ПЗУ, модули ОЗУ, таймер, контролер прерыв(м/б и ПДП), устр упр вв/выв (ППИ), устр последов вв/выв.

Если все эти устр-ва установить на одном кристалле то получится однокристальная ЭВМ (транспьютер).

33,Однокристальн эвм

Микроконтроллеры 4 разр. Их прямое назначение:

1)Калькуляторы 2)Пульты ДУ 3)ИК интерфейс.

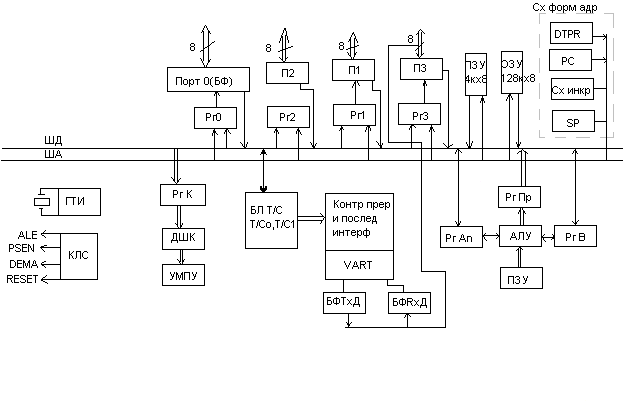

Intel MCS51

Это контроллер клавиатуры, таймер видеомагнитофонов. 8051 n-МОП технология где 0 вид ПЗУ, 0-ПЗУ масочного изг с фиксированной прошивкой. 3-ПЗУ однопрограммируемое ПЗУ(8351) 7-ПЗУ сУльтрафиол стиранием(30-50раз) 9-Flash память (1000-10000 перепрогр).

8х31- где 31-внутреннего ПЗУ нет, есть возможность подкл внешн ПЗУ.

8хС51 где С – КМОП технология 20мА.

Наиболее популярна МС89С51.

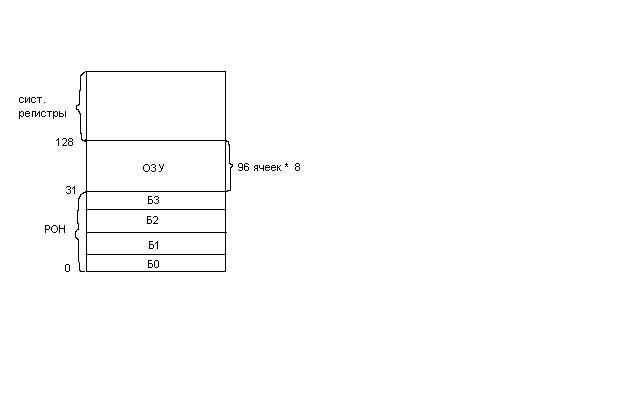

Контроллер имеет 4 || универсальных 8-разр порта, каждый из которых имеет альтернативную функцию. Кристалл гарвардского типа: память команд и данных раздельна. При обращении к данным использ Рг DTPR встроенное ОЗУ-128b ПЗУ-4kb. Имеется возм подкл внешнего ПЗУ 64kb и ОЗУ 64kb. Проц имеет 111 команд включая команды * и /. Есть возможность побитной установки и обработки разрядов портов и флагов. В проце содерж 32 РОНа. Они делятся на 4 банка и карта адреса выглядит след образом: в спец Рг задается какой банк РОНов работает.

RS0-RS1

указывает на номер банка.

RS0-RS1

указывает на номер банка.

80Н-порт 0

equ-порт 0=80Н обращение к ячейке 80Н

89Н ТМОD – установка режима таймера.

Блок таймеров содержит 2 16-ти разр многофукц таймера (0-3 режима). ГТИ: 12MHz за 12 тактов 1 команда в режиме таймера.

Контр прерыв и послед инткрф обр 5 разл прерываний (2 внешних, 2тиаймера и послед интерф). Посл интерф работает в полудуплексном реж-ме и поддерж стандарт протоколы обмена типа RS. Порт 0 исп-ся для ввода вывода байта(как обычный Рг +ШФ), в альтернативном реж-ме порт 0 обеспечивает формирование младшего байта адр и прием данных пр подкл внешн ОЗУ и ПЗУ. Порт 2 то же самое сто и порт 0 но при подкл внешн ОЗУ и ПЗУ формир старш байт адр. Порт 1 вв/выв 8 сигналов, альтернатив нет. Порт 3 каждый бит имеет альтернативную функцию. Dip40- 40 ножек. Альтернативные функции: TxD,RxD –сигнал послед-го интерфейса. T/C0,T/C1-сигналы таймера, сч-ка; RD,WR –чтение/запись при обращении к внеш. памяти данных или внеш. ОЗУ; INT0, INT1- прерыв. по внеш событиям; ALE-строб адреса, по сигналу ALE происходит защелкивание адреса (порта 0) во внешний Рг при обращении в внешн памяти прогр или данных. PSEN- сигнал чтения из внешн памяти прогр. DEMA- 0-блокировка внутр ПЗУ,работа в внешт ПЗУ, 1-наоборот.