- •1.Процессоры. Иерархия языков вт

- •Иерархия языков вт

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •4.Алу для деления чисел с фиксир(,)

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •8.Управл автоматы с мпу

- •9.Требования к кодам команди способы кодирования.

- •11.Шинные формирователи и рег-ры. Орг см 580 серии

- •Организация см процессора

- •12.Организация модулей пзу

- •13.Организация модулей статического озу.

- •16-Ти разрядные модули памяти

- •14.Организация динамических модулей дозу

- •15.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •16.Синхр способ продкл ву к см

- •17.Асинхр способ продкл ву к см

- •18.Организация кэш памяти.

- •19.Организация виртуальной памяти.

- •20.Общие полож.Risc-проц.Берклинская арх.

- •21.Старнфордсая структура

- •22.Машины упр потоками данных(df-машины)

- •23.Pentium

- •24.Pentium II,Pentium Pro

- •25.Pentuim VI

- •27.М/о ч/з ппи.

- •28.Усапп

- •29.Контролер пдп.

- •30.Прогр контр прерываний.

- •31.Таймер

- •32.Орг эвм типа ibm pc at

- •33,Однокристальн эвм

- •34.Протокол обмена подкл озу/пзу mcs-51

- •35.ATmega 32

- •36.Классификация оэвм по табл

- •35.Вс классификация по Флинну

- •38.Производительность эвм и сетей.

- •38.Типовые структуры вс

- •40.Архитектура Сммр,Сvмр,См.

- •41.Сm структура.

- •42. Понятие интерфейса. Виды арбитража

- •43.Арбитраж по последовательному опросу.

- •44. Контроллер прерываний по последовательному опросу

- •45.Арбитраж по || опросу.

- •46.Синхронизация информации в интерф.

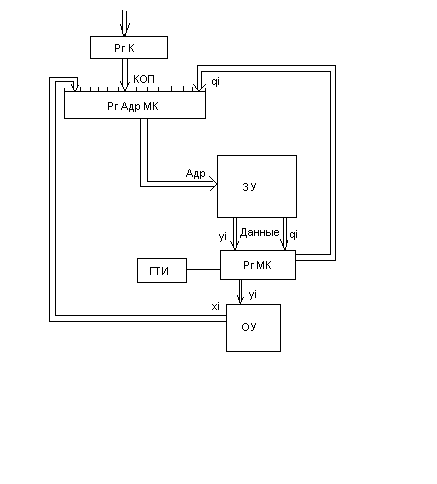

8.Управл автоматы с мпу

КОП-код операции qi-сост упр автомата (адр след МК)(КОП-const,

xi-const) ОУ- операционное устройство.

Код команды процессора записыв-ся в Рг.МК , этот код здает в Рг.Адр.МК область памяти ЗУ в ктр прошита МПрогр данной ком, соотв-но для каждого вида операций(другого кода ком-ды) в памяти МП выделяется своя область т.к. при выполн. МП в зависимости от признаков сост ОУ xi формир разл последов упр возд yi,то они так же оказыв влияние на адрес формиров-я след-го yi т.к. при неизменном коде опер и условиях xi возникает необход в формиров последов-ти yi , то в ЗУ прописыв-ся адрес следующ yi (адрес qi)которое формируется на следующ шаге (программный счетчик). Если в качестве ЗУ использ ПЗУ то процессор имеет жестко заданную сист команд (все микропроц-ры широкого прим так и работают) но в общем случае в место ПЗУ можно использ ОЗУ тогда проц-р можно перенастраивать под различные сист-мы команд (напр сделать совместными проги под Intel и Motorola (Mac)).

Достоинства: 1)Каждая ком имеет свою область памяти микропрограмм(измен одной ком не приводит к необх переделки остальн ком) 2)Для выполн каждой ком-ды выделяется столько времени сколько необх-мо (длительности выполн всех команд различны и минимальны)

9.Требования к кодам команди способы кодирования.

Код команды должен соотв требованиям:

1)Указывать на код операции

2)Указывать на адрес(адреса) одного(неск) операндов участв в выполнении команды.

3)Указывать на адрес,куда помещается результат выполнения

4)Указывать на ардрес след команды

Способы:

1)Горизонтальное кодирование.При гориз кодир каждому упр возд yi выдел-ся свой разряд в Рг.МК.

|

y1 |

y2 |

… |

. |

yn |

+: высокое быстродейтсв(в любо мом времени можно выполн любой у или несколько)

- : высокие аппаратные затраты

2)Вертикальное кодирование.

в Рг.МК. запис двоичн код или номер yi ктр необх выполн.

-: одно упр возд yi в ед времени

+:низкие аппаратные затраты.

3)Вертикально-гориз микропрограмм-е.

Вся совокупность упр возд yi делится на К подгрупп наиболее часто выполняемык одновременно yi.

К

К

|

y1…………yn |

|

К – двоичный код N подпр. (задается верт) a yi в подгр – горизонт

4)Горизонтально-верикальное микропрогр

Всё множ-во упр возд yi разбив-ся на К подгр по принципу несовместных команд или встр очень редко.

N групп-гориз

yi – вертикально

Высокое быстр и высокие аппратные затраты.

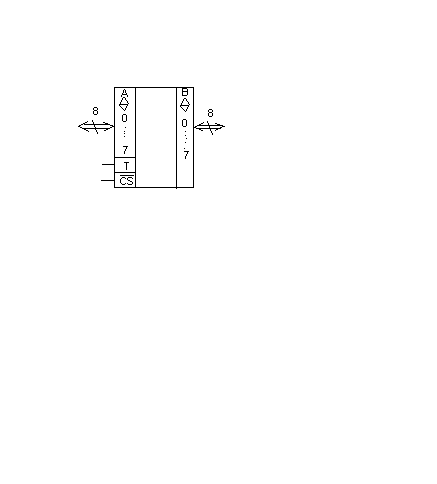

11.Шинные формирователи и рег-ры. Орг см 580 серии

Шинные формиров-ли-микросх с 3 сост предназн для согласования, увеличения нагр способнотси и подкл разл устр к СМ.

3 сост-эквивалент разомкнутого ключа,сост с высоким импедансом.

___

C S

– chip

select,

выборка кристалла или включение

микросхемы в работу

S

– chip

select,

выборка кристалла или включение

микросхемы в работу

|

CS |

T |

Направл |

|

1 |

Х |

Х |

|

0 |

0 |

A->B |

|

0 |

1 |

B->A |

1553АП6

ИР-Регистры-устр для временно проме-жуточного хранения инф.Любой Рг имеет CS и синхр. ОЕ-output enable – снятие 3 сост-хранимая инф идет на выход.

__

CS=1 на выходе 3 сост микросх не раб