- •Логическая основа вс

- •Сумматоры

- •8. Типовые кцу (шифраторы и дешифраторы)

- •9. Типовые кцу (мультиплексоры и де мультиплексоры)

- •10. Этапы синтеза кцу

- •11. Последовательностные цифровые устройства –пцу. Определение, формы задания , математическая модель пцу

- •Типовые триггеры

- •14. Типовые пцу — счетчики (суммирующие, вычитающие и реверсивные). Их функционирование показать временными диаграммами.

- •15. Типовые пцу - регистры (памяти и сдвига), универсальные, реверсивные

- •Основные типы сдвигов

- •16. Цифро-аналоговые преобразователи сигналов, реализованные на матрице двоично- взвешенных резисторах

- •17. Цифро-аналоговые преобразователи сигналов, реализованные на матрице r — 2r

- •18. Аналого-цифровые преобразователи, реализованные на принципе последовательного приближения

- •19. Аналого-цифровые преобразователи, реализованные на принципе последовательного счета

- •21.22. 23. Классификация полупроводниковых запоминающих устройств (озу и пзу). Типы озу. Типы пзу.

- •25. Статические озу (их реализация)

- •26. Динамические озу (их реализация)

- •27. Организация пзу

- •31. Декомпозиция мп

- •32. Принцип аппаратного управления («жесткой» логики)

- •33. Принцип микропрограммного управления («гибкой» логики)

- •34. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой.

- •39. Элементы архитектуры мп.

- •40. Структура команд мп.

- •41 Способы адресации, основанные на прямом использовании кода команды.

- •42 Способы адресации, основанные на преобразовании кода команды

- •43 Понятие вектора состояния мп.

- •44 Понятие системы прерывания программ

- •45 Характеристики системы прерывания

- •46. Способы организации приоритетного обслуживания запросов прерывания.

- •47. Программный, циклический и цепочечный способы опроса

- •48. Цепочечная однотактная схема ("дейзи-цепочка")

- •49.Два способа реализации программно-управляемого приоритета прерывающих программ, использующих порог и маски прерывания

- •51. Конвейерная обработка команд и данных.

- •53. Система ввода-вывода (интерфейсы)

- •56. Прямой доступ к памяти.

- •57. Контроллер пдп выполняет следующие функции:

- •58. Методы передачи информации между устройствами вычислительной системы.

- •59. Методы передачи информации между устройствами вычислительной системы (со стробированием и квитированием)

- •61.Структура ввода-вывода с одним общим интерфейсом

- •62.Мп структура с множеством интерфейсов и каналами ввода-вывода

- •63.Необходимость использования нескольких специализированных интерфейсов (Интерфейс основной (оперативной) памяти, интерфейс процессор-каналы,интерфейс ввода-вывода, интерфейсы периферийных устройств)

- •64. Три категории программного обеспечения (по) : системное, технического обслуживания и прикладное.

14. Типовые пцу — счетчики (суммирующие, вычитающие и реверсивные). Их функционирование показать временными диаграммами.

Двоичным счётчиком называется ПЦУ, которое подсчитывает число поступающих на его вход тактовых импульсов и выдает результат в виде двоичного числа.

Основным информационным параметром счётчиков является модуль счёта (коэффициент пересчёта). Модуль счёта КС определяет максимальное число тактовых импульсов, которое может быть сосчитано счётчиком. Таким образом, максимальный модуль счета n-разрядного двоичного счётчика равен 2n.

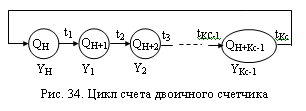

В процессе счёта тактовых импульсов t1,

t2, t3, …

счётчик последовательно проходит КС

состояний, включая начальное состояние

QН (рис. 34). При этом на

выходе счётчика формируется

последовательность двоичных чисел YH,

Y1, Y2 …, в

которой каждое последующее число

отличается от предыдущего на 1. КС-м

тактовым импульсом счётчик возвращается

в начальное состояние (говорят,

переполняется), после чего цикл счёта

повторяется.

процессе счёта тактовых импульсов t1,

t2, t3, …

счётчик последовательно проходит КС

состояний, включая начальное состояние

QН (рис. 34). При этом на

выходе счётчика формируется

последовательность двоичных чисел YH,

Y1, Y2 …, в

которой каждое последующее число

отличается от предыдущего на 1. КС-м

тактовым импульсом счётчик возвращается

в начальное состояние (говорят,

переполняется), после чего цикл счёта

повторяется.

Базовыми элементами любого счётчика являются Т- и ТV-триггеры, которые аппаратно могут быть реализованы на D- или JK-триггерах.

По направлению счёта различают суммирующие, вычитающие и реверсивные счётчики. Любой из них в зависимости от способа организации цепей синхронизации может быть асинхронным или синхронным.

Суммирующие счётчики с каждым тактом увеличивают свое состояние на 1. Стандартным начальным состоянием считается нулевое состояние счетчика.

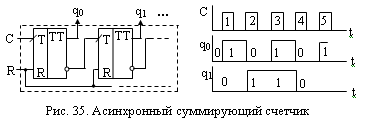

А синхронный

счетчик строится путем соединения

выхода предыдущего триггера со счетным

входом последующего (рис. 35). На рис. 35

приведены также временные диаграммы,

иллюстрирующие динамику работы счетчика

при стандартном начальном состоянии.

По фронту первого тактового импульса

младший триггер переходит в единичное

состояние, формируя на инверсном выходе

перепад напряжения из 1 в 0. Поскольку

этот перепад пассивен для данного типа

триггеров, второй триггер сохраняет

предыдущее нулевое состояние. В результате

на выходе счетчика образуется двоичное

число 01 (110). Фронт второго тактового

импульса возвращает младший триггер в

нулевое состояние. При этом на его

инверсном выходе формируется перепад

напряжения из 0 в 1, который переключает

второй триггер в единичное состояние.

В результате на выходе счетчика образуется

двоичное число 10 (210). Фронт третьего

тактового импульса переводит счетчик

в третье состояние – на выходе двоичное

число 11 (310). Четвертым тактовым импульсом

счетчик переполняется, то есть возвращается

в нулевое (начальное) состояние, после

чего процесс счета повторяется.

синхронный

счетчик строится путем соединения

выхода предыдущего триггера со счетным

входом последующего (рис. 35). На рис. 35

приведены также временные диаграммы,

иллюстрирующие динамику работы счетчика

при стандартном начальном состоянии.

По фронту первого тактового импульса

младший триггер переходит в единичное

состояние, формируя на инверсном выходе

перепад напряжения из 1 в 0. Поскольку

этот перепад пассивен для данного типа

триггеров, второй триггер сохраняет

предыдущее нулевое состояние. В результате

на выходе счетчика образуется двоичное

число 01 (110). Фронт второго тактового

импульса возвращает младший триггер в

нулевое состояние. При этом на его

инверсном выходе формируется перепад

напряжения из 0 в 1, который переключает

второй триггер в единичное состояние.

В результате на выходе счетчика образуется

двоичное число 10 (210). Фронт третьего

тактового импульса переводит счетчик

в третье состояние – на выходе двоичное

число 11 (310). Четвертым тактовым импульсом

счетчик переполняется, то есть возвращается

в нулевое (начальное) состояние, после

чего процесс счета повторяется.

На основе проведенного анализа можно сформулировать схемотехнические принципы работы суммирующего счетчика:

для любого суммирующего счетчика переключение i-го триггера возможно, только если все предыдущие триггеры находятся в состоянии единицы;

в асинхронном счетчике каждый последующий триггер может переключиться только после переключения предыдущего.

Из последнего пункта следует, что каждое двоичное число на выходе асинхронного счетчика формируется во времени последовательно разряд за разрядом, начиная с младшего.

Этот процесс эквивалентен распространению переноса при арифметическом сложении двоичного числа с единицей. Поэтому счетчики, у которых сигнал управления переключением триггеров распространяется последовательно, называются счетчиками с последовательным переносом.

О чевидно,

что наибольшее время, в течение которого

на выходе асинхронного счетчика

установится очередной результат равно

чевидно,

что наибольшее время, в течение которого

на выходе асинхронного счетчика

установится очередной результат равно

n , где – среднее время задержки переключения триггера по счетному входу, а n – число разрядов (триггеров) счетчика.

Н аибольшее время между изменением сигнала на входе и завершением образования соответствующего сигнала на выходе называется быстродействием цифрового устройства. В частности, быстродействие счетчиков характеризуется наибольшей допустимой частотой следования тактовых импульсов, которая для асинхронного счетчика определяется отношением 1/(n ) Гц.

Синхронные счетчики отличаются от асинхронных параллельным соединением счетных входов всех триггеров (рис. 36). Логические элементы обеспечивают выполнение первого пункта схемотехнических принципов работы суммирующего счетчика.

Триггеры синхронного счетчика переключаются одновременно, следовательно, одновременно будут изменяться и значения разрядов двоичного числа на его выходе. Однако сигнал разрешения по V-входу триггеров все же распространяется последовательно от первого логического элемента ко второму, от второго к третьему и т.д., проходя цепочку из n-1 логических элементов, где n – разрядность счетчика. Действительно, если два младших триггера установились в состояние 1, то сигнал разрешения на V-входе третьего триггера появится с задержкой на время переключения первого логического элемента. Если и третий триггер находится в состоянии 1, то сигнал разрешения на V-входе четвертого триггера появится с задержкой на время переключения уже двух логических элементов и т.д.

Т аким

образом, во-первых, данная схема также

является счетчиком с последовательным

переносом. Во-вторых, следующий такт

может начаться не раньше, чем через

время

аким

образом, во-первых, данная схема также

является счетчиком с последовательным

переносом. Во-вторых, следующий такт

может начаться не раньше, чем через

время

+ (n–1) * где – среднее время задержки переключения логического элемента.

П оскольку

< данный счетчик по

сравнению с асинхронным обладает бóльшим

быстродействием.

оскольку

< данный счетчик по

сравнению с асинхронным обладает бóльшим

быстродействием.

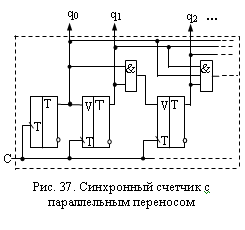

Д альнейшее повышение быстродействия возможно лишь за счет организации параллельного переноса (рис. 37).

Быстродействие такого счетчика определяется суммой +

и не зависит ни от числа триггеров, ни от

числа логических элементов. Однако

число входов логических элементов

увеличивается от разряда к разряду. Тем

самым нарушается регулярность

(однотипность) структуры счётчика, что

снижает технологичность его изготовления

в виде интегральной микросхемы. Поэтому

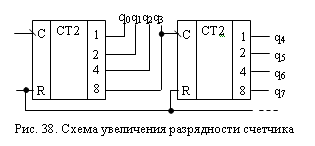

в интегральном исполнении счетчики с

параллельным переносом выпускаются не

более чем 4-разрядными, а построение на

их основе счетчиков большей разрядности

производится по схеме рис. 38. Там же

показано и условное графическое

обозначение интегральных суммирующих

счетчиков, где выходы счётчика помечаются

весовыми коэффициентами двоичных

разрядов, а вход сброса R

является входом первого приоритета

не зависит ни от числа триггеров, ни от

числа логических элементов. Однако

число входов логических элементов

увеличивается от разряда к разряду. Тем

самым нарушается регулярность

(однотипность) структуры счётчика, что

снижает технологичность его изготовления

в виде интегральной микросхемы. Поэтому

в интегральном исполнении счетчики с

параллельным переносом выпускаются не

более чем 4-разрядными, а построение на

их основе счетчиков большей разрядности

производится по схеме рис. 38. Там же

показано и условное графическое

обозначение интегральных суммирующих

счетчиков, где выходы счётчика помечаются

весовыми коэффициентами двоичных

разрядов, а вход сброса R

является входом первого приоритета

В ычитающие

счётчики с каждым тактом уменьшают свое

состояние на 1. Стандартным начальным

состоянием считается единичное состояние

счетчика.

ычитающие

счётчики с каждым тактом уменьшают свое

состояние на 1. Стандартным начальным

состоянием считается единичное состояние

счетчика.

Вычитающие счетчики легко получаются из суммирующих. Для этого достаточно лишь в качестве выходов счетчика использовать противоположные выходы триггеров. Других изменений в схеме суммирующего счетчика не требуется.

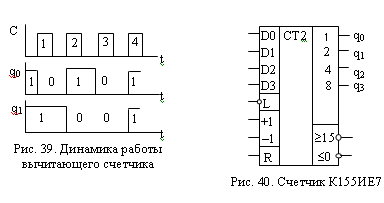

П ринцип

работы вычитающего счетчика вполне

ясен из временных диаграмм двухразрядного

счетчика при стандартном начальном

состоянии, управляемого фронтом тактового

импульса (рис. 39). Как видно, единственной

особенностью вычитающего счетчика

является переход из нулевого состояния

в единичное.

ринцип

работы вычитающего счетчика вполне

ясен из временных диаграмм двухразрядного

счетчика при стандартном начальном

состоянии, управляемого фронтом тактового

импульса (рис. 39). Как видно, единственной

особенностью вычитающего счетчика

является переход из нулевого состояния

в единичное.

Реверсивные счётчики обладают возможностями суммирующего и вычитающего счётчиков.

Условное графическое обозначение интегральных реверсивных счетчиков показано на примере микросхемы К155ИЕ7 (рис. 40). Режим суммирования задаётся подачей тактовых импульсов на вход +1, а режим вычитания – на вход -1. Вход L предназначен для предварительной установки счетчика в заданное 1 исостояние. Активный сигнал на этом входе блокирует счетные входы двоичное число с входов D переписывается на выход. Таким образом, вход L 15 активный сигналявляется входом второго приоритета. На выходе переноса 0 – припоявляется при единичном состоянии счётчика, а на выходе займа нулевом. Эти выходы обычно используются для построения многоразрядного 0 предыдущей микросхемы15 и реверсивного счётчика. При этом выходы (счетчика младших разрядов) соединяются, соответственно, с входами +1 и -1 последующей микросхемы (счётчика старших разрядов).

В интегральном исполнении выпускаются суммирующие счетчики – асинхронные и синхронные с параллельным переносом, а также реверсивные счетчики.-- В маркировке микросхем счетчиков используются буквы ИЕ.