- •Логическая основа вс

- •Сумматоры

- •8. Типовые кцу (шифраторы и дешифраторы)

- •9. Типовые кцу (мультиплексоры и де мультиплексоры)

- •10. Этапы синтеза кцу

- •11. Последовательностные цифровые устройства –пцу. Определение, формы задания , математическая модель пцу

- •Типовые триггеры

- •14. Типовые пцу — счетчики (суммирующие, вычитающие и реверсивные). Их функционирование показать временными диаграммами.

- •15. Типовые пцу - регистры (памяти и сдвига), универсальные, реверсивные

- •Основные типы сдвигов

- •16. Цифро-аналоговые преобразователи сигналов, реализованные на матрице двоично- взвешенных резисторах

- •17. Цифро-аналоговые преобразователи сигналов, реализованные на матрице r — 2r

- •18. Аналого-цифровые преобразователи, реализованные на принципе последовательного приближения

- •19. Аналого-цифровые преобразователи, реализованные на принципе последовательного счета

- •21.22. 23. Классификация полупроводниковых запоминающих устройств (озу и пзу). Типы озу. Типы пзу.

- •25. Статические озу (их реализация)

- •26. Динамические озу (их реализация)

- •27. Организация пзу

- •31. Декомпозиция мп

- •32. Принцип аппаратного управления («жесткой» логики)

- •33. Принцип микропрограммного управления («гибкой» логики)

- •34. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой.

- •39. Элементы архитектуры мп.

- •40. Структура команд мп.

- •41 Способы адресации, основанные на прямом использовании кода команды.

- •42 Способы адресации, основанные на преобразовании кода команды

- •43 Понятие вектора состояния мп.

- •44 Понятие системы прерывания программ

- •45 Характеристики системы прерывания

- •46. Способы организации приоритетного обслуживания запросов прерывания.

- •47. Программный, циклический и цепочечный способы опроса

- •48. Цепочечная однотактная схема ("дейзи-цепочка")

- •49.Два способа реализации программно-управляемого приоритета прерывающих программ, использующих порог и маски прерывания

- •51. Конвейерная обработка команд и данных.

- •53. Система ввода-вывода (интерфейсы)

- •56. Прямой доступ к памяти.

- •57. Контроллер пдп выполняет следующие функции:

- •58. Методы передачи информации между устройствами вычислительной системы.

- •59. Методы передачи информации между устройствами вычислительной системы (со стробированием и квитированием)

- •61.Структура ввода-вывода с одним общим интерфейсом

- •62.Мп структура с множеством интерфейсов и каналами ввода-вывода

- •63.Необходимость использования нескольких специализированных интерфейсов (Интерфейс основной (оперативной) памяти, интерфейс процессор-каналы,интерфейс ввода-вывода, интерфейсы периферийных устройств)

- •64. Три категории программного обеспечения (по) : системное, технического обслуживания и прикладное.

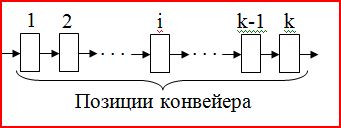

51. Конвейерная обработка команд и данных.

Принцип конвейерной обработки начнём рассматривать с конвейера команд.

Пусть рабочий цикл МП состоит из k этапов, причём i-й этап имеет продолжительность ti. Тогда при последовательном выполнении этапов длительность цикла определяется суммой

ТПОСЛ = , а общая производительность процессора РПОСЛ = 1/ операций/с.

Скорость работы МП может быть увеличена, если для выполнения каждого этапа ввести отдельный аппаратурный блок:

Блоки соединить так, чтобы результат выполнения некоторого этапа в данном блоке передавался для реализации очередного этапа на следующий блок и т.д.

Полученная таким образом обрабатывающая линия, и называется конвейером.

Конвейер называется синхронным, если он работает в принудительном темпе и для выполнения любого этапа выделено одно и то же время tТ (такт конвейера).

В этом случае разбиение цикла на этапы и выбор длительности такта производятся согласно условиям:

tТ = max{ti}, i = 1,…, k; (максимальная из длительностей этапов)

ti + ti+1 > tТ, i = 1,…, k.

Если для каких-либо смежных этапов второе условие не выполняется, то их следует объединить в один этап либо наиболее длинный этап разбить на несколько этапов. В последнем случае заново выбирается tТ и вновь проверяется первое условие.

После того как все позиции конвейера окажутся заполненными, параллельно во времени будет обрабатываться k команд.

Действительно, в момент заполнения конвейера в k-ой позиции обрабатывается k-й этап первой команды, в (k-1)-й позиции – (k-1)-й этап второй команды и т.д., в первой позиции – первый этап k-й команды.

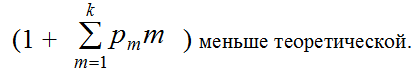

Теоретически соотношение производительностей процессора при конвейерной обработке и при последовательном выполнении этапов рабочего цикла и имеет вид: k/2 < (PКОНВ/РПОСЛ) <= k.

В действительности рост производительности МП оказывается ниже из-за простоев конвейера.

Так, при выполнении команд пересылки данных отдельные этапы рабочего цикла отсутствуют и, следовательно, простаивают отдельные блоки конвейера. Для команд условного перехода несколько тактов простаивает весь конвейер, т.к. выборка следующей команды должна быть задержана, пока не будет сформирован признак результата предыдущей операции (формируется на более позднем этапе).

Таким образом, если pm – вероятность выборки команды, вызывающей задержку конвейера на m тактов (m = 1, 2,…, k), то действительная производительность конвейера будет в

При большой зависимости продолжительностей выполнения отдельных этапов от типа команды целесообразно применение асинхронного конвейера.

В асинхронном конвейере команд нет единого такта работы его блоков.

Информация передаётся с одного блока конвейера на следующий, когда данный и следующий блоки полностью закончат свои процедуры.

Управление передачей информации между соседними блоками асинхронного конвейера осуществляется с помощью двух триггеров – триггера готовности блока (сигнализирует о завершении операции в данном блоке) и триггера освобождения последующего блока.

В целях повышения производительности МП принцип конвейерной обработки широко используется и в АЛУ, которые строятся в виде арифметического конвейера, причём таких арифметических конвейерных линий в процессоре может быть несколько.

Подобные операционные устройства часто называют магистральными.

Пусть операционное устройство должно вычислять некоторую функцию Ф от входных данных.

Эту функцию можно представить в виде последовательности более простых подфункций:

j1j®2®. . . j®k.

Результаты преобразования, выполняемые подфункцией j i, используются в качестве входных данных при вычислении подфункции j i+1.

Если при этом для каждой подфункции иметь реализующий её схемный блок, то получим арифметический конвейер, который может быть выполнен как синхронным, так и асинхронным.

При использовании арифметического конвейера для выполнения разных операций усложняется определение состава блоков конвейера и может потребоваться настройка с соответствующей коммутацией блоков на операцию, задаваемую текущей командой.

В ряде МП одновременно присутствуют конвейер команд и арифметический конвейер.

52. Особенности RISC-архитектуры.

Развитие архитектуры МП во многих случаях идёт по пути их усложнения: расширяется система команд, увеличивается число используемых способов адресации, вводятся сложные команды, которые выполняют процедуры, приближающиеся к примитивам языков высокого уровня и т.д.

Однако при этом порождается ряд нежелательных побочных эффектов:

1.Увеличивается длина кода команды и в первую очередь её операционная часть, что чревато увеличением числа форматов команд. В результате усложняется и замедляется процесс дешифрации кода операции, а также других процедур обработки команд.

2.Возрастающая сложность процедур обработки команд, в свою очередь, заставляет прибегать к управляющим устройствам с "гибкой" логикой вместо более быстродействующих управляющих устройств с "жёсткой" логикой.

3.Усложнение процессора делает более трудным или даже невыполнимым реализацию его на одном кристалле, что могло бы облегчить достижение высокой производительности.

Указанные негативные стороны процесса развития архитектуры привели к формированию альтернативного направления, использующего RISC-архитектуру (аббревиатура RISC раскрывается как ЭВМ с сокращённым набором команд).

RISC-архитектура предполагает реализацию в процессоре сокращённого набора простейших, но часто употребляемых команд, что позволяет упростить аппаратурные средства процессора и, как результат, повысить его быстродействие.

При использовании RISC-архитектуры выбор системы команд и структуры МП направлены на то, чтобы команды выполнялись за один машинный цикл МП. Выполнение более сложных, но редко встречающихся операций обеспечивают подпрограммы.

В микропроцессорах с RISC-архитектурой машинным циклом называют время, в течение которого производится выборка двух операндов из регистров, выполнение операции в АЛУ и запоминание результата в регистре

Характерными особенностями RISC-архитектуры являются сокращённый набор команд (не более 50 – 100), небольшое число (обычно 2 – 3) простых способов адресации (в основном регистровой) и небольшое число простых форматов команд, размер и функциональное назначение полей которых фиксированы.

В результате устройство управления процессора упрощается и может быть выполнено на "жёсткой" логике.

Кроме того, появляется возможность увеличения на кристалле числа общих и специализированных регистров до нескольких десятков и даже сотен.

Большое число регистров позволяет до предела сократить количество обращений к внешней памяти для реализации таких операций, как сохранение промежуточных результатов, передача операндов из одних программ в другие программы или подпрограммы, сохранение вектора состояния при прерываниях.

Таким образом, большинство команд в RISC-архитектуре являются быстрыми командами типа "регистр – регистр".

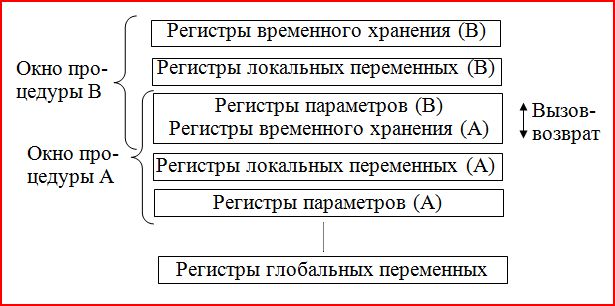

Ещё одной особенностью RISC-архитектуры является механизм перекрывающихся регистровых окон, предназначенный для уменьшения числа обращений к оперативной памяти и межрегистровых передач, что способствует повышению производительности процессора.

Суть механизма заключается в следующем.

Процедурам динамически выделяются небольшие группы регистров фиксированной длины (регистровые окна).Каждое окно состоит из трёх подгрупп регистров:

Первая подгруппа содержит параметры, переданные данной процедуре В от её вызвавшей, и результаты для вызывающей процедуры при возврате в неё.

Вторая подгруппа содержит локальные переменные данной процедуры.

Третья подгруппа является буфером для двустороннего обмена между данной и вызываемой ею следующей (А) процедурами.

Эта подгруппа передаёт вызываемой процедуре (А) параметры от данной, которая, в свою очередь, получает через этот буфер результаты от ею вызванной процедуры.

Таким образом, одна и та же подгруппа для данной процедуры является регистрами временного хранения, а для следующей – регистрами параметров.

Отдельное окно, доступное всем процедурам программы, выделяется для её глобальных переменных.

Примером процессоров, созданных на основе RISC-архитектуры, является однокристальный МП 80860 фирмы Intel, который практически представляет собой кремниевый эквивалент суперЭВМ Gray-1.

Примером ЭВМ с RISC-архитектурой является высокопроизводительный персональный компьютер IBM PC-RT, имеющий 118 команд, всего 2 способа адресации и 2 формата команд, 16 общих регистров, среднее число циклов на команду 3.