- •Логическая основа вс

- •Сумматоры

- •8. Типовые кцу (шифраторы и дешифраторы)

- •9. Типовые кцу (мультиплексоры и де мультиплексоры)

- •10. Этапы синтеза кцу

- •11. Последовательностные цифровые устройства –пцу. Определение, формы задания , математическая модель пцу

- •Типовые триггеры

- •14. Типовые пцу — счетчики (суммирующие, вычитающие и реверсивные). Их функционирование показать временными диаграммами.

- •15. Типовые пцу - регистры (памяти и сдвига), универсальные, реверсивные

- •Основные типы сдвигов

- •16. Цифро-аналоговые преобразователи сигналов, реализованные на матрице двоично- взвешенных резисторах

- •17. Цифро-аналоговые преобразователи сигналов, реализованные на матрице r — 2r

- •18. Аналого-цифровые преобразователи, реализованные на принципе последовательного приближения

- •19. Аналого-цифровые преобразователи, реализованные на принципе последовательного счета

- •21.22. 23. Классификация полупроводниковых запоминающих устройств (озу и пзу). Типы озу. Типы пзу.

- •25. Статические озу (их реализация)

- •26. Динамические озу (их реализация)

- •27. Организация пзу

- •31. Декомпозиция мп

- •32. Принцип аппаратного управления («жесткой» логики)

- •33. Принцип микропрограммного управления («гибкой» логики)

- •34. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой.

- •39. Элементы архитектуры мп.

- •40. Структура команд мп.

- •41 Способы адресации, основанные на прямом использовании кода команды.

- •42 Способы адресации, основанные на преобразовании кода команды

- •43 Понятие вектора состояния мп.

- •44 Понятие системы прерывания программ

- •45 Характеристики системы прерывания

- •46. Способы организации приоритетного обслуживания запросов прерывания.

- •47. Программный, циклический и цепочечный способы опроса

- •48. Цепочечная однотактная схема ("дейзи-цепочка")

- •49.Два способа реализации программно-управляемого приоритета прерывающих программ, использующих порог и маски прерывания

- •51. Конвейерная обработка команд и данных.

- •53. Система ввода-вывода (интерфейсы)

- •56. Прямой доступ к памяти.

- •57. Контроллер пдп выполняет следующие функции:

- •58. Методы передачи информации между устройствами вычислительной системы.

- •59. Методы передачи информации между устройствами вычислительной системы (со стробированием и квитированием)

- •61.Структура ввода-вывода с одним общим интерфейсом

- •62.Мп структура с множеством интерфейсов и каналами ввода-вывода

- •63.Необходимость использования нескольких специализированных интерфейсов (Интерфейс основной (оперативной) памяти, интерфейс процессор-каналы,интерфейс ввода-вывода, интерфейсы периферийных устройств)

- •64. Три категории программного обеспечения (по) : системное, технического обслуживания и прикладное.

Сумматоры

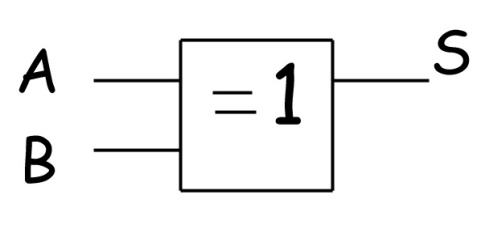

Сумматоры — это комбинационные устройства, предназначенные для сложения двух входных двоичных кодов. Например, арифметическая сумма кодов 0111 (число 7) и 0101 (число 5) равна 1100 (число 12). Арифметическая сумма кодов 1101 (число 13) и 0110 (число 6) равна 10011 (число 19), т. е. сумма двух двоичных чисел с числом разрядов n может иметь результат с числом разрядов n + 1. Этот дополнительный (старший) разряд называется выходом переноса (Р). На схемах сумматоры обозначаются буквами SM. Микросхемы сумматоров кодируются буквами ИМ. Рассмотрим таблицу истинности сложения двух одноразрядных двоичных чисел без учёта переноса: S =AB+AB Устройство, реализующее эту функцию, называется " исключающее ИЛИ":

Схема не информирует о бите переноса.

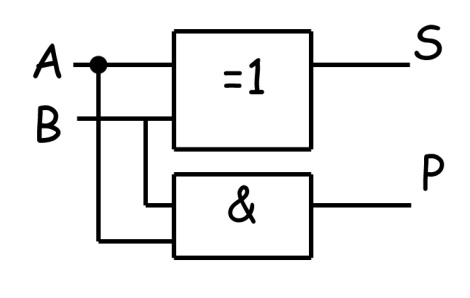

Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значение входных чисел А и В, значение результата суммирования S и значения переноса в старший разряд Р:

Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями: S = AB+AB и Р = АВ Устройство, реализующего таблицу истинности, содержит " исключающие ИЛИ" и конъюнктор " И"

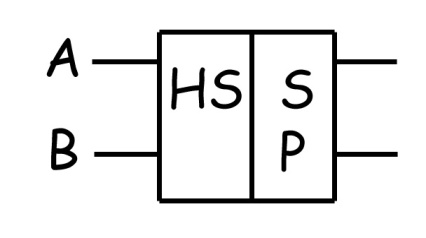

Это устройство называется полусумматором и изображается в виде:

Устройства называются полусумматором, т. к. имеет только два входа и не воспринимается сигнал переноса от других микросхем. Он используется только в младшем разряде. Рассмотрим сложение двух одноразрядных двоичных чисел с учётом бита переноса от других микросхем:

Работа

устройства, реализующего таблицу

истинности, описывается следующими

уравнениями:

S=ABPn-1+ABPn-1+ABPn-1+ABPn-1

Pn=ABPn-1+ABPn-1+ABPn-1+ABPn-1

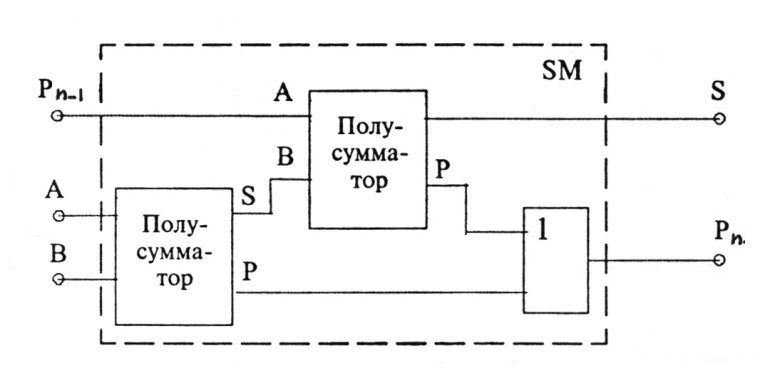

Устройство,

реализующие таблицу, содержит два

полусумматора и дизъюнктор " ИЛИ":

Работа

устройства, реализующего таблицу

истинности, описывается следующими

уравнениями:

S=ABPn-1+ABPn-1+ABPn-1+ABPn-1

Pn=ABPn-1+ABPn-1+ABPn-1+ABPn-1

Устройство,

реализующие таблицу, содержит два

полусумматора и дизъюнктор " ИЛИ":

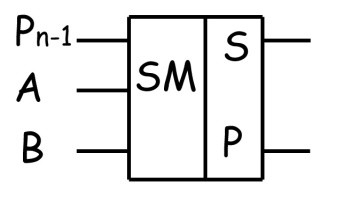

Это устройство называется одноразрядным сумматором и имеет следующее условное графическое обозначение:

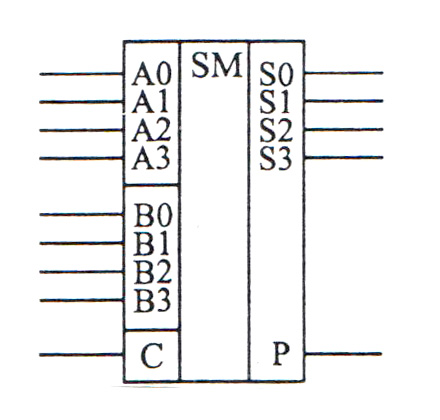

Сумматоры бывают одноразрядные (для суммирования двух одноразрядных чисел) двухразрядные (суммируют двухразрядные числа) и четырёхразрядные (суммируют четырёхразрядные числа). Чаще всего применяют 4 — х разрядные:

Вход С (вход расширения) для объединения нескольких сумматоров с целью увеличения разрядности

8. Типовые кцу (шифраторы и дешифраторы)

Дешифратором называется КЦУ, преобразующее n-разрядное двоичное число на входе в активный сигнал на одном из m выходов.

Основное назначение дешифраторов – формирование управляющих сигналов.

Дешифратор с n входами и m = 2n выходами называется полным, а в случае m < 2n – неполным (частично определенное КЦУ).

На рис. 16 приведено условное графическое обозначение дешифраторов на примере полного дешифратора 2 4 (n = 2, m = 4) со стробированием (вход V) и инверсными выходами (активным нулевым выходным сигналом).

И нформационные

входы обозначаются весовыми коэффициентами

двоичных разрядов, что устанавливает

однозначное соответствие между номером

входа дешифратора и номером разряда

двоичного набора. Для выходов используется

сквозная нумерация.

нформационные

входы обозначаются весовыми коэффициентами

двоичных разрядов, что устанавливает

однозначное соответствие между номером

входа дешифратора и номером разряда

двоичного набора. Для выходов используется

сквозная нумерация.

Таблица истинности полных дешифраторов, ограниченная дешифратором рис. 16, показана на рис. 17. Из таблицы видно, что номер выхода, на котором появляется активный сигнал, является десятичным эквивалентом текущего двоичного набора на информационных входах. В маркировке микросхем дешифраторов используются буквы ИД.

Шифратором называется КЦУ, преобразующее активный сигнал на одном (неприоритетный шифратор) или нескольких (приоритетный шифратор) из n информационных входов в m-разрядное двоичное число на выходе.

Шифраторы используются в устройствах ввода информации в цифровые системы и устройства.

Шифратор с m выходами и n = 2m входами называется полным, в противном случае – неполным (частично определенное КЦУ). На рис. 18 приведено условное графическое обозначение шифраторов на примере полного шифратора 4 2 (n = 4, m = 2) с инверсными входами (активным нулевым сигналом на входе). Для входов используется сквозная нумерация, а выходы обозначаются весовыми коэффициентами двоичных разрядов, что позволяет правильно определить двоичное число на выходе шифратора.

Т аблица

истинности неприоритетного и приоритетного

(значения входов указаны в скобках)

полных шифраторов, ограниченная

шифратором рис. 18, показана на рис.

19. Из таблицы следует, что двоичное

число на выходе неприоритетного

шифратора соответствует десятичному

номеру активного входа. Для приоритетного

шифратора допускается наличие активного

сигнала одновременно на нескольких

входах. В этом случае двоичное число на

выходе соответствует наибольшему по

номеру активному входу. Из таблицы также

видно, что шифраторам свойственна

неопределенность: одно и то же двоичное

число на выходе образуется как при

активном старшем входе, так и пассивных

всех входах. Если к тому же шифратор

дополняется входом стробирования,

образуется еще одна неопределенность:

в режиме блокирования все выходы

шифратора тоже будут установлены в

единичное значение. Для идентификации

этих ситуаций в интегральных шифраторах

предусматриваются два служебных выхода.

аблица

истинности неприоритетного и приоритетного

(значения входов указаны в скобках)

полных шифраторов, ограниченная

шифратором рис. 18, показана на рис.

19. Из таблицы следует, что двоичное

число на выходе неприоритетного

шифратора соответствует десятичному

номеру активного входа. Для приоритетного

шифратора допускается наличие активного

сигнала одновременно на нескольких

входах. В этом случае двоичное число на

выходе соответствует наибольшему по

номеру активному входу. Из таблицы также

видно, что шифраторам свойственна

неопределенность: одно и то же двоичное

число на выходе образуется как при

активном старшем входе, так и пассивных

всех входах. Если к тому же шифратор

дополняется входом стробирования,

образуется еще одна неопределенность:

в режиме блокирования все выходы

шифратора тоже будут установлены в

единичное значение. Для идентификации

этих ситуаций в интегральных шифраторах

предусматриваются два служебных выхода.

В маркировке микросхем шифраторов используются буквы ИВ