- •Логическая основа вс

- •Сумматоры

- •8. Типовые кцу (шифраторы и дешифраторы)

- •9. Типовые кцу (мультиплексоры и де мультиплексоры)

- •10. Этапы синтеза кцу

- •11. Последовательностные цифровые устройства –пцу. Определение, формы задания , математическая модель пцу

- •Типовые триггеры

- •14. Типовые пцу — счетчики (суммирующие, вычитающие и реверсивные). Их функционирование показать временными диаграммами.

- •15. Типовые пцу - регистры (памяти и сдвига), универсальные, реверсивные

- •Основные типы сдвигов

- •16. Цифро-аналоговые преобразователи сигналов, реализованные на матрице двоично- взвешенных резисторах

- •17. Цифро-аналоговые преобразователи сигналов, реализованные на матрице r — 2r

- •18. Аналого-цифровые преобразователи, реализованные на принципе последовательного приближения

- •19. Аналого-цифровые преобразователи, реализованные на принципе последовательного счета

- •21.22. 23. Классификация полупроводниковых запоминающих устройств (озу и пзу). Типы озу. Типы пзу.

- •25. Статические озу (их реализация)

- •26. Динамические озу (их реализация)

- •27. Организация пзу

- •31. Декомпозиция мп

- •32. Принцип аппаратного управления («жесткой» логики)

- •33. Принцип микропрограммного управления («гибкой» логики)

- •34. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой.

- •39. Элементы архитектуры мп.

- •40. Структура команд мп.

- •41 Способы адресации, основанные на прямом использовании кода команды.

- •42 Способы адресации, основанные на преобразовании кода команды

- •43 Понятие вектора состояния мп.

- •44 Понятие системы прерывания программ

- •45 Характеристики системы прерывания

- •46. Способы организации приоритетного обслуживания запросов прерывания.

- •47. Программный, циклический и цепочечный способы опроса

- •48. Цепочечная однотактная схема ("дейзи-цепочка")

- •49.Два способа реализации программно-управляемого приоритета прерывающих программ, использующих порог и маски прерывания

- •51. Конвейерная обработка команд и данных.

- •53. Система ввода-вывода (интерфейсы)

- •56. Прямой доступ к памяти.

- •57. Контроллер пдп выполняет следующие функции:

- •58. Методы передачи информации между устройствами вычислительной системы.

- •59. Методы передачи информации между устройствами вычислительной системы (со стробированием и квитированием)

- •61.Структура ввода-вывода с одним общим интерфейсом

- •62.Мп структура с множеством интерфейсов и каналами ввода-вывода

- •63.Необходимость использования нескольких специализированных интерфейсов (Интерфейс основной (оперативной) памяти, интерфейс процессор-каналы,интерфейс ввода-вывода, интерфейсы периферийных устройств)

- •64. Три категории программного обеспечения (по) : системное, технического обслуживания и прикладное.

11. Последовательностные цифровые устройства –пцу. Определение, формы задания , математическая модель пцу

Последовательностным называется цифровое устройство с памятью, в котором текущие двоичные сигналы на выходе зависят как от текущих двоичных сигналов на входе, так и от предыдущих состояний устройства.

Под состоянием ПЦУ понимается двоичная информация, считываемая из его памяти в данный момент времени.

ПЦУ синхронизируются тактовыми импульсами и работают циклами, автоматически переходя с каждым тактом из одного состояния в другое, формируя при этом на выходе определенные двоичные сигналы. Каждый цикл всегда начинается и заканчивается некоторым заранее определенным начальным состоянием.

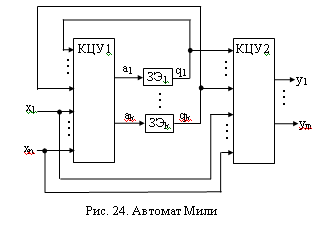

Наиболее общей моделью ПЦУ является автомат Мили (рис. 24). Запоминающие элементы (ЗЭ) хранят все состояния цикла работы ПЦУ в заданной последовательности в виде k-разрядных двоичных наборов. КЦУ1 в зависимости от текущих сигналов Х = {xi} на входе и текущего состояния Q = {qj} ПЦУ вырабатывает двоичные сигналы а1, …, аК управления памятью. Эти сигналы определяют состояние, в которое ПЦУ перейдёт в следующем такте. КЦУ2 в зависимости от текущих двоичных сигналов на входе и текущего состояния ПЦУ вырабатывает выходные двоичные сигналы.

Автомат Мили задаётся двумя системами логических функций: функций переходов Qt+1 = f(Xt, Qt) и функций выходов Yt = φ(Xt, Qt), где индекс t соответствует текущему такту цикла, а (t+1) – последующему. Однако на практике часто оказывается достаточной более простая модель, в которой отсутствует связь КЦУ2 с входом ПЦУ. В этом случае функции выходов упрощаются: Yt = φ(Qt). Такая модель называется конечным автоматом Мура

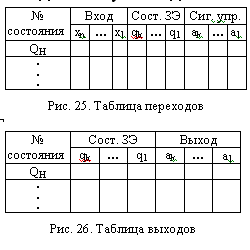

Ф

ункции

переходов определяют состояние ПЦУ в

следующем такте и позволяют синтезировать

КЦУ1. Задаются они в виде таблицы переходов

(рис. 25). Заполняется она, начиная с

начального состояния QН,

соответствующего ну-левому такту. В ее

строках записываются соответствующие

двоичные наборы. При этом значения

управляющих сигналов выбираются из

условия обеспечения следующего состояния

ПЦУ.

ункции

переходов определяют состояние ПЦУ в

следующем такте и позволяют синтезировать

КЦУ1. Задаются они в виде таблицы переходов

(рис. 25). Заполняется она, начиная с

начального состояния QН,

соответствующего ну-левому такту. В ее

строках записываются соответствующие

двоичные наборы. При этом значения

управляющих сигналов выбираются из

условия обеспечения следующего состояния

ПЦУ.

Функции выходов определяют выходной двоичный набор в текущем такте и позволяют синтезировать КЦУ2. Задаются они в виде таблицы выходов (рис. 26).

Обычно обе таблицы объединяются в одну, которая называется автоматной таблицей. Однако автоматная таблица не отражает динамику поведения ПЦУ. Поэтому для пояснения работы ПЦУ автоматную таблицу дополняют временными диаграммами

12. Элементарные ПЦУ -триггеры, их классификация, таблицы функционирования

Основными компонентами ПЦУ являются запоминающие элементы, которые реализуются специальными устройствами – триггерами.

Триггер – это одноразрядный элемент памяти, предназначенный для хранения одного бита информации. Основной способ построения триггеров – использование обратных связей. Именно за счёт них обеспечивается возможность запоминания.

Любой триггер имеет два выхода – прямой и инверсный, но состояние триггера определяется сигналом на прямом выходе. Число входов в зависимости от типа триггера может составлять от двух до пяти.

13. Синхронные и асинхронные триггеры

По способу приема информации различают асинхронные и синхронные триггеры. Синхронные триггеры записывают бит информации только при наличии активного (разрешающего) сигнала на входе синхронизации. Пассивное значение синхросигнала определяет режим хранения триггера. Асинхронные триггеры не имеют входа синхронизации и записывают бит информации в момент его подачи на информационные входы.

Синхронные триггеры могут быть со статическим или динамическим управлением по входу синхронизации. При статическом управлении активным является уровень логического 0 (инверсный синхровход) или логической 1 (прямой синхровход). На условном графическом обозначении триггера инверсный синхровход показывается кружочком , а прямой – без кружочка . При динамическом управлении активным является фронт или срез синхроимпульса. На условном графическом обозначении триггера фронт показывается прямой косой линией , а срез – обратной .

По функциональным возможностям различают триггеры с раздельной установкой состояний 0 и 1 (RS-триггер), с приёмом информации по одному входу D (D-триггер), универсальный с информационными входами J и K (JK-триггер) и со счётным входом Т (Т-триггер).