- •1. Основные принципы работы цп. Машина фон Неймана.

- •2. Аппаратные прерывания pc,обрабатываемые bios. Общая характеристика.

- •1. Ввод-вывод по опросу. Временные диаграммы, особенности программной реализации.

- •В ывод информации Процессор выставляет данные в порт и считывает

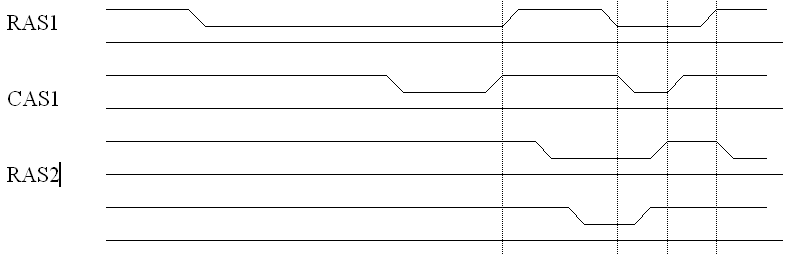

- •2. Способы организации пдп: «прозрачный» режим.

- •2. Способы организации пдп: метод захват цикла.

- •1. Прямой доступ к памяти. Общая характеристика.

- •2. Особенности разработки по в системах с прерываниями.

- •2. Типовые временные диаграммы обработки аппаратного прерывания на примере любого микропроцессора.

- •1. Сравнительная характеристика методов ввода-вывода.

- •По опросу:

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Организация прерываний в ibm pc. Аппаратная часть. Обработка аппаратных прерываний.

- •Билет n 7

- •2. Стандартный контроллер пдп. Общая характеристика

- •2. Ввод-вывод по прерываниям. Достоинства и недостатки.

- •2. Общая характеристика векторных прерываний.

- •1. Методы передачи данных: синхронный метод.

- •Билет n 11

- •1. Последовательные интерфейсы передачи данных: spi, i2c, rs232 и др. Сравнительная характеристика.

- •2. Ввод-вывод по опросу. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •1. Формат передачи данных в интерфейсе rs-232.

- •2. Организация прерываний в ibm pc. Общая характеристика.

- •Билет n 13

- •1. Методы передачи данных: асинхронный, асинхронно-синхронный, синхронный. Сравнительная характеристика.

- •2. Реализация прерываний по уровню и по фронту. Сравнительная характеристика.

- •1. Способы передачи информации: параллельный, параллельно-последовательный, последовательный.

- •2. Системы на кристалле. Системные шины, общая характеристика.

- •1. Методы ввода-вывода. Общая характеристика.

- •2. Контроллеры прерываний. Общая характеристика.

- •1. Интерфейсы «общая шина», «изолированная шина». Сравнительная характеристика.

- •2. Организация прерываний в ibm pc.

- •1. Микроконтроллеры с гарвардской архитектурой. Общая характеристика.

- •2. Организация мпс. Шинная структура. Варианты исполнения.

- •1. Сигнальные процессоры. Архитектура, общая характеристика

- •2. Системы на кристалле. Сходство и отличия от классических микропроцессорных систем

- •1. Типовые режимы пересылок данных в шинах систем на кристалле..

- •2. Элементная база современных мпс: типовые элементы, контроллеры и т.Д

- •1. Системы со встроенным вводом-выводом. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Передача информации в мпс: методы стробирования.

- •2. Интерфейсы. Общая характеристика.

- •1. Организация прерываний в микроконтроллерах (на примерах i8080, i8085, z80, 8086).

- •2. Память. Способы классификации, общая характеристика

- •1. Интерфейсы. Общие определения, стандартные интерфейсы.

- •2. Архитектура фон Неймана и ее модификации в системах с прерываниями и пдп.

- •1. Методы разработки и отладки мпс: макетирование, моделирование. Сравнительная характеристика.

- •1. Инструментальные средства отладки микропроцессорных систем: логические, сигнатурные анализаторы и т.Н.

- •2. Интерфейсы. Общие определения, стандартные интерфейсы.

Билет n 7

1. Системы на кристалле. Общая характеристика.

Под приборами класса система-на-кристалле, в общем случае, подразумеваются приборы на едином кристалле которых интегрированы процессор (процессоры, в том числе специализированные), некоторый объем памяти (как правило, очень маленький), ряд периферийных устройств и интерфейсов - т.е. максимум того, что необходимо для решения задач, поставленных перед системой. Как правило, на системе-на-кристалле работает полноценная операционная система.

Типичная SoC содержит:

один или несколько микроконтроллеров, микропроцессоров или ядер цифровой обработки сигналов (DSP),

банк памяти, состоящий из модулей ПЗУ, ОЗУ, ППЗУ или флеш.

источники опорной частоты, например, кварцевые резонаторы и схемы ФАПЧ (фазовой автоподстройки частоты),

таймеры, счетчики, цепи задержки после включения,

стандартные интерфейсы для внешних устройств: USB, FireWire, Ethernet, USART, SPI.

входы и выходы цифро-аналоговых и аналого-цифровых преобразователей.

регуляторы напряжения и стабилизаторы питания.

Блоки могут быть соединены с помощью шины собственной разработки или стандартной конструкции, например AMBA в чипах компании ARM. Если в составе чипа есть контроллер прямого доступа к памяти (ПДП), то с его помощью можно заносить данные с большой скоростью из внешних устройств напрямую в память чипа, минуя процессорное ядро.

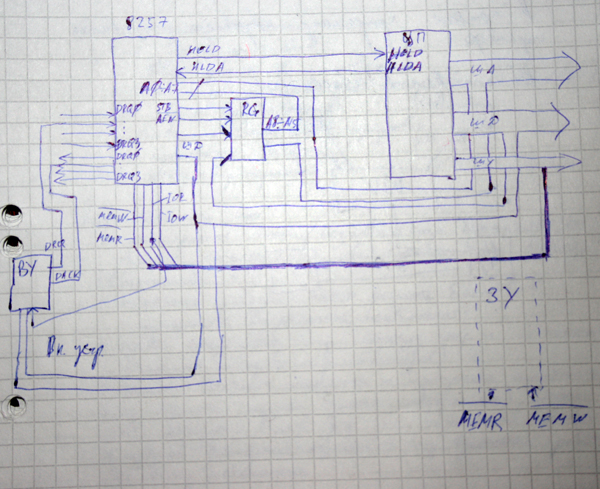

2. Стандартный контроллер пдп. Общая характеристика

Вообще, рассказывалось про контроллер 8257, вот такой.

CLK

CLK

КПДП ЦП

DRQ0 HАLD

DRQ0 HАLD

DACK0 HLDA

DACK0 HLDA

............. 8 8

DRQ3 РГ

DRQ3 РГ

DACK3

STB

RAM

STB

RAM

By AEN

MEMR

MEMR

MEMW

MEMW

IOR

IOW

IOW

MEMW

ШД

ША

ША

ШУ

РГ - защёлка адреса, стандартный контроллер использует мультиплексированные адреса данных. Организовать пересылку данных из внешнего устройства (Ву) в память.

Ву выставляет по линии DRQ0 запрос на прямой доступ к памяти, если приоритет соответствует, то контроллер генерирует сигнал HOLD ЦП. ЦП заканчивает работу текущей программы и выдаёт сигнал по линии HLDA (переводит все свои линии из этого состояния). Контроллер, получив сигнал HLDA, выдаёт разрешение Ву по линии DRQ0 на пересылку данных. И начинается пересылка, которая управляется контроллером. Ву выставляет данные на ШД, а контроллер генерирует сигналы IRQ и MEMR и на ША выставляет адрес записываемых данных. Контроллер инкрементирует (декрементирует) адрес и выставляет следующую пару данных.

Пересылка осуществляется за 1 цикл. Цикл повторяется до тех пор, пока счётчик пересылок в контроллере ПДП не обнулится или цикл может повторяться бесконечно.

Возможна работа ПДП в 2-х режимах:

1) Групповая пересылка байт

2)Одиночная пересылка (после каждой пересылки управление возвращается к ЦП).

Для пересылки данных из памяти в Ву контроллер должен выставить пару MEMR и IQR, всё остальное не изменится . Все взаимодействия осущ-ся по 2 сигналам HALD и HLDA.

БИЛЕТ N 8

1. Методы повышения быстродействия одноуровневых ЗУ. Интерливинг.

Ч астота

< 25 МГц частота > 25 МГц

астота

< 25 МГц частота > 25 МГц

о дноуровневая

многоуровневая

дноуровневая

многоуровневая

линейная интерливинг

страничная КЭШ

с прямым с мадульно - ассоциативным

отображением отображением

Микропроцесор 8080 – частота 2,5 МГц ; быстродействие памяти частота – 10 МГц

При частоте 25 МГц возникает вопрос – согласовать скорость обмена ЦП и памяти.

Линейная организация памяти на динамических сис-мах с повышенным быстродействием.

Станичные и интерливинг. Организации памяти позволяют повысить быстродействие памяти. Переход с динамической на статическую ,но это экономически не выгодно – это метод ещё один для повышения быстродействия.

Интерливинг –память делится на 2 блока (или несколько) и обращение к ним осуществляется последовательно