- •1. Основные принципы работы цп. Машина фон Неймана.

- •2. Аппаратные прерывания pc,обрабатываемые bios. Общая характеристика.

- •1. Ввод-вывод по опросу. Временные диаграммы, особенности программной реализации.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2. Способы организации пдп: «прозрачный» режим.

- •2. Способы организации пдп: метод захват цикла.

- •1. Прямой доступ к памяти. Общая характеристика.

- •2. Особенности разработки по в системах с прерываниями.

- •2. Типовые временные диаграммы обработки аппаратного прерывания на примере любого микропроцессора.

- •1. Сравнительная характеристика методов ввода-вывода.

- •По опросу:

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Организация прерываний в ibm pc. Аппаратная часть. Обработка аппаратных прерываний.

- •Билет n 7

- •2. Стандартный контроллер пдп. Общая характеристика

- •2. Ввод-вывод по прерываниям. Достоинства и недостатки.

- •2. Общая характеристика векторных прерываний.

- •1. Методы передачи данных: синхронный метод.

- •Билет n 11

- •1. Последовательные интерфейсы передачи данных: spi, i2c, rs232 и др. Сравнительная характеристика.

- •2. Ввод-вывод по опросу. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •1. Формат передачи данных в интерфейсе rs-232.

- •2. Организация прерываний в ibm pc. Общая характеристика.

- •Билет n 13

- •1. Методы передачи данных: асинхронный, асинхронно-синхронный, синхронный. Сравнительная характеристика.

- •2. Реализация прерываний по уровню и по фронту. Сравнительная характеристика.

- •1. Способы передачи информации: параллельный, параллельно-последовательный, последовательный.

- •2. Системы на кристалле. Системные шины, общая характеристика.

- •1. Методы ввода-вывода. Общая характеристика.

- •2. Контроллеры прерываний. Общая характеристика.

- •1. Интерфейсы «общая шина», «изолированная шина». Сравнительная характеристика.

- •2. Организация прерываний в ibm pc.

- •1. Микроконтроллеры с гарвардской архитектурой. Общая характеристика.

- •2. Организация мпс. Шинная структура. Варианты исполнения.

- •1. Сигнальные процессоры. Архитектура, общая характеристика

- •2. Системы на кристалле. Сходство и отличия от классических микропроцессорных систем

- •1. Типовые режимы пересылок данных в шинах систем на кристалле..

- •2. Элементная база современных мпс: типовые элементы, контроллеры и т.Д

- •1. Системы со встроенным вводом-выводом. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Передача информации в мпс: методы стробирования.

- •2. Интерфейсы. Общая характеристика.

- •1. Организация прерываний в микроконтроллерах (на примерах i8080, i8085, z80, 8086).

- •2. Память. Способы классификации, общая характеристика

- •1. Интерфейсы. Общие определения, стандартные интерфейсы.

- •2. Архитектура фон Неймана и ее модификации в системах с прерываниями и пдп.

- •1. Методы разработки и отладки мпс: макетирование, моделирование. Сравнительная характеристика.

- •1. Инструментальные средства отладки микропроцессорных систем: логические, сигнатурные анализаторы и т.Н.

- •2. Интерфейсы. Общие определения, стандартные интерфейсы.

2. Память. Способы классификации, общая характеристика

Классификация микросхем памяти :

Делится память на 2 вида :

-Оперативное ЗУ (читать и писать )

-ПЗУ (читать в процессе работы МПС)

ОЗУ:

1.Микросхемы регистровой памяти.

2.Статическая память.

3.Динамическая память

ПЗУ:

1.Массочные (ПЗУМ)

2.ПЛМ – программируемые логические матрицы

3.ППЗУ – программируемая пользователем ЗУ

4.РПЗУ – программируемое ЗУ

а) ультрофиолетовое стирание информации

б) электрическое стирание (Flash память)

Порядки микросхем :

ОЗУ

1) Регистровые (фаил из нескольких регистров) , информационная ёмкось не велика.

Достоинства:

а) быстродействуют

Недостатки :

а) большая потребляемая мощность

2) Статическое ЗУ: по информ-ой ёмкости – высокая.На 1 кристалл возможно до 100 Кбайт. Среднее энергопотребление (бит информации) ; быстродействие высокое по ниже регистров, т.к. они построены почти на обычных триггерах. Применимость: быстродействующая память в системе любого типа, строительство простое.

3) Динамическая память: применимость не высокая,потребляемая мощность (бит) маленькая ,высокое быстродействие и высокая информационная ёмкоть в пересчёте на 1 корпус.

Применимость : в системе где требуется высокий объём памяти . Впростых контроллерах не целесообразно применять динамическую память (требуется регенерация).Эта система надёжна , но не для всех систем (кол- во сбоев).

ПЗУ

ПЗУМ – ЗУ запрограммировано на стадии изготовления (путём наложения масок).Применяются в случае высокой серийности изготавливаемых устр-в.Цикл программирования большой (проходит большое время от программирования до применения.

ПЛМ – используется в качестве запоминающего элемента в схеме управления

ППЗУ – схемы с пережигаемыми перемычками внутри кристалла.

Достоинства:

Маленький цикл программирования , применяют в низкосерийных устройствах ; для програмирования требуется дополнительная аппаратура .эти перемычки могут зарости (срок службы нормальный)

РПЗУ – схемы этой группы являются наиболее важными.

Достоинства :

1. Низкий цикл программирования .

2. Неоднократность процесса программирования.

3. Кол- во циклов программирования в 1. от 10 и выше ; а в 2. неограничено.

4. Высокая информационная ёмкость.

Недостатки :

1. Дополнительная аппаратура для стирания информации для :

а) источник жёсткого излучения

б) специальный источник

Информационная ёмкость достигает несколько Мбайт. Flash память – относится к группе б). Для её репрограмирования не обязательно вытаскивать из памяти,высокая информационная ёмкость,низкая стоимость. Её не относят к ОЗУ из-за скорости записи.

Память : ( к обоим видам и ОЗУ и ПЗУ)

синхронная

асинхронная

В синхронной памяти выдача и приём информации тактируются. В асинхронной памяти приём выдачи информации управления подачи комбинационных сигналов.

Синхронная память быстрее чем асинхронная.

БИЛЕТ N 23

1. Синхронная и асинхронная память. Основные принципы работы.

Память : ( к обоим видам и ОЗУ и ПЗУ)

синхронная

асинхронная

В синхронной памяти выдача и приём информации тактируются. В асинхронной памяти приём выдачи информации управления подачи комбинационных сигналов.

Синхронная память быстрее чем асинхронная.

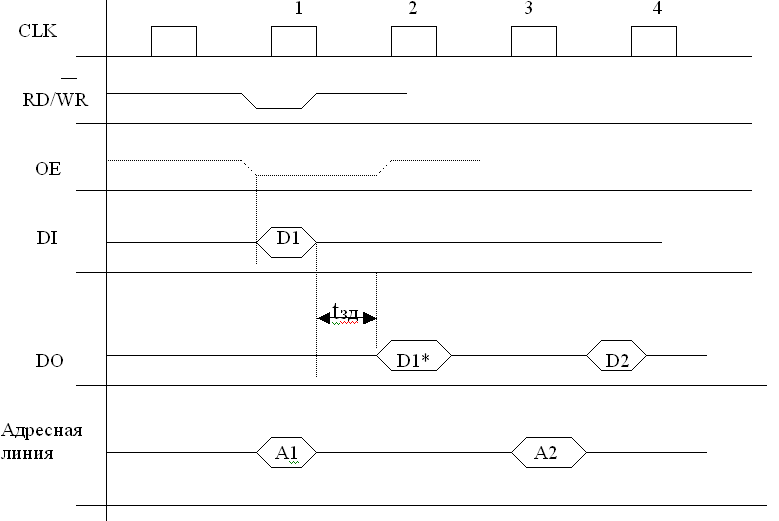

Работа синхронной памяти.Устройство синхронной памяти.

Всё построенно на триггерах ,в обязательном порядке защёлкивается адрес. На память надо подавать тактированные сигналы.

DO : входные данные появляются на вых. с некоторой задержкой tзд и могут быть считаны в следующем такте.

D O и адресная линия : данные появляются на такте где подали адрес , а на следующем такте нужен дополнительный цикл.

Тактирование осуществляется по фронту.

В случае записи и чтении данных по адресу А1 надо 3 цикла :

А1 и D1 записались.

А2

D2

D1* - входные данные копируются на вых. буфер.

2. Архитектура современных микроконтроллеров и микроЭВМ: фон Неймана, гарвардская, DSP. Сравнительная характеристика.

{вставка из рукописи

Фон Нейман

Программа хранится в памяти вместе с данными.

Все обмены с памятью осуществляются только по средствам ЦП.

Последовательное выполнение команд.

Данные могут обрабатываться как программа, а программа как данные.

Гарвард

Интерфейс данных, интерфейс команд.

Достоинства: высокая степень параллелизма в обработке данных.

End}

Всем известный IBM PC-совместимый компьютер представляет собой реализацию так называемой фон-неймановской архитектуры вычислительных машин. Эта архитектура была представлена Джоном фон-Нейманом еще в 1945 году и имеет следующие основные признаки. Машина состоит из блока управления, арифметико-логического устройства (АЛУ), памяти и устройств ввода/вывода. В ней реализуется концепция хранимой программы: программы и данные хранятся в одной и той же памяти.

Рис. 1.1 Архитектура фон-Неймана

Если разделить память на память программ и память данных мы получим Гарвардскую архитектуру.

Рис. 1.2 Гарвардская архитектура

Выполняемые действия определяются блоком управления и АЛУ, которые вместе являются основой центрального процессора. Центральный процессор выбирает и исполняет команды из памяти последовательно, адрес очередной команды задается "счетчиком адреса" в блоке управления. Этот принцип исполнения называется последовательной передачей управления. Данные, с которыми работает программа, могут включать переменные - именованные области памяти, в которых сохраняются значения с целью дальнейшего использования в программе.

DSP отличается от других типов микропроцессоров и микроконтроллеров по следующим пяти основным признакам:

Быстрая арифметика.

DSP - процессор должен осуществлять выполнение за один цикл операций умножения, умножения с аккумуляцией, циклический сдвиг, а также стандартные арифметические и логические операции.

Расширенный динамический объем для операции умножения/аккумуляции.

Операция вычисления суммы некой последовательности значений является фундаментальной для алгоритмов, реализуемых на DSP. Защита от переполнения необходима для избежания потери данных.

Выборка двух операндов за один цикл.

Очевидно, что для большинства операций, выполняемых DSP, необходимы два операнда. Таким образом, для достижения максимального быстродействия процессор должен быть способен производить одновременную выборку двух операндов, что требует также наличия гибкой системы адресации.

Наличие аппаратно реализованных циклических буферов(встроенных и внешних).

Широкий класс алгоритмов, реализуемых на DSP требует использования циклических буферов. Аппаратная поддержка циклического возврата указателя адреса или модульная адресация уменьшает непроизводительные затраты процессорного времени и упрощает реализацию алгоритмов.

Организация циклов и ветвлений без потери в производительности.

Алгоритмы DSP включают очень много повторяющихся операций, которые могут быть реализованы в виде циклов. Возможность организации последовательности выполнения программы кодов в цикле без потери производительности отличают DSP от других процессоров. Аналогично, потеря времени при выполнении операции ветвления по условию также недопустима при цифровой обработке сигналов.

DSP фирмы Motorola

Фирмой Motorola в настоящее время выпускается три семейства Цифровых Процессоров Сигналов. Это серии DSP56100, DSP56000 и DSP96000. Все микросхемы приведенных серий основываются на архитектуре DSP56000 и различаются разрядностью (16, 24, 32 бит соответственно) и некоторыми встроенными устройствами. Таким образом достигается совместимость микросхем всех трех семейств снизу вверх. Все DSP фирмы Motorola построены по идентичной трехшинной Гарвардской архитектуре, описанной ранее, с большим количеством составных частей, портов, контроллеров, банков памяти и шин, работающих параллельно с целью достижения максимального быстродействия.

Передача данных происходит по двунаправленным шинам данных (одной для DSP56100 (XDB) и двум для DSP56000 и DSP96000 (XDB и YDB)), шине данных программ (PDB) и общей шине данных (GDB). Кроме того, у DSP96000 присутствует отдельная шина прямого доступа к памяти (DDB). Передача данных между шинами происходит через внутреннее устройство управления шинами.

Адресация осуществляется по двум однонаправленным шинам: шине адреса данных и шине адреса программ.

Блок манипуляции битами позволяет гибко управлять состоянием любого бита в регистрах и ячейках памяти. Наличие такой возможности является преимуществом по отношению к DSP других пользователей.

Арифметико-логическое устройство (АЛУ) выполняет все арифметические и логические операции и имеет в своем составе входные регистры, аккумуляторы, регистры расширения аккумуляторов (8-битные, допускающие 256 переполнений без потери точности), параллельный одноцикловой блок умножения с сохранением (МАС), а так же сдвиговые регистры.Гибкая система команд позволяет выполнить АЛУ за один цикл команды умножения, умножения с сохранением результата, суммирования, вычитания, сдвига и логические операции. Характерной особенностью DSP фирмы Motorola является возможность сдваивания входных регистров АЛУ и увеличения таким образом разрядности обрабатываемых чисел. Еще одной важной особенностью является наличие операции деления, зачастую отсутствующей у других производителей и заменяемой операцией умножения на обратное число, что приводит к потере точности.

Блок формирования адреса выполняет все вычисления, связанные с определением адресов в памяти. Этот блок работает независимо от остальных блоков процессора. За один цикл могут производиться две операции считывания из памяти или одна операция записи. DSP фирмы Motorola обладают чрезвычайно мощной мощной системой адресации, позволяющей производить практически любые манипуляции с данными за одну команду. Это важная особенность выгодно отличает DSP, выпускаемые фирмой, от аналогов. Адресация по модулю удобна для организации кольцевых буферов без проверки выхода за границу, что позволяет избегать непроизводительных затрат времени. Возможность адресации с инверсией значащих битов облегчает реализацию БПФ.

Блок управления выполнением программ содержит 6 регистров, среди которых Указатель адреса цикла и Счетчика циклов, позволяющие организовать аппаратную поддержку организации циклов в DSP фирмы Motorola, при которой не тратятся дополнительные машинные циклы на проверку условия выхода из цикла и изменения счетчика цикла. В команде организации цикла DO явно указывается количество повторений.

Системный стек представляет из себя отдельную часть из 15 слов ОЗУ, и может хранить информацию о 15 прерываниях, 7 циклах или 15 выходах в подпрограмму. Данные из стека читаются за один цикл уменьшая таким образом непроизводительные затраты времени процессора.

Главной отличительной особенностью DSP фирмы Motorola является наличие у всех микросхем внутрикристального эмулятора, позволяющие производить отладку программ без использования дополнительных аппаратных средств. Таким образом нет необходимости в покупке дорогостоящих отладочных средств. Эмулятор позволяет производить запись/считывание регистров и ячеек памяти, установку точек останова, пошаговое выполнение программ и другие действия посредством подачи команд по 4- проводной шине.

Для снижения потребления энергии в моменты, когда не производится вычисления, предусмотрены два режима с пониженным энергопотреблением : STOP и WAIT.

Для работы совместно с другими процессорами и каналами прямого доступа к памяти предусмотрен встроенный HOST-интерфейс.

Обладая всеми вышеперечисленными свойствами, необходимыми для цифровой обработки сигналов, DSP фирмы Motorola имеют чрезвычайно мощную и гибкую систему команд, позволяющую пользователю удобно и эффективно работать с процессорами.

БИЛЕТ N 24