- •1. Основные принципы работы цп. Машина фон Неймана.

- •2. Аппаратные прерывания pc,обрабатываемые bios. Общая характеристика.

- •1. Ввод-вывод по опросу. Временные диаграммы, особенности программной реализации.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2. Способы организации пдп: «прозрачный» режим.

- •2. Способы организации пдп: метод захват цикла.

- •1. Прямой доступ к памяти. Общая характеристика.

- •2. Особенности разработки по в системах с прерываниями.

- •2. Типовые временные диаграммы обработки аппаратного прерывания на примере любого микропроцессора.

- •1. Сравнительная характеристика методов ввода-вывода.

- •По опросу:

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Организация прерываний в ibm pc. Аппаратная часть. Обработка аппаратных прерываний.

- •Билет n 7

- •2. Стандартный контроллер пдп. Общая характеристика

- •2. Ввод-вывод по прерываниям. Достоинства и недостатки.

- •2. Общая характеристика векторных прерываний.

- •1. Методы передачи данных: синхронный метод.

- •Билет n 11

- •1. Последовательные интерфейсы передачи данных: spi, i2c, rs232 и др. Сравнительная характеристика.

- •2. Ввод-вывод по опросу. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •1. Формат передачи данных в интерфейсе rs-232.

- •2. Организация прерываний в ibm pc. Общая характеристика.

- •Билет n 13

- •1. Методы передачи данных: асинхронный, асинхронно-синхронный, синхронный. Сравнительная характеристика.

- •2. Реализация прерываний по уровню и по фронту. Сравнительная характеристика.

- •1. Способы передачи информации: параллельный, параллельно-последовательный, последовательный.

- •2. Системы на кристалле. Системные шины, общая характеристика.

- •1. Методы ввода-вывода. Общая характеристика.

- •2. Контроллеры прерываний. Общая характеристика.

- •1. Интерфейсы «общая шина», «изолированная шина». Сравнительная характеристика.

- •2. Организация прерываний в ibm pc.

- •1. Микроконтроллеры с гарвардской архитектурой. Общая характеристика.

- •2. Организация мпс. Шинная структура. Варианты исполнения.

- •1. Сигнальные процессоры. Архитектура, общая характеристика

- •2. Системы на кристалле. Сходство и отличия от классических микропроцессорных систем

- •1. Типовые режимы пересылок данных в шинах систем на кристалле..

- •2. Элементная база современных мпс: типовые элементы, контроллеры и т.Д

- •1. Системы со встроенным вводом-выводом. Достоинства и недостатки.

- •В ывод информации Процессор выставляет данные в порт и считывает

- •2) По прерыванию:

- •2. Передача информации в мпс: методы стробирования.

- •2. Интерфейсы. Общая характеристика.

- •1. Организация прерываний в микроконтроллерах (на примерах i8080, i8085, z80, 8086).

- •2. Память. Способы классификации, общая характеристика

- •1. Интерфейсы. Общие определения, стандартные интерфейсы.

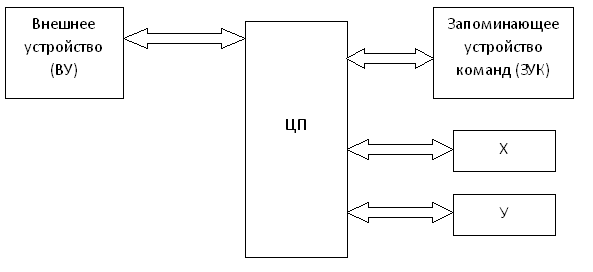

- •2. Архитектура фон Неймана и ее модификации в системах с прерываниями и пдп.

- •1. Методы разработки и отладки мпс: макетирование, моделирование. Сравнительная характеристика.

- •1. Инструментальные средства отладки микропроцессорных систем: логические, сигнатурные анализаторы и т.Н.

- •2. Интерфейсы. Общие определения, стандартные интерфейсы.

1. Сигнальные процессоры. Архитектура, общая характеристика

DSP процессор (или сигнальный процессор) был разработан, исходя из класса задач цифровой обработки сигналов, возможно, в режиме реального времени. Обладает расширенной Гарвардской архитектурой.

Модифицированная гарвардская архитектура

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Еще дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной Гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти.

Расширенная гарвардская архитектура

Часто требуется выбрать три составляющие : два операнда и инструкцию (в алгоритмах цифровой обработки сигналов это наиболее распространенная задача). Для этого существует кэш-память. В ней может храниться инструкция — следовательно, обе шины остаются свободными и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная Гарвардская архитектура

DSP отличается от других типов микропроцессоров и микроконтроллеров по следующим пяти основным признакам:

Быстрая арифметика.

DSP - процессор должен осуществлять выполнение за один цикл операций умножения, умножения с аккумуляцией, циклический сдвиг, а также стандартные арифметические и логические операции.

Расширенный динамический объем для операции умножения/аккумуляции.

Операция вычисления суммы некой последовательности значений является фундаментальной для алгоритмов, реализуемых на DSP. Защита от переполнения необходима для избежания потери данных.

Выборка двух операндов за один цикл.

Очевидно, что для большинства операций, выполняемых DSP, необходимы два операнда. Таким образом, для достижения максимального быстродействия процессор должен быть способен производить одновременную выборку двух операндов, что требует также наличия гибкой системы адресации.

Наличие аппаратно реализованных циклических буферов(встроенных и внешних).

Широкий класс алгоритмов, реализуемых на DSP требует использования циклических буферов. Аппаратная поддержка циклического возврата указателя адреса или модульная адресация уменьшает непроизводительные затраты процессорного времени и упрощает реализацию алгоритмов.

Организация циклов и ветвлений без потери в производительности.

Алгоритмы DSP включают очень много повторяющихся операций, которые могут быть реализованы в виде циклов. Возможность организации последовательности выполнения программы кодов в цикле без потери производительности отличают DSP от других процессоров. Аналогично, потеря времени при выполнении операции ветвления по условию также недопустима при цифровой обработке сигналов.