- •1.1 Електричні кола постійного струму

- •Електричні кола постійного струму

- •1.1.1 Основні визначення і закони

- •1 Джерела електричної енергії (джерела живлення).

- •1.1.2 Розрахунок лінійних кіл постійного струму з одним джерелом живлення.

- •1.2 Електричні кола змінного струму

- •1.2.1 Поняття про змінний струм

- •1.2.2 Основні поняття синусоїдальної функції

- •1.2.3 Зображення синусоїдальної величини

- •Кутова частота і фазові співвідношення

- •Початковий фазовий кут, або початкова фаза.

- •1.2.4 Прості електричні кола змінного струму

- •1.1 Електронно-дірковий перехід

- •1.1.1 Загальні відомості.

- •1.1.2 Утворення переходу.

- •1.1.3 Контакт метал – напівпровідник.

- •1.2.1 Загальні відомості

- •Продовження таблиці 1.2

- •1.2.2 Характеристики, параметри, область застосування

- •1.3.1 Загальні відомості

- •1.3.2 Фізичні явища й принцип дії бт за схемою із загальним емітером

- •1.3.3 Транзистори Шотки

- •1.3.5 Розрахунок режиму спокою підсилювального каскаду на біполярному транзисторі

- •1.4.1 Загальні відомості

- •1.4.2 Фізичні явища та принцип дії пт

- •1.4.2.1 Польові транзистори з керуючим переходом

- •1.4.2.2 Польові транзистори з ізольованим затвором

- •1.4.3 Лізмон-транзистори

- •1.4.4 Мнон - транзистори

- •3.1 Загальна характеристика імпульсних сигналів і пристроїв

- •3.2 Ключовий режим роботи транзисторів

- •3.3.1 Загальні відомості

- •3.3.2 Логічні елементи в інтегральному виконанні

- •3.3.2.1 Діодно-транзисторні логічні елементи

- •3.3.2.2 Транзисторно логіка -транзисторна

- •3.3.2.3 Логічні елементи на мон-транзисторах

- •3.3.2.4 Логічні елементи на мен-транзисторах

- •3.3.2.5 Інтегральна інжекційна логіка

- •3.3.2.6 Логічні елементи емітерно-зв'язкової логіки

- •3.4.1 Загальні відомості

- •Продовження таблиці 3.3

- •3.4.2 Характерні явища для тригерів

- •Лекція 9 3.5 Компаратори і тригери шмітта, генератори імпульсів

- •3.5.1 Загальні відомості

- •3.5.2 Мультивібратори

- •3.5.3 Одновібратори

- •До пункту 3.5.2

- •3.6 Інтегруючі і диференціюючи rc-ланцюги

- •3.6.1 Інтегруючий rc-ланцюг

- •3.6.2 Диференціюючий rc-ланцюг

- •4.1 Загальні відомості

- •4.2 Однофазний однопівперіодний випрямляч

- •4.3 Однофазний двухпівперіодний випрямляч із нульовим виводом

- •4.4 Однофазний мостовий випрямляч

- •4.5 Випрямлячі - помножувачі напруги

- •4.6 Згладжуючи фільтри

- •4.7.1 Параметричні стабілізатори напруги

- •4.7.2 Компенсаційні стабілізатори напруги

- •Контрольні питання

3.3.2.6 Логічні елементи емітерно-зв'язкової логіки

Схемотехніка елементів ЕЗЛ заснована на використанні диференціального підсилювача в режимі перемикання струму. Елементи ЕЗЛ з'явилися в 1967 р. і в цей час є самими швидкодіючими серед напівпровідникових елементів на основі кремнію. Затримки поширення сигналів в елементах ЕЗЛ зменшилися до субнаносекундного діапазону (приблизно 1 нс).

Зверхшвидкодія елементів ЕЗЛ досягається за рахунок використання ненасиченого режиму роботи транзисторів, вихідних емітерних повторювачів, малих амплітуд логічних сигналів (близько 0,8 В). У логічних елементах ЕЗЛ є парафазний вихід, що дозволяє одночасно одержувати пряме й інверсне значення реалізованої функції. Це дає помітне зниження загальної кількості мікросхем в апаратурі.

Особливостями схемотехніки ЕЗЛ і її характеристик є:

можливість об'єднання виходів декількох елементів для утворення нових функцій;

можливість роботи на низькоомне навантаження завдяки наявності емітерних повторювачів;

невелике значення роботи перемикання й незалежність споживаної потужності від частоти перемикання;

висока стабільність динамічних параметрів при зміні температури й напруги живлення;

використання негативного джерела живлення й заземлення колекторних ланцюгів, що зменшує залежність вихідних сигналів від перешкод у шинах живлення.

До недоліків елементів ЕЗЛ відносять складність схем, значне споживання потужності й труднощі узгодження з мікросхемами ТТЛ і ТТЛШ.

Промисловість випускає ряд серій ЕЗЛ: 100, 137, 138, 187, 223, 229, 700, 500 і ДО1500.

Схема типового логічного елемента ЕЗЛ серії 500 показана на рис. 3.12.

Рисунок 3.12 - Схема типового логічного елемента ЕЗЛ серії 500

Схема ЕЗЛ включає:

перемикач струму (логічні транзистори VT1, VT2, опорний транзистор VT3, резистори R1;R2;R3);

джерело опорного зсуву (транзистор VT4, діоди VD1,VD2 резистори R5,R6);

• вигхдні

емітерні повторювачі (транзистори

VT5,VT6).

Напруга

на відкритому переході база-емітер

кремнієвого транзистора є

постійним параметром

![]() В.

При описі роботи елемента беруть виразу

для негативної

логіки: значення 0 відображається високим

(з урахуванням знака)

рівнем напруги

В.

При описі роботи елемента беруть виразу

для негативної

логіки: значення 0 відображається високим

(з урахуванням знака)

рівнем напруги

![]() В;

значення балка. 1 відображається низьким

рівнем

напруги

В;

значення балка. 1 відображається низьким

рівнем

напруги

![]() В.

Амплітуда (перепад) логічного сигналу

В.

Амплітуда (перепад) логічного сигналу

![]() В.

Опорна напруга перемикача струму

розташовується симетрично

щодо рівнів двійкових сигналів і

визначається як їх середнє:

В.

Опорна напруга перемикача струму

розташовується симетрично

щодо рівнів двійкових сигналів і

визначається як їх середнє:

![]() В.

В.

Якщо хоча б на один із входів подана напруга В, то даний транзистор відкривається, на нього перемикається струм IE, що створює на резисторі R1 спадання напруги мінус 0,9 У. При цьому опорний транзистор закритий і на резисторі R2 спадання напруги дорівнює мінус 0,1 У.

Якщо

на всіх входах подані рівні UL

=

-1,7 У, то транзистори VТ1

і

VT2

закриваються,

а транзистор VT3

відкривається

й на нього перемикається струм

IE.

У цьому випадку

падіння напруги на резисторі R1

дорівнює

мінус 0,1 В, а на резисторі R2

мінус

0,9 В. При цьому на колекторах лівого й

правого плеча рівні напруги не

відповідають

прийнятому значенню двійкового сигналу.

Емітерні повторювачі на транзисторах

VT5

і

VT6

зміщають

рівні сигналів, що надходять на їхню

бази з лівого

й правого плеча перемикача, на

В

у сторону негативних сигналів:

![]() ;

;

![]() .

.

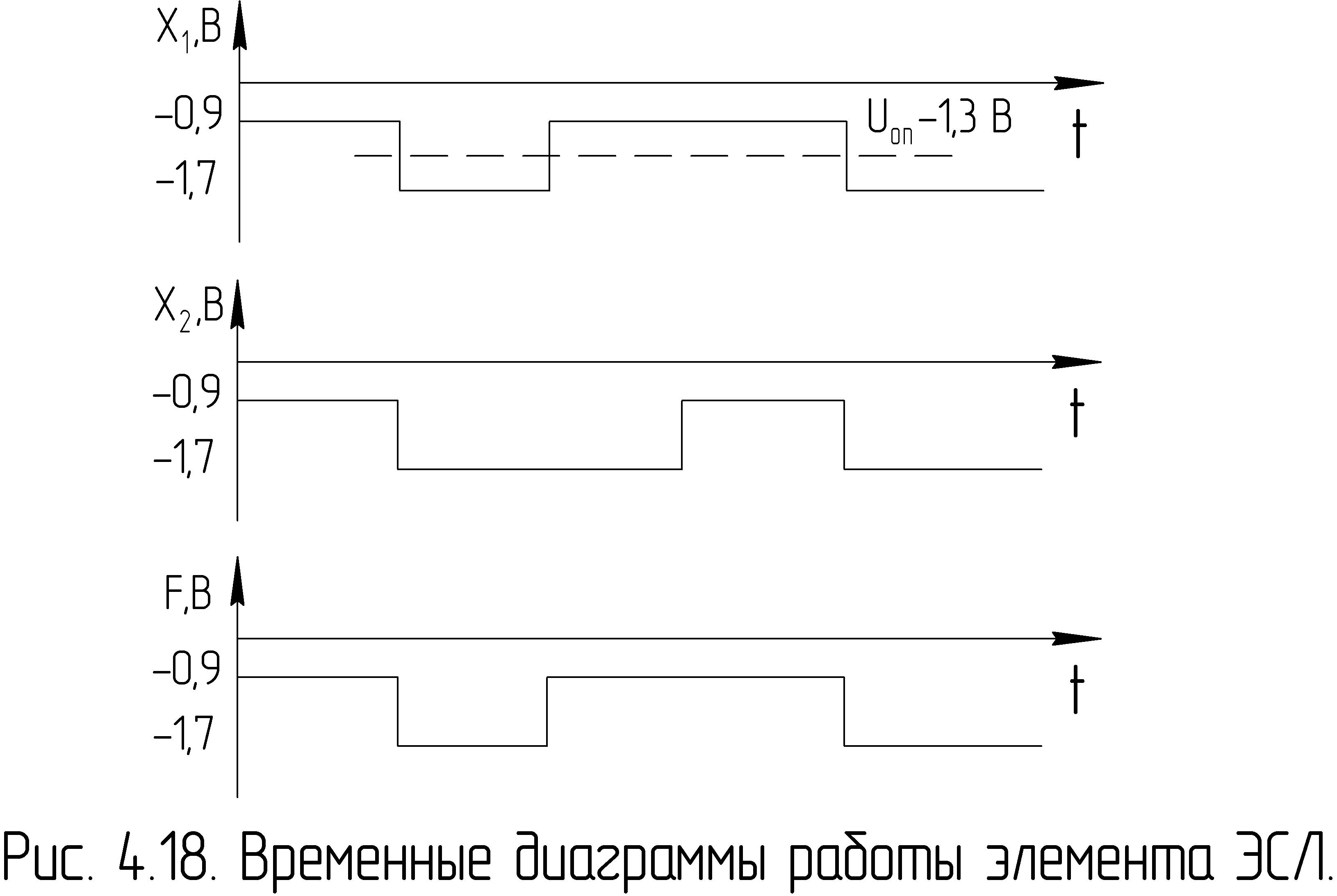

Внаслідок цього рівні вхідних і вихідних сигналів відповідають прийнятому стандарту. Тимчасові діаграми роботи елемента ЕЗЛ показані на рис. 3.13

.

Рисунок 3.13 - Часові діаграми роботи елемента ЕЗЛ

Як треба з часових діаграм, вхідні й вихідні логічні сигнали змінюються на ±0,4 В щодо опорної напруги.

У негативній логіці елемент ЕЗЛ реалізує на прямому виході F функцію І а на інверсному виході Y— функцію НІ-І, що записується як АБО-НІ. У позитивній логіці елемент ЕЗЛ реалізує функцію АБО-НІ /АБО.

Контрольні питання

До пункту 3.3.1

Визначення логічного елемента.

Логічне додавання, логічне множення, логічна інверсія.

Умовне графічне позначення, таблиця істинності й тимчасових діаграм елемента «АБО»,«І», «НІ»,« І-НІ»,« АБО-НІ».

До пунктів 3.3.2.1-3.3.2.6

Комбінована схема «І-НІ», «АБО-НІ» та ін.

Логічні елементи в інтегральному виконанні.

ДТЛ та ТТЛ (схема та принцип роботи).

МОП ТЛ , КМОП ТЛ, МЕП ТЛ (схема та принцип роботи).

Інтегрально-інжекторна логіка.

Логічні елементи емітерно-зв’язної логіки.

Лекція 8 3.4 Тригери

Загальні відомості

Характерні явища для тригерів

R-S – тригери

D – тригери

Т-тригер

J-K-тригер