- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

Глава 2. Устройства эвм.

2.1 Определение и назначение триггеров, их классификация.

Триггером называют логическую схему с положительной обратной связью, способную формировать 2 устойчивых состояния на своих выходах Q и не Q, изменения которых происходит под действием входных сигналов. Предназначен в основном для хранения одного бита информации, т.е. логических «0»или «1». Схема триггера обеспечивает запись, считывание, хранение, стирание и индикации двоичной информации. На основе триггеров строятся типовые функциональные узлы ЭВМ – регистры, счетчики, накапливающие сумматоры, микропрограммные автоматы. Состояние триггера, определяемое по входам: прямом – Q и инверсном не Q, устанавливается сигналами на его входе. При положительном кодирование (высокий уровень на входе Q – “1”) под воздействием сигнала на его информационном входе S(set) называют установкой, а при подаче сигнала на вход R (reset) (высокий уровень на входе не Q) называют сбросом.

Основные информационные входы триггеров:

S – разделительный вход установки (Q=”1”)

R – разделительный вход сброса (Q=”0”)

Y – вход установки универсального триггера (Q=”1”)

K – вход сброса универсального триггера (Q=”0”)

T – счетный вход триггера

D – информационный вход для подключения триггера в состояние, соответствующее логическому уровню сигнала его входа

С – управляющий или синхронизирующий вход

V – вход для блокирования триггера с целью длительного хранения информации

Классифицируются триггеры по разным признакам:

По типу используемых входов:

RS – триггеры, D – триггер, T, JK, VD, VT.

По способу записи информации:

Асинхронные и синхронные.

По моменту реакции на входной сигнал:

Статические и динамические.

По числу тактов синхронизации:

Однотактовые, двухтактовые, трехтактовые.

По числу ступеней:

Одно- или двухступенчатые.

Могут быть и другие признаки.

Различают четыре типа входов триггера.

Прямой статический – реагирует на уровень сигнала

Инверсный статический – реагирует на уровень сигнала

Прямой динамический – реагирует только на перепад входного сигнала от «0» к «1»

Инверсный динамический – реагирует только на перепад входного сигнала от «1» к «0»

3 и 4 в другие моменты не реагируют на сигнал.

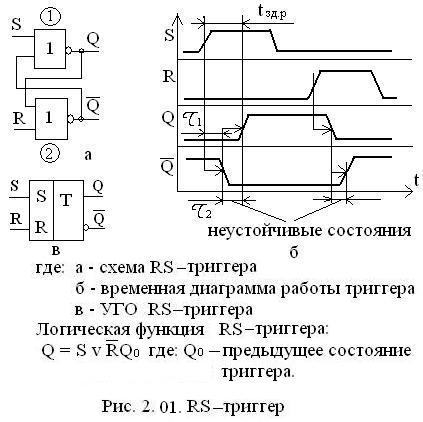

2.2 RS – триггеры.

RS – триггер асинхронный на элементах И-НЕ.

Схема триггера, его УГО и временная диаграмма работы триггера приведены на рис. 2.1.

Логическая функция RS – триггера на элементах ИЛИ-НЕ: Q=Sv¬RQ0 = ¬(Rv¬(SvQ0)), где Q0 предыдущее состояние.

Работа RS – триггера.

Пока сигналы на входах S и R - неактивны (равны 0) триггер находится в одном из устойчивых состояний, состояние его называется режимом хранения. Допустим триггер установлен: Q=1, ¬Q=0. Q=1 поступая на вход элемента 1 поддерживает на его выходе Q=1. В таком состоянии триггер может находится сколь угодно долго. В силу симметрии триггер будет устойчив и при Q=0 а ¬Q=1, т.е. будет устойчивым и в сброшенном состоянии.

Основные свойства RS – триггера.

(На временной диаграмме рис 2.1.б.)

Исходное состояние нулевое (Q=0,¬Q=1).

- Сигналы поступают поочередно: S=1 потом R=1.

- После окончания S=1 триггера запоминает его и хранит до появления R=1. Это его важнейшее свойство.

- Для возврата триггера в исходное состояние надо подать сигнал R=1.

Оба элемента ИЛИ-НЕ 1 и 2 переключаются поочередно, последовательно – сначала 2, а потом 1 при установки; при сбросе наоборот.

Существуют промежутки во время переключения элементов когда на обоих выходах уровни одинаковы – и состояние триггера неустойчивое: если в это время снять сигнал, вызывающий переключение, триггер может вернуться в первоначальное состояние, что опасно для последних схем – они могут принять ложный сигнал.

Время задержки на переключение триггера составляет tзд.р.=ῐ1+ῐ2

Где ῐ1 – время переключения элемента 1, ῐ2 – время переключения элемента 2. tзд.р – определяет необходимую длительность входного сигнала (оно берется обычно не менее (2÷3) ῐ для надежного переключения триггера).

При подаче на входы RS – триггера одновременно двух сигналов R=1 и S=1 на входах Q и ¬Q появляются «0». Теперь если эти сигналы одновременно убрать, то оба элемента начнут переключаться в единичное состояние, стремясь оставить партнера в «0». Какой из них выиграет, зависит от их:

- коэффициента усиления элемента ИЛИ-НЕ

- скорости переключения или переходных процессов

- от ряда случайных факторов.

Т.е. исход борьбы будет неопределенным, поэтому комбинации на входе S=1, R=1 являются запретными.

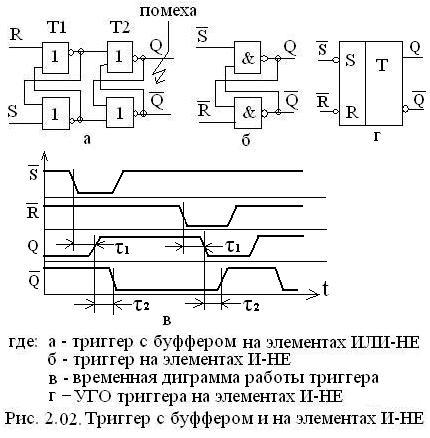

У триггера есть обратные связи и его выходы одновременно являются его входами. Следовательно, если на его выходе появляется короткая помеха (например, от нагрузки) то она может подействовать на другой вход и привести к переключению триггера (запоминанию помехи). Поэтому иногда триггеры делают двухступенчатыми (см. рис. 2.2. а). На входах Т2 постоянно действуют сигналы из выходов Т1 и помеха не сможет подействовать на него.

RS – триггеры на элементах И-НЕ.

(рис .2.2.б)(его УГО на рис.2.2.г.)

RS – триггер на элементах И-НЕ будет двойственным по отношению к триггеру на элементах ИЛИ-НЕ. Все процессы в нем будут происходить наоборот, это видно из временной диаграммы (рис.2.2.в). RS – неудобны для хранения информации, так как для записи новой информации триггер требует двух сигналов для записи.

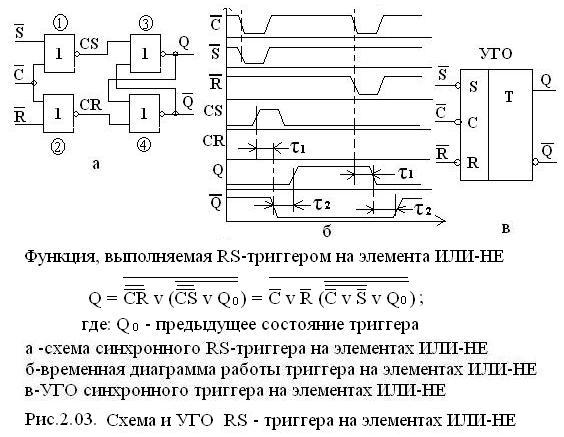

2.3. Синхронные RS – триггеры.

Синхронные RS – триггеры на элементах ИЛИ-НЕ.

Схема, временная диаграмма работы такого триггера и его УГО приведены на рис.2.3.а,б и в.

Элементы ИЛИ-НЕ 1 и 2 составляют схему с инверсными входами, который является сам по себе асинхронный триггер – фиксатор. Из временной диаграммы (рис.2.3.б) видно, что при ¬C=0 и ¬S=0 на входе элемента 2 устанавливает логическая «1» (т.е. CS=1) и триггер (элементы 3 и 4 переключаются в состояние «1» (CR=1) и триггер переключается в состояние «0». Комбинация ¬C=¬S=¬R=0 – запрещена, т.к. на выходе триггера будет неопределенность.

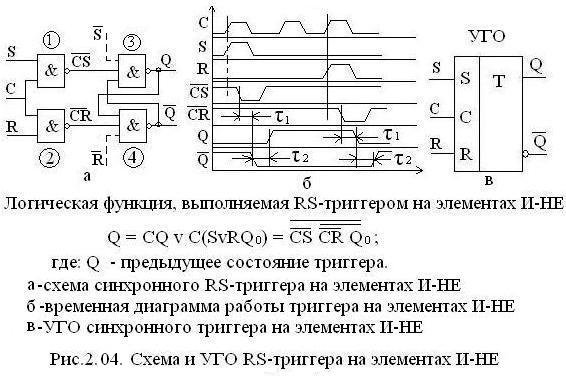

Синхронные RS – триггеры на элементах И-НЕ (схема, временная диаграмма работы и УГО триггера приведены на рис.2.4.а,б и в).

Здесь аналогично триггеру на элементах ИЛИ-НЕ, схема установлена на элементах 1 и 2 с прямыми входами S,R и С. При значении S=0, на выходе элементах 3 и 4 переключается в «1». При значении R=0 на выходе устанавливается ¬(CS)=1 и триггер переключается в состояние «0». В заключении заметим, что минимальная задержка распространения сигнала (время срабатывания триггера) в синхронных RS – триггерах составляет 3ῐ: одна ῐ в элементах 1 и2, а 2ῐ - в самом RS – триггере. Синхронные RS – триггеры могут быть снабжены приоритетными входами ¬S и ¬R (входы асинхронные)(см. рис.2.4.а). Схема синхронного RS – триггера (при С=1) функционирует как асинхронный RS – триггера.

2.4. D – триггеры. DV – триггеры.

Схема D – триггера приведена на рис.2.5.а. (пунктирные линии пока игнорируем).

D – триггер имеет один информационный вход, информация с которого записывается только по сигналу С, т.е. может быть только синхронным. С – сигнал играет роль команды записать. Временная диаграмма работы триггера показана на рис.2.5.б. Из диаграммы видно, что изменения информационного сигнала на D – входе при С=0 не влияют на выход Q (моменты t1, t2 и t7). Т.е. триггер запирается по входу С и находится в режиме хранения.

Фронт сигнала С ( момент t3) переключает триггер в состояние соответствующее значению сигнала на входе D.

В этом смысле D – триггер задерживает прохождение входного сигнала D до поступления сигнала С: от сюда его название D – триггер (delay – задержка). Другие названия триггера: прозрачная защелка, прозрачный фиксатор, синхронный фиксатор.

При С=1 триггер прозрачен: любое изменение D – сигнала меняет состояние Q – выхода в соответствии с D – входом (моменты t4 и t5). По срезу С – сигнала (t6) D – триггер фиксирует на выходе Q то значение сигнала, которое было на D – входе перед этим моментом. Следующее изменение Q - выхода возможно только по фронту С – сигнала (t8).

При С=1-const – свойство запоминания триггер теряет и становится просто усилителем мощности в тракте передачи. Способы табличного описания работы триггера 1 и 0 или символами уровней H и L приведены на рис.2.5.е. где Х – безразлично.

Иногда в D – триггер вводятся дополнительные входы (см. рис.2.5 пунктирные линии). ¬R – вход для сброса триггера в «0» при С=0.

При С=1 если при этом и D=1 RS – триггер (элементы 3 и 4) подача ¬R=0 запрещена, т.к. в противном случает он окажется под воздействием нулевых входов ¬S и ¬R, что приведет к неопределенности выходов.

V – вход. При его наличии триггер называется DV – триггером, который будет работать как D – триггер только при подаче одновременно двух сигналов: D – сигнала и V – сигнала, т.е. их конъюнкции. Условные обозначения D – триггера и DV - триггера приведены на рис. б и в).

Динамические характеристики D – триггера.

(рассмотрим диаграмму на рис.2.5.д)

Временная диаграмма (рис . д) построена с учетом состояний неопределенности. Переходный процесс характеризуется по двум трактам:

tзд.р.CQ – от входа С до выхода Q при D – const.

tзд.р.DQ – от входа D до выхода Q при С=1.

Выводы:

Для фиксации состояния D – входа на выходе Q без сбоев, переходный процесс в схеме, вызванный срезом С – сигнала не должен накладываться на переходный процесс, вызванный переключением D – входа, т.е. нужны промежутки: tПД – время подготовки, tВД – время выдержки. Обычно они равны tПД =(1÷2)ῐ и tВД=(0÷ῐ). Где ῐ - длительность фронтов при переключении сигнала.

Существует минимальная длительность С – сигнала, которая обеспечивает отсутствие сбоев из-за наложения переходных процессов вызванных передним и задним фронтами.

Подобные выводы справедливы для большинства цифровых схем. Серийно выпускаемые D – триггеры K155TM5, TM7, K561 TM3 и др. (обычно по 4 триггера в микросхемах).

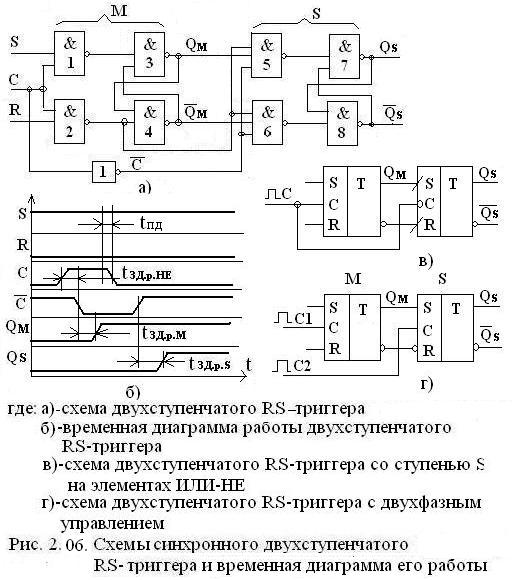

2.5. Синхронные двухступенчатые RS – триггеры.

Синхронные двухступенчатые RS – триггеры строятся по способу последовательного соединения двух синхронных RS – триггеров, называемых M – ступень (Master – хозяин, основная) и S – ступень (Slave – раб, вспомогательная) управляемые общим сигналом С, обеспечивают совмещение 2-х процессов: одновременной записи новой информации и считывание ранее записанной. Схемы таких триггеров можно строить разными способами.

Работа схемы (рис.2.06.а)

Во время действия сигнала С первая ступень М может принимать информацию по входу S, а может со второй ступени S, в это время можно считывать информацию, ранее записанную. По окончании сигнала С первой блокируется ступень М (сигнал С=0), а вторую ступень под действием сигнала через инвертор ¬C, информация переписывается из входов первой ступени М. Таким образом обе ступени управляются сигналом С, первая напрямую, а вторая через инвертор.

Легко заметить, что в приведенной схеме RS – триггера есть два пути распространения сигнала С: один путь через элементы 1,2,3,4, а другой через инвертор, после чего они встречаются в элементах 5 и 6. Следовательно в ней возможны гонки (см. 1.9)

Для борьбы с ними применяются несколько способов построения двухступенчатых триггеров, так называемых противогоночных.

Первый способ построения противогоночной схемы RS – триггера приведен на рис.2.6.в. Здесь ступень М выполнена на элементах И-НЕ, а ступень S – на элементах ИЛИ-НЕ (дуальном варианте, см 1.6), следовательно ступени будут срабатывать на противоположных уровнях сигнала С, тогда влияние задержки в цепи сигнала будет практически равна 0.

Второй способ (рис.2.06.г) – управление разнесенными во времени сигналами С1 и С2.

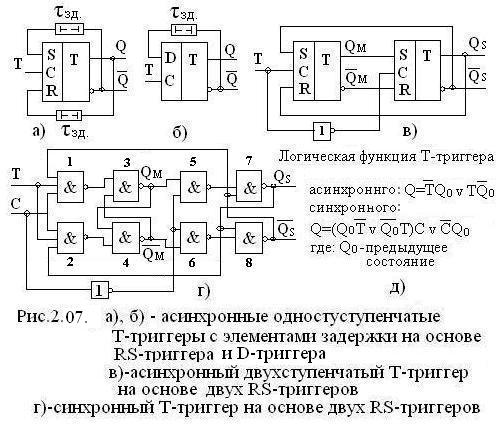

2.6. Двухступенчатые Т – триггеры.

Т – триггером называется триггер с одним информационным входом Т, состояние которого меняется на противоположное после прихода каждого счетного импульса на Т – вход. Поэтому Т – триггер еще называют счетным.

Функциональные схемы одноступенчатых асинхронных Т – триггеров на основе RS – триггера и D – триггера приведена на рис.2.7.а и б соответственно.

Переключение триггера обеспечивается совместным действием сигнала на входе Т и сигналов с выходов Q, ¬Q и у D – триггера - ¬Q по обратным связям. Однако такие схемы Т – триггера не могут обеспечить надежное его функционирование.

Объясняется это тем, что элемент памяти (сам RS – триггер) должен одновременно выполнять две взаимоисключающие функции: быть источником и приемником информации, что при отсутствии достаточных задержек самого элемента памяти невозможно: изменение выхода немедленно скажется на входе. Даже при наличии задержек в обратной связи не гарантирует надежной работы триггера. Во время действия сигнала Т сигналы с входов Q и ¬Q не должны изменяться на входе триггера, т.е. должно выполняться условие ῐЗД=ТСИГН, что выдержать довольно сложно в силу например, изменения температуры, старения элементов, которые повлияют на величину ῐЗД.

Эту проблему счетного одноступенчатого триггера решает схема с использованием двухступенчатого RS – триггера (рис.2.7.г). В этом синхронном Т – триггере информация при поступлении С.Т запоминается в первой ступени (М), а после их окончания переписывается во вторую ступень (S).

Допустим триггер сброшен: QS=0, ¬QS=1. При поступлении сигналов С.Т на входе элемента 1 окажется три единицы и информация запишется в ступень М, а по окончании С.Т перепишется в ступень S, следовательно на выходе окажется QS=1, ¬QS=0. При следующем приходе С.Т сработает элемент 2 и триггер вернется в исходное состояние QS=0, ¬QS=1. Триггер осуществил сложение двух сигналов по mod 2. Далее процесс повторяется. Говорят: Т - триггер «кувыркается». У Т – триггера может быть дополнительные входы например для сигнала С.Т.V .

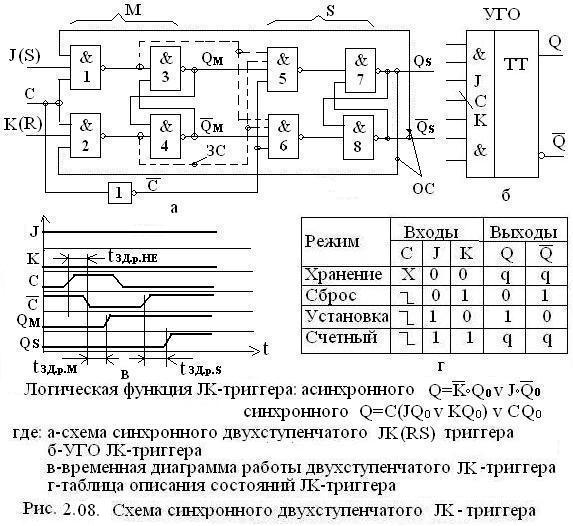

2.7. JK – триггеры.

JK – триггер, построенный на основе двухступенчатого RS – триггера, является универсальным триггером, поскольку на его основе могут быть построены другие, ранее рассмотренные: D – триггер, DV – триггер, Т – триггер.

Схема JK – триггера приведена на рис.2.8.а, получена из двухступенчатого RS – триггера за счет охвата обратными связями выхода Q со входом (R) K – входом и выхода ¬QS со входом (S) J. Временна диаграмма работы триггера приведена на рис.2.8.в, а таблица переходов (описания) состояний на рис.2.8.г.

В таблице значок означает срез сигнала С на входе, по которому срабатывает триггер, q – состояние на выходах триггера перед поступлением сигнала С, а Х – безразличное значение (т.е. сигнал не действует на триггер). На рис.2.8.в приведена временная диаграмма работы триггера, а на рис.2.8.б – УГО JK – триггера.

Работа JK – триггера.

(без учета пунктирных линий (ЗС – запрещенные связи)). Очевидно, что всегда на вход одного из элементов 3И-НЕ (1 или 2) поступает с выхода ¬QS или Q либо «0» либо «1». Допустим, что исходное состояние JK – триггера: QS=0, ¬QS=1 и QМ=0, ¬QМ=1.

Следовательно на вход элемента 1 по обратной связи поступает «1», а на вход элемента 2 – «0». При подаче сигнала С=1 и сигнала J=1 первая ступень по фронту С перебросится: т.е. на ее выходах окажется QМ=1, ¬QМ=0, а по срезу сигнала С (через инвертор) перебросится и ступень S – станет QS=1, ¬QS=0. Аналогично все происходит при противоположном исходном состоянии триггера и при подаче С=1 и К=1. На выходе окажется QS=0, ¬QS=1.

Основные свойства JK – триггера.

Ни при С=0 ни при С=1 триггер для выходных сигналов не прозрачен, хотя каждая ступень в отдельности при С=1 прозрачна.

При J=К=0 – режим хранения. С – сигнал не может действовать.

При J=1 К=0 С – сигнал открывает только элемент 1 при условии, что на выходах триггера: QS=0 ¬QS=1. Если до этого было QS=1 ¬QS=0 то триггер останется без изменений, то есть в этом состоянии J – вход выполняет функцию S – входа RS – триггера. В силу симметричности схемы, аналоговый вывод будет и при исходном состоянии J=0 К=1. Тогда К – вход выполняет функцию R – входа RS – триггера.

При J=1 и K=1 JK – триггер существенно отличается от RS – триггера, для которого такая комбинация входов запрещена. В этом случае JK – триггер при любом предыдущем состоянии, по срезу сигнала С меняет состояние своих выводов на противоположное. Такой режим работы JK – триггера называется ступенчатым или режимом Т – триггера. (режим кувыркания).

Замечание: Некоторые JK – триггеры могут иметь двойные и даже тройные конъюнктивные входы (см. рис. 2.8.б), что на его свойства не влияет. В этом случае на входы J и K должны подаваться только конъюнкции сигналов J и K с другими сигналами. На УГО JK – триггера буквы ТТ – означают наличие двух ступеней.

Некоторые особенности двухступенчатых триггеров.

У JK – триггера, так же как и у RS – триггера есть параллельные пути распространения сигнала: через М – ступень и через инвертор, после чего они встречаются в элементах 5 и 6, следовательно есть возможность возникновения гонок.

В JK – триггере иногда применяется способ построения противогоночной схемы с использованием запрещающих обратных связей (ЗС) (рис. 2.8.а, пунктирные линии), помимо рассмотренных способов в 2.5 (построение S – ступени в дуальном варианте, использования разнесенных во времени сигналов управления ступенями С1 и С2). В принципе применение запрещающих обратных связей возможно и в синхронных двухступенчатых RS – триггерах. В случае наличия ЗС между элементами 1 – 5 и 2 – 6 возможность проникновения ложного сигнала из М – ступени в S – ступень блокируется нулевым уровнем того из конъюнкторов 1 или 2, который срабатывает в данный момент под воздействием сигнала J или K.

Однако в схемах с ЗС возможно явление, которое называют «проскок фронта» и которое может привести к сбоям. Пусть JK – триггер находится в режиме хранения, то есть J=K=0. Тогда при С=1 на том из входов J или K, конъюнктор которого 1 или 2 открыт по цепи обратной связи с выходов S – ступени, поступит короткая единичная помеха (в том числе по цепи ЗС на S – ступень) например, от источника сигналов на вход J или K при не закончившихся переходных процессов на его выходе, вызовет переключение М – ступени, которое сразу же пройдет в S – ступень, переключит ее по своему фронту ни дожидаясь переключения С – сигнала. Если же при С=1 на J или K поступит нулевая помеха, произойдет аналогичное переключения S – ступени но уже по отрицательному фронту помехи, не дожидаясь переключения С – сигнала. В обоих случаях произойдет сбой в работе, триггер зафиксирует логический сигнал.

В двухступенчатых синхронных триггерах без ЗС возможно явление, такое как «захват единицы». Если задержка в инверторе превысит задержку М – ступени, то при поступлении С –сигнала новое состояние М – ступени успеет проскочить в S – ступень, прежде чем инвертор закроет элементы 5 и 6 и следовательно выход триггера QS изменится не по фронту С – сигнала а по его срезу, что может вызвать сбой в узле, который принимает сигналы из триггера. Метод борьбы с таким явлением заключается в том, что при изготовлении подобных триггеров по интегральной технологии достигается нормирование задержек в М – ступени и инверторе. Для достижения гарантированной их разницы, чтобы инвертор реагировал на фронт С - сигнала раньше, а на его срез позже чем М – ступень. Достигается это за счет регулирования порогов срабатывания в элементах.

В рассматриваемых триггерах также возможны гонки по входу (1.8, рис 1.18).

Из рассмотренных случаев сбоя в работе двухступенчатых триггеров можно сделать вывод: для надежной их работы надо соблюдать условие о нем говорилось в 2.4.

а) Необходимо обеспечить окончание всех переходных процессов в логических схемах, формирующих сигналы для входов J и K (S или R) до начала действия С – сигнала, то есть обеспечить промежуток времени, который называется tВД (время выдержки) и tПД (время подготовки).

б) В течении действия С – сигнала уровни на входах J и K (S или R) не должны изменяться.

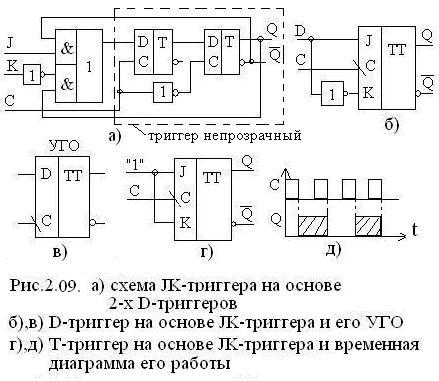

2.8 Применение JK – триггеров для построения D – и T – триггеров.

Схемы приведены на рис 2.09.

На рис 2.09.а приведена схема JK – триггера, построенная на основе D – триггеров. Важным свойством такого триггера является отсутствие явления «захват 1» и «проскок фронта». Этот триггер непроницаем для помех, поэтому состояния входов J и K можно менять как при С=0 так и при С=1. Необходимо только соблюдать интервалы tПД перед самым срезом и tВД сразу после среза С – сигнала. Часто такие триггеры называют триггерами, переключаемые перепадом. Их применение выгодно в цепях с помехами, поскольку помеха здесь опасна в течении короткого интервала подготовки плюс интервала выдержки. Все остальное время триггер на помехи не реагирует. Примером такого триггера является JK – триггер – К561ТВ1. Временными характеристиками триггера являются: tЗД.Р.CQ, tВД, tПД, минимально допустимая длительность С – сигнала, максимально допустимая длина фронта С – сигнала.

На рис 2.09.б приведена схема D – триггера на основе JK – триггера и его УГО на рис 2.9.в. В отличии от рассмотренного D – триггера (защелка) в 2.4, рассматриваемый D – триггер будет непрозрачен по D – входу. Явления проскока фронта и захвата 1 также отсутствует, поскольку триггер переключается перепадом С – сигнала. Однако если такой триггер построить на основе JK – триггера с запрещающими связями, то у него при С=1 будет проскок фронта по D – входу.

На рис 2.09.г приведена схема синхронного Т – триггера на основе JK – триггера. В этом случае на входы J и K подана постоянная логическая единица. Такой триггер используется только в счетном режиме, его вход С называют счетным. Временная его работы приведена на рис 2.9.д. Триггер делит частоту входных сигналов пополам, то есть триггер суммирует сигналы по mod 2.

2.9 Шестиэлементный триггер с динамическим управлением.

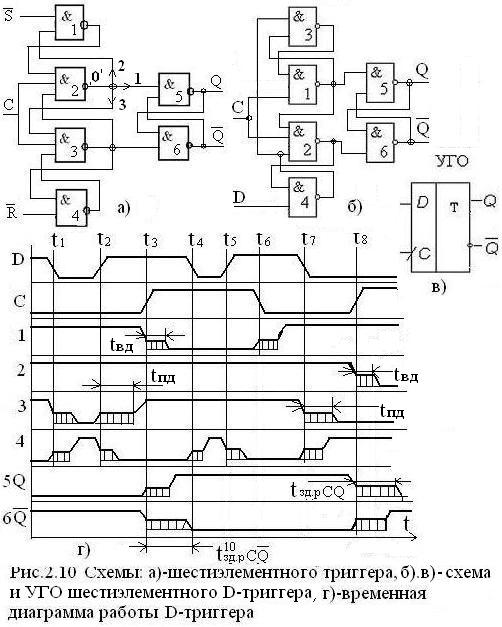

Схемы шестиэлементного триггера и на его основе D – триггера приведены на рис 2.10.

Шестиэлементный триггер еще называют схемой трех триггеров, триггер с самоблокировкой, триггер Вебба.

Работа шестиэлементного триггера.

Триггер принимает информацию по ¬S и ¬R входам только в момент перепада С – сигнала, точнее в окрестностях этого момента. Часть схемы (элементы 2,3,5 и 6) без перекрестных связей между элементами 2 и 3 представляет собой синхронный RS – триггер с управлением уровнем С – сигнала, чувствительный к сигналам ¬S и ¬R при С=1.

Чтобы триггер воспринимал сигналы ¬S и ¬R только во время фронта С – сигнала, надо блокировать цепи подачи информационных сигналов сразу после перехода С – сигнала из «0» в «1» и сохранять эту блокировку до возвращения сигнала С к нулевому уровню. Нулевое значение С – сигнала устанавливает единицу на выходах элементов 2 и 3, что приводит выходной триггер (элементы 5 и 6) в режим хранения. При С=0 выходы элементов 1,4 дают инверсии входных информационных сигналов, передавая эти значения S и R на входы элементов 2 и 3 соответственно.

При поступлении С=1, если при этом S=R=0, сохранится режим хранения. Если же появится единичный информационный сигнал, например S=1 R=0 то на входе элемента 2 все входы окажутся единичными а его выход нулевым. Этот «0» сразу закроет элемент 1, перебросит триггер (элементы 5 и 6) в «1» и предотвратит возможное воздействие на выходной триггер по второму входу (элемент 6). Аналогичные действия будут и при R=1 S=0.

Работа шестиэлементного D – триггера (с динамическим управлением).

Рис 2.10 б и г.

В триггер входными конъюнкторами являются 1 и 2, выходными – 5 и 6. На временной диаграмме заштрихованные области обозначают зоны неопределенности состояний элементов (переходные процессы), учитывающие и времена задержек.

При С=0 элементы 1 и 2 закрыты и триггер (элементы 5 и 6) не реагируют на изменения D – входа (моменты t1, t2 и t7) как и положено D – триггеру. Триггер находится в режиме хранения. По фронту С – сигнала (моменты t3 и t8) в зависимости от уровня на D – входе открывается один из конъюнкторов (1 или 2) и переключает триггер (5-6) (если подтверждает состояние, если оно совпадает с требуемым). Элементы 3 и 4, управляемые D – входом, своими уровнями на выходе подготавливают один из конъюнкторов (1 или 2) для того, чтобы он открылся очередным С – сигналом (моменты t1, t2 и t7).

Система связей между элементами 1,2,3,4 обеспечивает следующее:

Переключившись по фронту С – сигнала в «0», элемент 1 по связи – его выход – вход элемента 2, блокирует вход элемента 2, не давая ему открыться даже если несколько позже, уже при С=1 вход D переключится в «0» (момент t4). В свою очередь элемент 2 сработав по фронту С – сигнала ( момент t8) по цепочке элементов 2-4-3-1, блокирует элемент 1, даже в случает переключения D – входа в «1». Таким образом можно сделать вывод, что при С=1 триггер непроницаем по D – входу ни для каких его изменений. То есть шестиэлементный D – триггер переключается только перепадом С – сигнала от «0» к «1». Схема такого триггера – противогоночная и допускает для своих элементов любые сочетания задержек, поскольку все его элементы переключаются последовательно, параллельные пути распространения сигнала отсутствуют. tЗД.Р.CQ равна сумме задержек элементов 2,5,6. tПД – время подготовки, в течении которого D – вход не должен изменяться, определяется временем неопределенного состояния на входах конъюнкторов 1 и 2. Самое длинное время срабатывания при этом определяется временем срабатывания элементов 4 и 3 ( на временной диаграмме tПД). tВД – время выдержки, в течении которого после фронта сигнала С D – вход не должен меняться, определяется временем в течении которого элемент 1 должен заблокировать (переключить) вход элемента 2 или наоборот.

Нарушение непроницаемости D – триггера возможно на срезе С – сигнала, если срез сильно затянуть, а порог элемента 2 существенно выше порога элемента 1 (это гонки по С – входу). Так если триггер находится в «0» и если во время среза С – сигнала от уровня элемента 2 до порога элемента 1 состояние D – входа переключится из «0» в «1», то элемент 1 выдаст ложный нулевой сигнал, который переключит выходной триггер в «1».

Пример выпускаемого подобного триггера К155ТМ2. Поскольку шестиэлементный D – триггер прозрачен по D – входу, то на его основе строят Т – и JK – триггеры.

Работа шестиэлементного Т – триггера.

Рис 2.11 а и б.

Входы J и K(штриховые линии) – игнорируем. По фронту С(Т) – сигнала схема работает как Т – триггер. Необходимым условием устойчивого переключения является следующее:

Время задержки распространения tЗД.Р.C¬Q по тракту вход С(Т) – выход ¬Q должно быть больше времени выдержки tВД по входу D. Входные сигналы Т каждый раз меняющие состояние выхода элементов 5 и 6 проходят через элементы 1 и 2 поочередно: четные через один, нечетные через другой. На выходе каждого частота делится пополам. Состояние выходов элементов 5 и 6 меняется по фронту входного сигнала Т, а выход элемента 3 – по его срезу, что иногда используется в пересчетных схемах.

Замечание.

При использовании входов J и K (рис 2.11.а) схема работает как JK – триггер. Единственный его недостаток – он пропускает проскок фронта как и двухступенчатый JK – триггер, поэтому уровни на его входах J и K не должны изменяться пока С=1. Это обстоятельство не позволяет при передаче информации с одного триггера на другой использовать выходы Q и ¬Q. В таком триггере используется выход ¬Q1, который срабатывает по срезу С – сигнала, т.е. по окончанию входного сигнала. На базе шестиэлементного триггера логично еще построить JK – триггер, который будет иметь свойство непроницаемости т.е. переключаться по фронту если на входе непрозрачного D – триггера поставить элемент 2И-ИЛИ.

Более подробно о двухступенчатых и шестиэлементных триггера см. в книге Потемкина стр. 177-196.