- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

Глава 7. Умножители, драйверы, синхронизаторы.

7.1. Умножители.

Вслед за успехами технологии изготовления ИС происходит переход от выполнения арифметических операций в ЭВМ с использованием последовательных комбинационных устройств (например сумматоров) к специализированным ИС, выполняющих операции аппаратными способами, что значительно увеличивает быстродействие ЭВМ.

Логика построения таких блоков чаще всего связана с традиционными алгоритмами выполнения операций.

Построение например блоков умножения (умножителей) двоичных кодов на основе суммирования частичных произведений, получаемых с применением конъюнкторов.

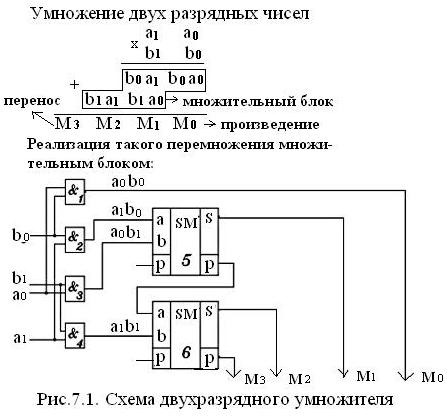

Рис 7.1.

Здесь частичные произведения А0*B0, В0*А1 и т.д. формируются конъюнкторами 1 – 4 (причем одновременно), а код результата сумматорами 5 и 6 (последовательно). Полученная схема умножения носит название матричного множительного блока (ММБ).

Используя такой подход логично синтезировать умножитель произвольной разрядности.

Пример: Пусть имеем 2 числа разрядности m*n.

Аm=am-1a2юююф0 и Bn=bn-1bn-2…b0

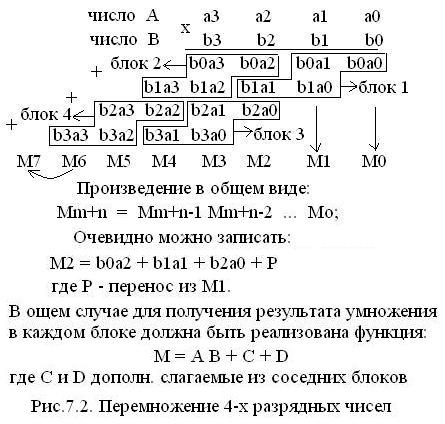

Перемножим два 4-х – разрядных числа А и В. Рис 7.2.

Из рассмотренного процесса перемножения в столбце М2 чисел А и В логично сделать вывод: каждый из выделенных блоков должен: получить частичное произведение b1a1 (в блоке 1) и дополнительно прибавить, кроме переноса Р, полученного от сложения b0a1 в самом блоке, частичные произведения b0a2 и b2a0, полученных в соседних блоках 2 и 3, т.е. каждый блок должен реализовывать показанное на рис 7.2. соотношение М=А*В + С*D.

Следовательно в рассмотренную схему умножения двух 2-х – разрядных чисел (рис 7.1.) надо добавить еще два сумматора для прибавления к А*В слагаемых С*D.

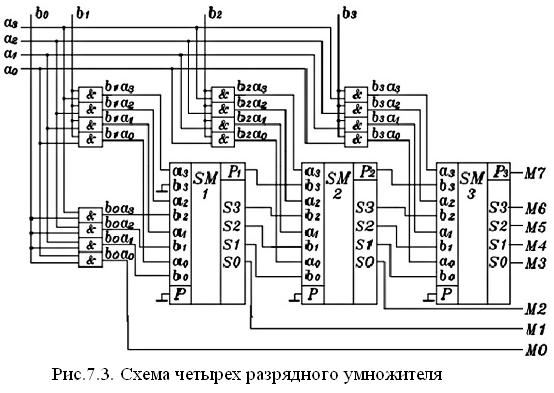

С учетом сказанного на рис 7.3 приведена схема 4-х – разрядного умножителя.

Работа схемы очевидна и соответствует алгоритму умножения 4-х –разрядных чисел А и В.

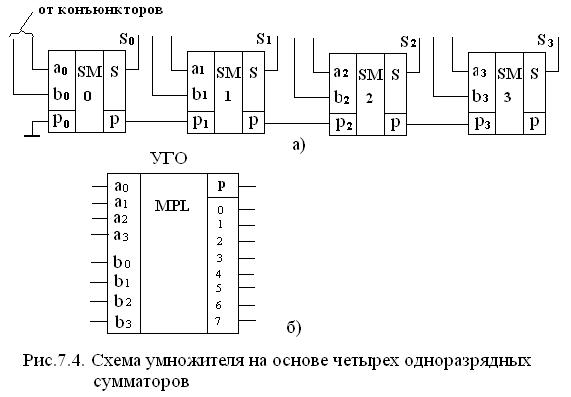

4-х – разрядные сумматоры SM1, SM2 и SM3, используемые в схеме умножения на рис 7.3., построены на основе одноразрядных сумматоров, соединенных по схеме приведенной на рис 7.4.

Вывод: для построения множительно – суммирующего блока для n – разрядных чисел требуется: n2 – конъюнкторов и n2 одноразрядных сумматоров.

Максимальная длительность умножения tумн есть сумма задержек сигналов в конъюнкторах для определения произведения bj*ai и задержки в цепочке передачи сигналов в матрице одноразрядных сумматоров т.е.

tумн = tk + (m+n-1)tsm.

где tk – задержка конъюнктора,

tsm – задержка одноразрядного сумматора SM.

УГО умножителя показано на рис 7.4. б

Где Е – сигнал стробирования

MPL – Multiplir – матричный умножитель. Примеры выпускаемых умножителей:

Серия 1802: 8х8(17нс), 12х12 разр. Минск 32х32 (250нс) Hitachi 16х16 (5нс).

7.2. Последовательные умножители.

В последовательных умножителях вычисляются n+m – разрядное произведение:

P=An+Bm

Где An = an-1…a1a0 – множимое разрядности n.

Bm = bm-1…b1b0 – множитель разрядности m.

Множимое Аn записывается в параллельном коде во внутренний регистр памяти умножителя, а разряды множителя Bm подаются на умножитель последовательно начиная с младшего разряда по мере умножения.

Из традиционного алгоритма умножения чисел известно, что умножитель должен иметь накапливающий сумматор, состоящий из n – разрядного комбинационного двоичного сумматора и сдвигающего регистра, который используется и в качестве аккумулятора старших разрядов суммы частичных произведений.

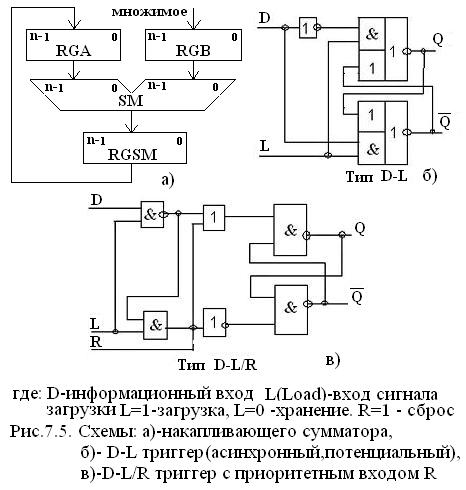

Схема накапливающего сумматора приведена на рис 7.5.а, работа которого очевидна.

В множителе применяются два типа триггеров (рис 7.5. б и в):

D-L – триггер и D-L/R – триггер с приоритетным входом сброса R. Их работа ясна из схемы.

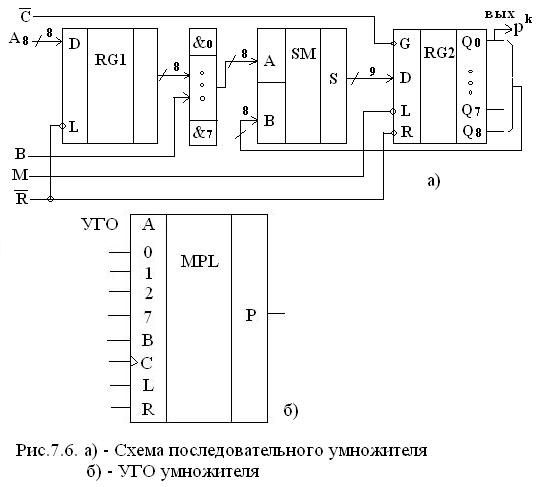

Схема умножителя и его УГО приведены на рис 7.6. а и б соответственно.

8 – разрядный регистр RG1 памяти умножителя для числа A8 построен на D-L – триггерах (асинхронные, потенциальные), а 9 – разрядный сдвигающий регистр RG2 на D-L/R триггерах. Выход сумматора SM 9 – разрядный с учетом переноса.

Загрузка множимого A8 в RG1 производится параллельно по сигналу ¬R=0, который одновременно сбрасывает RG2 в «0». Умножение числа А8 на один разряд bk множителя В8 (его разряды поступают последовательно друг за другом) (к- номер разряда и такта) производится набором из 8 логических элементов И:

aiхbk = ai*bk

Пока поступают разряды bk множителя, сдвигающий регистр RG2 работает в режиме синхронной (параллельной) загрузки (L=0). Эффект сдвига это время при передачи суммы из RG2 в сумматор SM обеспечивается подачей разрядов RG2 с весом на 1 больше на разряды сумматора, то есть разряды RG2 QКН с весом 2К+1 подаются на входы сумматора SM – подаются bk с весом 2к.

Умножение выполняется за m+n тактов с выдачей произведения Р в последовательном коде с выхода Q0 сдвигающего регистра RG2. Первые m – разрядов произведения выдаются при загрузке RG2 за счет эффекта сдвига при вышеупомянутой передаче из RG2 в SM, а остальные n – разрядов после подачи сигнала L=1, который переключает RG2 в режим сдвига под действием тактового сигнала ¬С.

Множитель Вm может иметь произвольную разрядность. УГО умножителя показано на рис 7.6. б. Пример серийно выпускаемого умножителя К555И9 (8 х 1 бит).

7.3. Драйверы. Шинные приемопередатчики.

Усилитель тока с большой нагрузочной способностью принято называть буферами или драйверами.

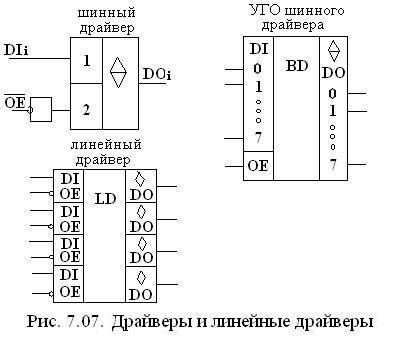

Многоразрядные драйверы с Z – состояниями выходов используются для подключения устройств к системной (внутренней) шине микро процессорных систем с помощью монтажное ИЛИ, к общим шинам других устройств. Также драйверы часто называются формирователями или шинными драйверами (Bus Driver).

Схема данного многоразрядного драйвера и УГО приведены на рис 7.7. Если каждый разряд многоразрядного драйвера управляется отдельным сигналом то его принято называть линейным драйвером.

УГО – линейного драйвера приведено на рис 7.7. Он содержит 4 линейных формирователя. Шинные формирователи могут быть с открытым коллектором.

Шинные приемопередатчики.

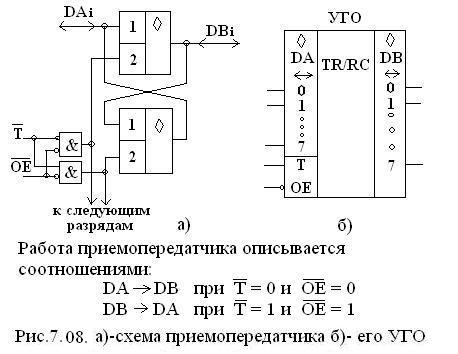

Рассмотренные драйверы передают сигналы в одном направлении. Однако часто возникает необходимость передавать данные по одной шине в двух направлениях (противоположных), например, от процессора к памяти или внешнему устройству и наоборот.

Для этого применяются двунаправленные драйверы, которые называются приемопередатчиками (transceiver) схема и УГО которых приведены на рис 7.8 а и б.

В остальных случаях выходы приемопередатчика находятся в Z – состоянии.