- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

§ 5.3 Сумматоры с параллельным переносом.

Сумматоры с параллельным переносом не имеют последовательного распространения сигнала переноса от разряда к разряду. Во всех разрядах перенос формируется специальными схемами, на входы которых одновременно поступают все переменные, необходимые для его выработки.

Суть построения сумматора с параллельным переносом поясняет его структурная схема, показанная на рис. 5.5.

Основной задачей в таком сумматоре является построение специальной схемы для формирования сигнала переноса для каждого разряда.

Определим функции, реализуемые специальными схемами для разрядов.

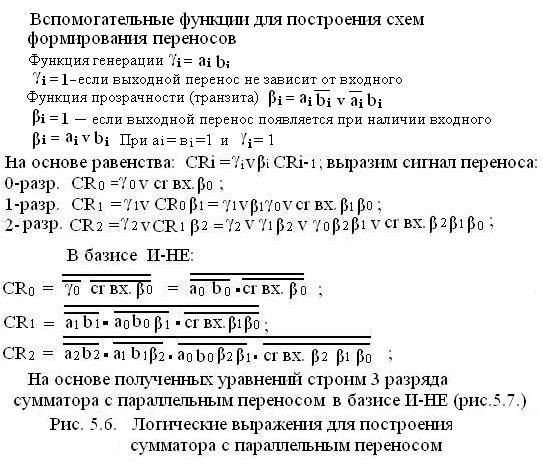

Введем две вспомогательные функции (для удобства) рис. 5.6.

Функция генерации: γi=ai·bi, которая принимает единичное значение, если перенос на выходе данного разряда появляется независимо от наличия или отсутствия входного переноса.

Функция прозрачности (транзита): βi=ai

˅ ai

,

которая принимает единичное зачение

на выходе данного разряда появляется

только при наличии входного переноса.

Но поскольку при ai=bi=1

перенос формируется при γi=1,

то функцию транзита можно представить:

βi=ai

˅bi.

Теперь выражение для сигналов можно

представить так – CRi=γi˅βi·CRi-1,

на основе которого получены равенства

для разрядов 0,1 и 2.

˅ ai

,

которая принимает единичное зачение

на выходе данного разряда появляется

только при наличии входного переноса.

Но поскольку при ai=bi=1

перенос формируется при γi=1,

то функцию транзита можно представить:

βi=ai

˅bi.

Теперь выражение для сигналов можно

представить так – CRi=γi˅βi·CRi-1,

на основе которого получены равенства

для разрядов 0,1 и 2.

На рис. 5.6 – представлены все неравенства.

На основе этих уравнений построены специальные схемы для сумматора трехразрядного для формирования переносов (рис. 5.7).

Из схемы видно, что время задержки суммирования складывается из:

- времени формирования функции βi раном τ,

- времени CR равном 3τ

- времени задержки одноразрядного сумматора SM равном (4÷5)τ.

Итого суммарная задержка составляет (7÷8)τ, причем она не зависит от числа разрядов. Фактически это не совсем точно, поскольку с ростом числа разрядов увеличивается нагрузка на элементы. Например, на элемент, формирующий β0 – подключен 1 элемент, β1 – подключаются 2 элемента и т. д. А это приводит к росту задержки τ этих элементов, и начиная с определенного числа разрядов, сумматор начинает терять преимущества параллельного переноса по быстродействию.

Практически используются:

-сумматоры до четырех разрядов – последовательный перенос,

-сумматоры до восьми разрядов – параллельный перенос.

§ 5.4 Двоично-десятичные сумматоры.

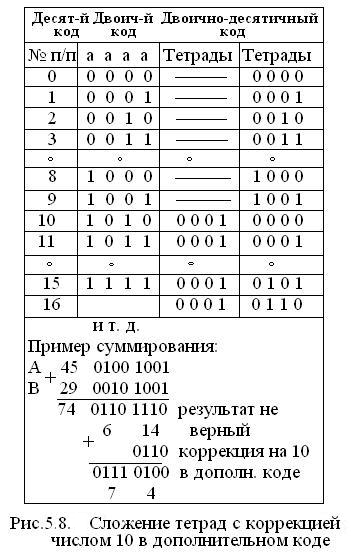

Для операций над десятичными числами каждая цифра от 0 до 9 представляется двоичной тетрадой, после чего операции над десятичными числами производятся над тетрадами, как над двоичными числами.

Такое представление десятичных чисел получило название двоично-десятичного кода, отнесенного к классу взвешенных кодов. Очевидно, что для представления десяти цифр необходим четырехразрядный двоичный код. На рис. 5.8 представлена таблица соответствия десятичных цифр двоичным тетрадам.

И з

таблицы видно, что тетрады двоичного

кода, начиная с 1010 и до 1111 не используются

(будем считать их запрещенными),

следовательно при суммировании тетрад

с 0000 до 1001 в итоге могут появиться

запрещенные тетрады, что приведет к

неверному результату и подстверждает

пример суммирования, рассмотрены на

рис. 5.8, из которого видно, что тетрада

1110 запрещенная, оказалась с избытком

10 и потребовала коррекции – вычитания

этого избытка 10, представленного в доп.

коде и переноса 1 в следующую (старшую)

тетраду. На основе этих рассуждений

можно построить сумматор для подобных

сложений одноразрядных десятичных

чисел, представленных двоичными

тетрадами.

з

таблицы видно, что тетрады двоичного

кода, начиная с 1010 и до 1111 не используются

(будем считать их запрещенными),

следовательно при суммировании тетрад

с 0000 до 1001 в итоге могут появиться

запрещенные тетрады, что приведет к

неверному результату и подстверждает

пример суммирования, рассмотрены на

рис. 5.8, из которого видно, что тетрада

1110 запрещенная, оказалась с избытком

10 и потребовала коррекции – вычитания

этого избытка 10, представленного в доп.

коде и переноса 1 в следующую (старшую)

тетраду. На основе этих рассуждений

можно построить сумматор для подобных

сложений одноразрядных десятичных

чисел, представленных двоичными

тетрадами.

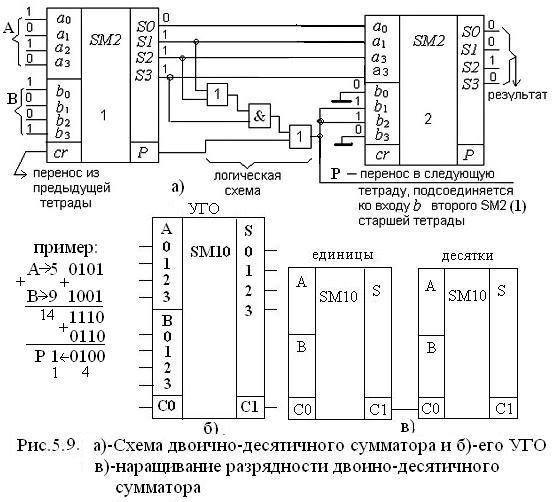

Такой сумматор. его УГО и наращивание его разрядности приведены на рис.5.9 а), б), и в) соответственно.

Из схемы видно, что если в результате суммирования получается разрешенная тетрада, то а выходе логической схемы формируются нули, и следовательно, разряды «bi» SM2 (2) влияния на разряды аi, поэтому результат суммирования в SM2(1) формируется без изменения.

Если же образуется запрещенная тетрада, логическая схема на ее основе сформирует коррекционную комбинацию и результат в SM2 (2) будет скорректирован.

При вычитании двоично-десятичных чисел используются преобразователи числа В (вычитаемого) в дополнение до 9 (получение обратного кода значения вычитаемой тетрады) на основе соотношения |W=9-B|, где W – дополнение, В – вычитаемое.

Фукционирование тактов преобразоветелей описывается таблицей дополнений, представленной на рис. 5.10 а), а соединение преобразователя с десятичным сумматором на рис. б).

где: SUB-(Substract) – вычитание ,SUB=0 – сложение, SUB=1 – вычитание, Z – сигнал установки нулевого значения на выходе блока. Z=0 – на выходах «0».