- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

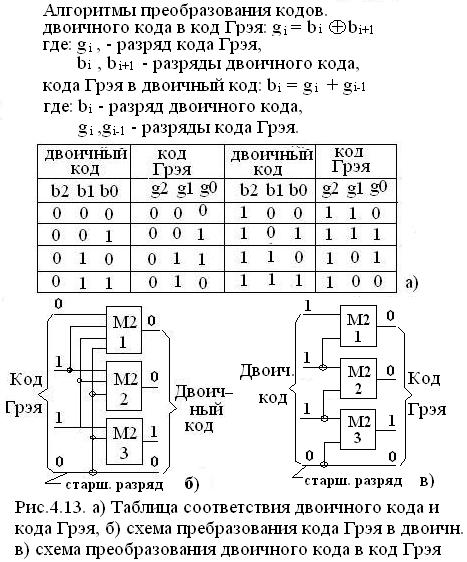

§4.7 Код Грэя

Недостатком синхронных счетчиков является возможность переключения всех разрядов одновременно, например, при переходе от комбинации все единицы к комбинации все нули, что может привести к провалу в питании и, следовательно, к сбою.

Свободным от этого недостатка является Код Грея. На рис.4.13 приведена в качестве примера а) – таблица соответствия двоичного кода коду Грэя и алгоритмы преобразования двоичного кода в код Грэя и наоборот. На рисунках б) и в) соответствующие схемы, осуществляющие эти преобразования.

Основные свойства кода Грэя.

1.При переходе от одного числа к другому соседнему изменение в комбинациях происходит только в одном разряде.

2.Код еще называют рефлексивным или отраженным. В разряде можно поставить зеркало и получить в нем отражение верхней части кода, которое будет продолжением таблицы.

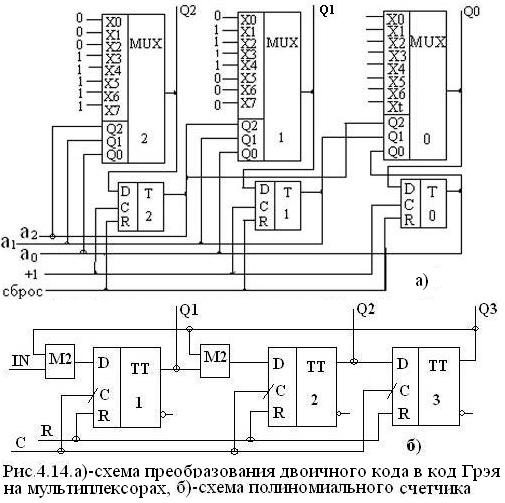

Недостаток кода: результат на выходе требует перекодирования, поскольку счет неестественный. На рис.4.14 а) приведена схема преобразования двоичного кода в код Грэя, построенная на мультиплексорах.

§4.8 Полиномиальные счетчики.

Это сдвигающие регистры с линейными обратными связями, генераторы псевдослучайных последовательностей. Используются в устройствах тестового диагностирования цифровых устройств, решения задач методом Монте-Карло, моделировании систем с учетом разброса их параметров и в ряде других случаев.

Название «полиномиальные» связано с понятием линейных комбинационных функций. На рис.4.14 б) приведена схема полиномиального счетчика. При нулевых состояниях всех триггеров и при IN=0 счетчик не реагирует на С-сигналы. При подаче IN=1 (причем только одной) по очередному сигналу С счетчик переходит в состояние 100, и далее при IN=0 в каждый такт схема меняет состояние по некоторому закону. Схема входит в цикл и будет работать в нем, пока по входу гашения R все триггеры будут сброшены в «0».

Длина и вид генерируемой последовательности зависят от числа триггеров в счетчике и от того, между какими разрядами заведены О.С. и включены сумматоры по mod2.

В заключение, полиномиальные узлы а базе сдвигающих регистров и сумматоров по mod2 способны реализовать ряд операций над полиномами (многочленами), имеющими двоичные коэффициенты при степенях переменной Х (пример – циклические коды).

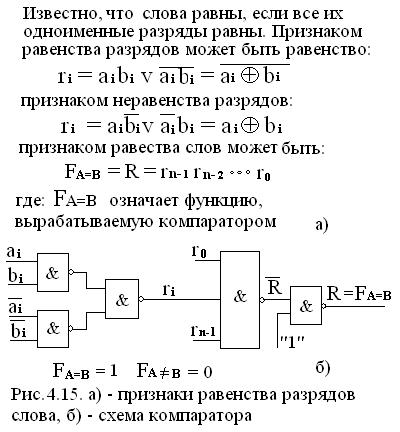

§ 4.9 Компараторы.

Компаратор – это узел для сравнения двух чисел. Простейший компаратор сравнивает 2 числа (слова) А и В и выдает однобитовый сигнал: при равенстве А=В –>1, при неравенстве – 0.

Полный компаратор сравнивает А и В и определяет соотношения: A=B, A>B и A<B.

При построении компаратора преодолевается основная трудность: определение указанных соотношений – функций.

Сравнение двух чисел происходит на основе поразрядных операций над одноименными разрядами обоих чисел.

Признаки равенства разрядов сформулированы и приведены на рис.4.15 а).

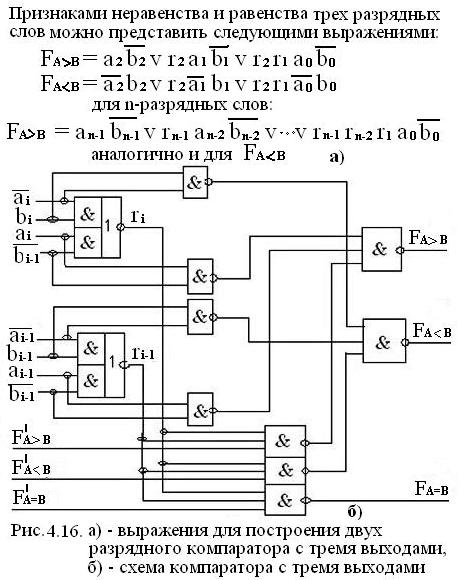

На основе полученных выражений для функции FAi=Bi построена схема сравнения одноименных разрядов чисел А и В, которая приведена на рис. 4.15 б). Функции FA>B и FA<B можно получить на основе следующих рассуждений:

при a2=1 и b2=0 – слово А>B

при a2=0 и b2=1 – слово А>В.

При а2=b2 результат сравнения будет неизвестным, поэтому нужен анализ более младших разрядов. Следовательно, для трехразрядных слов можно записать выражения для FA>B и FA<B, которые приведены на рис. 4.16 а).

В соответствии с полученными выражениями для FA=B,FA>B и FA<B построен компаратор для сравнения двух двухразрядных чисел А и В, схема которого приведена на рис.4.16 б).

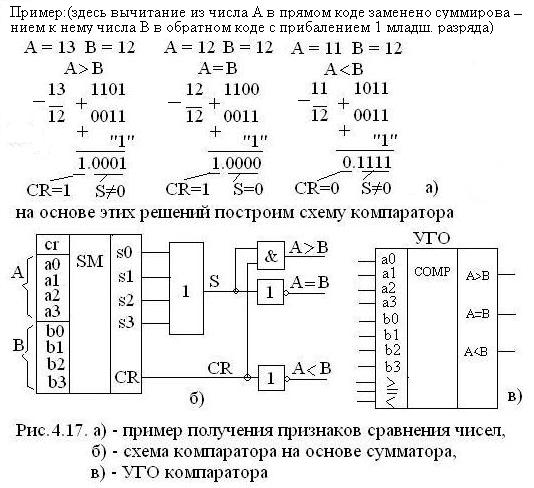

Компаратор можно построить и на основе сумматора, используя операцию вычитания чисел А-В, для чего число В достаточно представить в обратном коде, после чего сложить и прибавить 1 младшего разряда.

По результатам такого суммирования можно выделить признаки, по которым определить соотношения:

А>B –>CR=1 S≠0 на основе этих признаков построена схема

A=B –> CR=1 S=0 компаратора приведения на рис. 4.17 б).

A<B –> CR=0 S≠0

По затратам оборудования такая схема уступает предыдущей (сумматор сложнее). УГО компаратора показано на рис. 4.17 в). Серийно выпускаемые COMP К561ИП2, К555СП1. Входы > = < – для наращивания разрядности.