- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

Глава 5. Сумматоры.

§ 5.1 Полусумматор. Инкрементор.

Схему сложения двух чисел: переноса Сr и числа А называют полусумматором.

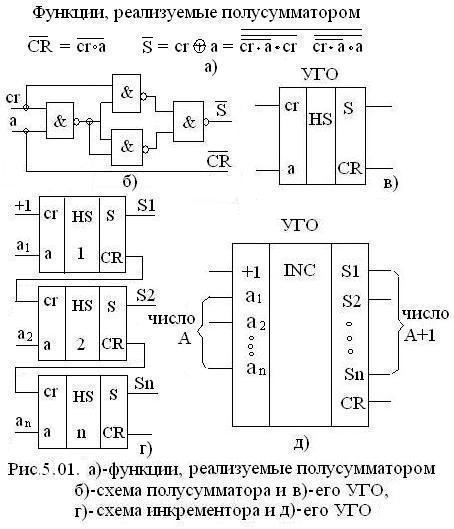

Функции, реализуемые полусумматором, приведены на рис. 5.1 а), а его схема на рис. 5.1 б). УГО полусумматора на рис. 5.1 в).

Полусумматоры, соединенные последовательно по цепи переносов, образуют инкрементор, который иногда называют накапливающим сумматором. Схема инкрементора и его УГО показаны на рис. 5.1 г) и д) соответственно.

При подаче на вход +1 «0»икрементор записывает число А без изменения.

Если на этот вход подать «1», то он прибавляет ее к числу А (выход А+1).

В инкременторе число А и А+1 существует только одновременно на входе и выходе, то есть схема инкрементора является схемой без памяти. Инкрементор можно построить и с параллельным переносом или групповым.

По аналогии с инкрементором строится и декрементор – узел, уменьшающий число А на «1», если на вход займа «-1» подать единичный сигнал (строится по аналогии со сдвигающим RG влево).

§5.2 Сумматор.

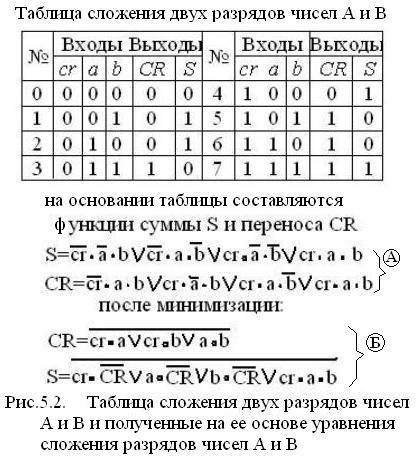

Н а

основании таблицы суммирования двух

разрядов чисел А и В (рис.5.2) можно

составить логические выражения при

суммировании для суммы S

и переноса CR

(выражения

а

основании таблицы суммирования двух

разрядов чисел А и В (рис.5.2) можно

составить логические выражения при

суммировании для суммы S

и переноса CR

(выражения

![]() ).

).

Основная

задача – минимизировать эти функции.

После минимизации получим функции

суммирования для суммы S

![]() и

переноса CR.

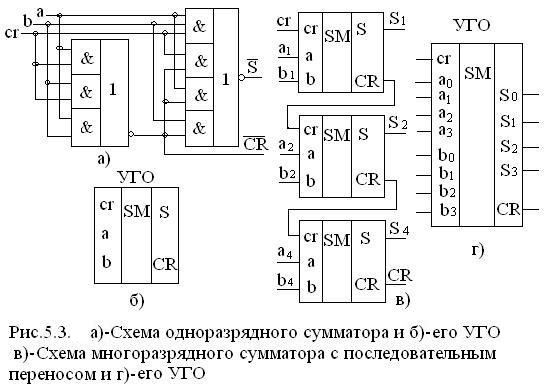

На основании функций

можно построить одноразрядный сумматор

– рис.5.3 а).

и

переноса CR.

На основании функций

можно построить одноразрядный сумматор

– рис.5.3 а).

Следует

отметить, что схема одноразрядного

сумматора, построенная на основании

функций

в базисе И-ИЛИ-НЕ имеет 17 выводов, что в

2 раза меньше, чем в схеме, построенной

на основании функций

![]() (цена минимизации).

(цена минимизации).

Задержка сумматора: для S – 1τ , для CR – 2τ. Последовательным соединением одноразрядных сумматоров по тракту переноса CR получен многоразрядный сумматор с последовательным переносом (рис.5.3 в), его УГО на рис.5.3 г.

Особенности схемы.

На

входе одноразрядного сумматора сигнал

cr,

а на выходе –

,

следовательно, между разрядами надо

ставить инверторы, что увеличивает

задержку многоразрядного сумматора.

Поэтому на практике для решения этой

проблемы используется свойство

самодвойственности логических функций:

значение функции интерпретируется при

инвертировании ее входных аргументов.

Это видно из сравнения строк таблицы

суммирования (рис.5.2): 3 и 4, 2 и 5, 1 и 6, 0 и

7. Исходя из этого факта при построении

многоразрядного последовательного

сумматора тракты переноса CR

соединяются напрямую, а на те разряды,

на которые поступает инверсный перенос

,

входные аргументы инвертируют и получают

на выходе CR

без инверсии. Если на входы разрядов

сумматора данные подаются с выходов

регистра (это чаще всего и делается), то

данные для соответствующих разрядов

снимаются с инверсных выходов этого

регистра.

,

следовательно, между разрядами надо

ставить инверторы, что увеличивает

задержку многоразрядного сумматора.

Поэтому на практике для решения этой

проблемы используется свойство

самодвойственности логических функций:

значение функции интерпретируется при

инвертировании ее входных аргументов.

Это видно из сравнения строк таблицы

суммирования (рис.5.2): 3 и 4, 2 и 5, 1 и 6, 0 и

7. Исходя из этого факта при построении

многоразрядного последовательного

сумматора тракты переноса CR

соединяются напрямую, а на те разряды,

на которые поступает инверсный перенос

,

входные аргументы инвертируют и получают

на выходе CR

без инверсии. Если на входы разрядов

сумматора данные подаются с выходов

регистра (это чаще всего и делается), то

данные для соответствующих разрядов

снимаются с инверсных выходов этого

регистра.

По определению сумматором называют комбинационное логическое устройство для выполнения арифметического сложения двух чисел, представленных в двоичном коде. Сумматор является основным узлом арифметико-логического устройства ЭВМ – ALU.

Сумматор имеет:

n – входов разрядов числа А.

n – входов разрядов числа В.

cr – вход переноса из младшего разряда сумматора.

CR – выход переноса в старший разряд сумматора.

n – выходов разрядов суммы S.

Задержки распространения сигналов:

tcr,S – от входа переноса до установления суммы S.

tА,S– от входов слагаемых до выходов S при cr – const.

tcr,CR– от входа cr до выхода CR при постоянных слагаемых.

tA,CR– от входа слагаемых до выхода CR.

Задержка многоразрядного сумматора с последовательным переносом:

tcr вх,СR вых= tcr1,CR1+ tcr2,CR2+… +tcr n,CR n=n tcr,CR,

где n – число разрядов в сумматоре,

tcr,CR – задержка в одном разряде.

Примеры серийно выпускаемых сумматоров:

К155ИМ1 – двухразрядный, данные вводятся с регистра – прямой и инверсный выход,

К155ИМ-2,3 – четырехразрядные, с переносом через разряд, используется инвертор.

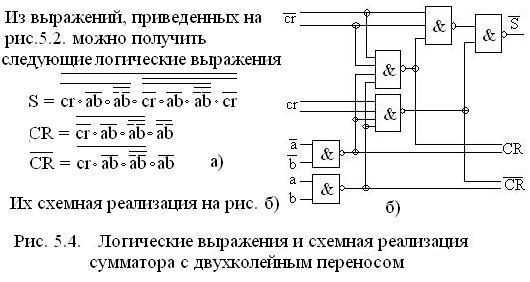

Иногда в сумматорах для решения проблемы переносов в разрядах используются сумматоры с двухколейным переносом (рис. 5.4 а и б).

Логические функции суммирования (а) получены из соотношений (рис. 5.2). Схема реализации рис. 5.4 б.

Особенности схемы: перенос вырабатывается парафазным кодом по двум трактам CR и , что позволяет при построении многоразрядного сумматора для переноса между разрядами CR или для получения суммы всегда одной фазности.