- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

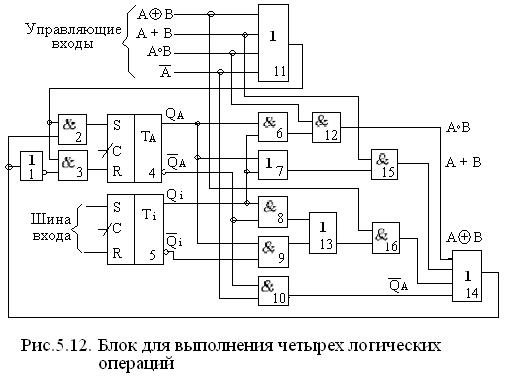

§ 5.5 Блоки для логических операций

В составе процессора ЭВМ (в ALU) есть блоки, выполняющие до 16 логических операций. Общая структурная схема блоков приведена на рис. 5.11 а).

Пример построения схемы, реализующей 6 логических операций , приведенных на рис. 5.11 б), показан на рис. 5.11 в). Каждая из функций Fi ,выполняемая определенным логическим элементом: ИЛИ ,ИЛИ-НЕ,И и т.д. или их совокупностью.

Ко входам Xi и Yi подключаются соответствующие выходы (разряды) буферных регистров ALU ( о котором будет сказано ниже) RGA и RGB,а ко входам Vio ÷Vis- соответствующие выходы дешифратора команд ДС.

Типов

логических блоков может быть много. В

качестве примера на рис. 5.12 приведена

другая схема блока, для одного разряда

выполняющая четыре логические операции.

ТА(эл-т 4)-является триггером (разрядом) регистра сумматора ALU-RGSM (аккумулятора) а Т1(S)-триггер (разряд) входного регистра ALU-RGB.

Остальные элементы составляют логический блок. Блок выполняет 4 операции: конъюкции, дизъюкции , арифметического сложения, сложения по

mod2 и инверсии между разрядами. Отличительная особенность блока – все операции могут выполняться одновременно и поразрядно между ТА и Т1 , но результат записывается в один триггер (в нашем случае в ТА) поэтому одновременная подача управляющих сигналов недопустима.

Выбор операции осуществляется подачей «1» на соответствующий управляющий вход блока.

Например:

реализовать операцию Ai![]() Bi

подачей на него «1».

Bi

подачей на него «1».

Тогда: сигналы QА и i проходят на конъюнктор (9), а А и Qi – на элемент (8), с выходов элементов (8) и (9) результаты конъюнкции подаются на ИЛИ (13), на выходе которого получается результат:

QА · i + А · Qi = Ai Bi.

Этот результат при подаче «1» на вход элемента (16) пересылается в (14) и далее записывается через элемент (2) в Та (4), где и фиксируется.

Другие операции выполняется аналогично. Блок может быть расширен для выполнения и других операций.

Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

ALU – функционально законченный узел процессора ЭВМ, предназначенный для выполнения арифметических операций по обработке информации.

Основные операции, выполняемые ALU:

Арифметические (все они сводятся к сложению), до 50% от всех выполненных операций.

Логические (до 16 операций – до 45% от всех выполнений).

Остальные 5% - операции управления.

Основные связи ALU в составе процессора показаны на рис 6.1.

ALU – основные части которого сумматор и комбинационная логическая схема (блок логических операций) имеет 2 группы входов (портов) Вх1 Вх2 для приема данных (операторов) и 2 группы выходов: Вых1 – выход результата операции, выполненной ALU (сумматором) или логическим блоком. Вых2 – выход осведомительной информации (признаков) результата операции: переполнение разрядной сетки, знак результата деления на «0» и т.д.

Эта информация используется для коррекции управляющих сигналов в блоке управления.

RG1 и RG2 – регистры (их иногда называют буферными) для приема операторов из памяти ЭВМ.

RG SM – регистр сумматора (его чаще называют аккумулятором) для приема из сумматора или блока логических операций результата операции и передачи его либо в RG1 (RG2) либо в память ЭВМ.

SM – сумматор.

6.1 Классификация ALU.

ALU классифицируются по нескольким признакам:

По способу действия над операциями:

- последовательные, когда операнды представлены в последовательном коде и операции над ними выполняются разряд за разрядом.

- параллельные, когда операнды представлены в параллельном коде и операции выполняются над всеми разрядами одновременно.

По способу представления чисел:

- ALU для чисел с фиксированной точкой.

- ALU для чисел с плавающей точкой.

- ALU для десятичных чисел.

По характеру использованных блоков ALU:

Блочные, когда операции над числами с фиксированной и плавающей точкой, с десятичными числами и алфавитно-цифровыми полями выполняются в отдельных (специализированных) блоках. Обладают высоким быстродействием. Т.к. блоки могут работать параллельно.

Многофункциональные ALU, когда все операции выполняются одними и теми же блоками, которые коммутируются нужным образом.

ALU управляются сигналами, инициирующие выполнение определенных микроопераций. Последовательность таких сигналов определяется кодом операции и осведомительными сигналами из RGпр по результатам предыдущей операции.

Проектирование ALU в основном состоит в:

Выборе кодов для представления данных

Определении алгоритмов выполнения операций

Выборе структур операционных блоков и набора микроопераций, реализуемых ими

В объединении блоков в один многофункциональный узел – ALU.

6.2 Языки описания вычислительных устройств.

ЭВМ – одна из самых сложных технических систем, описание структуры и функционировании которой производится на различных уровнях ее детализации. Каждому уровню описания соответствуют определение средства.

Потребность в таких формализованных средствах описания диктуется не только потребностями современной методологии изучения сложных систем но и потребностями моделирования проектных решений при создания системы, автоматизации проектирования и т.д.

Для формированного описания часто используют различные «языки описания», например, такие, как показаны на рис 6.2.

В нашем курсе рассматриваются в основном узлы системы, поэтому чаще всего используется язык микроопераций, который иногда называют регистровым или языком регистровых передач. Несколько примеров использования этого языка приведены на рис 6.3.

Пояснение: например слово –число Х15[0-n]: здесь Х15 – идентификатор – это произвольная последовательность букв и цифр, начинающаяся с буквы. [0-n] – разрядный указатель номеров разрядов.

Определения:

Элементарная операция, выполняемая за один тактовый интервал – называется микрооперацией.

В некоторые тактовые интервалы могут параллельно выполняться под действием управляющих сигналов несколько микроопераций. Совокупность таких операций называют микрокомандой.

Последовательность микрокоманд, обеспечивающая выполнение операции (например, сложение 2х числе) называют микропрограммой операции.

Микрооперация – это преобразование над операндами: один или несколькими, может быть одноместной или многоместной, описывается микрооператором (рис 6.3. пункт 4) и сопровождается меткой.

Аналогично описание и микрокоманды, представляющее собой метку и раздельную запятыми последовательность микрооператоров.

Обычно даже простые операции выполняются за несколько тактов. Например, микрокоманда – принять адрес в RG – адреса выполняются за два такта:

Уст.0 RGA: RGA:=0

Пр.А2: RGA:=RGK[A2]

Здесь: Уст.0 – обозначение управляющего сигнала для обнуления RGA.

Пр А2 – сигнал приема (записи) адреса А2 из регистра команды RGK.

Микропрограмма может быть в виде графа, в котором вершины соответствуют микрокомандам.

6.3 ALU для сложения (вычитания) чисел с фиксированной точкой.

В ALU операция сложения сводится к арифметическому сложению чисел, представленных в прямом или дополнительном кодах. Обратный код применяется редко, поскольку имеет 2 представления нуля +0 и -0, что затрудняет анализ результатов операции. Алгоритм операции сложения определяется типом применяемых кодов.

Функциональная схема ALU сложения (вычитания) приведена на рис 6.4.

Управляющие сигналы вырабатываются управляющим блоком в соответствии с кодом операции. Каждый управляющий сигнал идет по своему тракту: например, в RG1 может поступать 4 типа сигналов:

Сигнал обнуления регистра

Сигнал записи кода операнда из BDIO

Сигнал выдачи кода с прямых выходов регистра

Сигнал выдачи кода с инверсных выходов (при инвертировании кода)

Работа ALU.

Из оперативной памяти ЭВМ по шине BDIO поступают команды А и В, первое слагаемое (или уменьшаемое) в RGB, второе слагаемое в RG1. RG1 и RGA имеют прямую и инверсную связь для передачи кода операнда, прямую при сложении, инверсную при вычитании. Вычитание производится по формуле (А+¬В) где ¬В значение операнда В в обратном коде. К результату прибавляется +1. Результат суммирования (или вычитания) передается в RGSM и далее по шине BDIO в память.

При сложении двоичных кодов, включая и их знаковые разряды следует учитывать следующие правила:

Если возникает перенос из знакового разряда суммы при отсутствии переноса в этот разряд, или возникает перенос в знаковый разряд при отсутствии переноса из него, то имеется переполнение разрядной сетки соответственно при отрицательных и положительных суммах.

Если нет переносов из знакового разряда и в знаковый разряд суммы, или есть оба эти переноса, то переполнение разрядной сетки отсутствует и

При «0» в знаковом разряде суммы положительная

При «1» - отрицательная

На входы RGпр поступают:

Значения всех разрядов сумматора СМ[0] и CM[1÷n-1]

Перенос из знакового разряда Пн CM[0]

Перенос в знаковый разряд Пн CM[1]

В результате этого, после выполнения операции в спец. Комбинационной схеме (на рис 6.4 – отсут-т) формируются признаки по соответствующим соотношениям показанным на рис 6.5.

На рис 6.6 приведена временная диаграмма работы ALU при сложении (вычитании) чисел с фиксированной точкой.

Из диаграммы видно, что сложение выполнено за 5 тактов, а вычитание за 6 тактов с добавлением +1.

6.4 Методы умножения двоичных чисел.

В ЭВМ операция умножения сводится к операции сложения двух чисел и сдвигу разрядов. Могут применяться 4 основных метода умножения. Примеры умножения приведены на рис 6.7.

Выводы по методам умножения.

1 метод.

После каждого сдвига множимого выполняется операция сложения.

Операция умножения состоит из n-циклов (n-разрядность множителя)

ALU при этом методе должно иметь:

Регистр множителя (n-1) разрядный

Сумматор и регистр сумматора 2(n-1) – разрядные.

Метод практически не применяется из-за большой разрядности регистров и сумматора.

2 метод.

Выравнивание суммы частных произведений по старшим разрядам.

Младшие разряды произведения по мере их формирования можно перемещать в освободившиеся разряды множителя, поскольку далее не используются, а старшие – записать в RGSM. И результат снимать с двух регистров. Метод часто применяется вследствие необходимости одинарной длины разрядности регистров буферных и сумматора.

3 метод.

Сумматор и RGSM необходим 2(n-1) – разрядности.

Последовательность действий в цикле определяется старшим разрядом множителя.

Метод применяется в некоторых ALU, так как позволяет без дополнительных цепей сдвига выполнять деление чисел, в то время как во 2м методе для деления необходимы цепи сдвига в регистре множимого (при делении – частного) и в сумматоре частичных произведений (разностей при делении).

4 метод.

Необходимы двойные разрядности регистра сумматора и сумматора.

При делении чисел требуются цепи сдвига в регистрах.

Сумма частичных произведений неподвижна, поэтому можно совмещать во времени операции сдвига сложения.

В заключение следует отметить, что выбор метода умножения определяется соотношением затрат оборудования на цепи сдвига, разрядности и быстродействием.

6.5 ALU для умножения чисел с фиксированной точкой.

Применяется второй метод. Рис 6.8.

Алгоритм умножения

Берутся модули от сомножителей.

Исходное значение SM частичных произведений приравнивается к нулю.

Если цифра множителя в разряде равна «1» то к сумме частичных произведений прибавляется множимое, если «0» - не прибавляется.

Производится сдвиг суммы частичных произведений вправо на один разряд.

Пункты 3 и 4 выполняются для всех разрядов множителя начиная с младшего разряда

Произведению присваивается «+» если знаки сомножителей одинаковы и «-» в противном случае.

Работа ALU.

В RG1 принимается множимое, RGB – обнуляется, в сч. Циклов (на схеме не показан) заносится число разрядов множителя, в RGB заносится множитель. Далее идет процесс умножения: в зависимости от значения младшего разряда множителя 0 или 1 к частному произведению прибавляется 0 или множимое соответственно.

Полученная сумма в RGSM со сдвигом на разряд вправо передается в RGB. Одновременно множитель сдвигается на разряд вправо путем косой передачи из RG2 в RG2’ и возврата в RG2.

Старшие разряды RG2’ при этом освобождаются и в них заносятся младшие разряды получаемого произведения.

Содержимое счетчика циклов с каждым перемножением уменьшается на 1 и при достижении в нем «0» процесс перемножения прекращается. В результате RGSM и RG2’ будут храниться соответственно старшие и младшие разряды произведения.

Особенностью умножения целых чисел является необходимость представления результата умножения двоичным словом. При этом число цифровых разрядов двойного слова 2N-1 на 1 больше числа 2n-2 цифровых разрядов произведения двух чисел, содержащих n-1 цифровых разрядов.

Поэтому, после перемножения чисел надо результат сдвинуть на разряд вправо, для правильного его расположения в разрядной сетке формата двойного слова. После сдвига результат операции передается на шину данных BDIO.

Умножение целых чисел со знаками, представленных в прямом и дополнительном кодах производится с применением модифицированного сдвига суммы частичных произведений.

6.6 О применении прямого, обратного и дополнительного кодов при выполнении арифметических операций в сумматоре.

Общеизвестно, что в сумматоре ALU реализуется только операция сложения, назовем условно, положительных операнд (чисел).

Положительные числа во всех кодах совпадают. Отрицательные представляются в обратном и дополнительном кодах, причем в операциях вычитания знак вычитаемого автоматически изменяется на противоположный. Знаковый разряд и цифровая часть числа рассматриваются как одно целое и одинаково участвуют в операции. При сложении в обратных кодах перенос из старшего знакового результата поступает на вход переноса младшего разряда (циклический перенос), а при сложении в дополнительных кодах этот перенос не учитывается.

Для напоминания на рис 6.9 приведена таблица соответствия прямого, обратного и дополнительного кодов для отрицательных чисел и даны примеры операций с применением обратного и дополнительного кодов.

На рис 6.10 приведены примеры возможного переполнения разрядной сетки при сложении чисел с одинаковыми знаками и применения модифицированных кодов для обнаружения переполнения.

6.7 ALU для деления целых чисел с фиксированной точкой.

Деление чисел сводится к выполнению последовательности вычитания делителя, сначала из делимого, затем из образующихся частичных остатков и их сдвига. Фактически деление заменяется суммированием с применением дополнительных кодов.

Деление можно осуществлять двумя основными способами:

Деление с неподвижным делимым и со сдвигаемым вправо делителем. Способ основан на копировании ручного деления. (самостоятельно поделить 2 числа, записать алгоритм деления и построить структурную схему ALU для этого способа).

Деление со сдвигаемым делимым и неподвижным делителем. Схема ALU для такого способа приведена на рис 6.11.

Неподвижный делитель В в дополнительном коде заносится в RGA, делимое А, сдвигаемое влево относительно делителя В заносится старшими разрядами в RGB, младшими в RG2. Деление начинается со сдвига делимого А путем косой передачи его в RGSM (старшие разряды) и в RG2’ (младшие разряды), после чего делимое передается из RGSM в RGB и из RG2’ в RG2.

Далее в SM происходит вычитание делителя (в RGA), образуется частичный остаток (путем подсуммирования +1) и цифра частного (1 если остаток >0 и 0 если остаток <0) заносится в освободившийся после сдвига А разряд RG2.

При этом если остаток <0, то его значение восстанавливается до предыдущего значения.

Алгоритм деления приведен на рис 6.12.

Недостаток способа: нужен дополнительный такт для восстановления остатка, поэтому иногда применяются способы деления без восстановления остатка.

Суть деления с восстановлением частичного остатка заключается в следующем:

Если при делении в результате вычитания делителя из делимого (частичного остатка) выясняется, что делимое или очередной частичный остаток оказались больше или равны делителю, то в очередной разряд частичного остатка заносится «1» и полученный частичный остаток сдвигается влево на один разряд.

Если же выясняется, что после вычитания делителя частичный остаток оказался меньше делителя, то в очередной разряд частного заносится «0», к полученному остатку прибавляется делитель, чтобы восстановить частичный остаток до вычитания, после чего результат прибавления сдвигается влево на один разряд. Описанные процессы продолжаются до получения n-разрядного частного. Такой метод и называется делением с восстановлением остатка на рис 6.13 приведен пример подобного деления.

Примечание. Часто в ЭВМ используется деление без восстановления остатка. Суть его в следующем:

Если результат вычитания делителя из делимого получен отрицательный, то частичный остаток не восстанавливается путем прибавления делителя, а на следующем шаге деления вместо вычитания делимого производится его прибавление к частичному остатку. Если результат при этом остался отрицательным, то в очередную цифру частного записывается «0» и на следующем шаге так же выполняется сложение. Если результат после сложения положительный то в разяряд частного записывается «1» и на следующем шаге производится вычитание.

6.8 Операции над числами с плавающей точкой. Представление чисел в ЭВМ.

При представлении чисел с фиксированной точкой, точка ставится в определенном месте относительно разрядов модуля числа в разрядной сетке. Рис 6.14

точка перед старшим разрядом.

Здесь

при переполнении разрядной сетки (при

потере младшего разряда) погрешность

не превышает величину

.

Метод применяется редко.

.

Метод применяется редко.

Точка перед младшим разрядом.

Здесь

модуль только целое число. При занесении

числа в ячейку превышающего число

теряется старший разряд и погрешность

может достигнуть 100%. Например, 11112

(1510)

при потере старшего разряда становится

01112

(710).

теряется старший разряд и погрешность

может достигнуть 100%. Например, 11112

(1510)

при потере старшего разряда становится

01112

(710).

Числа с плавающей точкой представлены иначе. Рис 6.14 п.2.

Порядок P числа может быть как положительным, так и отрицательным. Числа с плавающей запятой могут быть представлены в форматах с основанием 2, 8, 16 и двоично-десятичном.

Нормализованным числом принято считать число, у которого старший разряд мантиссы не равен нулю. ЭВМ автоматически нормализует число.

Например: получен результат, в котором r-старших разрядов мантиссы равны 0. Нормализация заключается в сдвиге мантиссы q на r-разрядов влево и одновременным умножением порядка P на r единиц. При этом в младшие освободившиеся разряды мантиссы записываются нули.

После такой операции число не меняется, а условие нормализации будет соблюдено. Поскольку арифметические действия над числами с плавающей точкой требуют отдельных операций над мантиссами и порядками, то операции над ними сводят к операциям над целыми положительными числами, применяя представление чисел со смещенными порядками. Для этого при записи числа в ячейку памяти к его порядку Р прибавляется целое число-смещение N=2k, где K-число двоичных разрядов, используемых для расположения модуля порядка в разрядной сетке. Тогда смещенный порядок есть Рсм = P+N, который всегда будет положительным, причем для его представления надо такое же число разрядов, как и для модуля Р.

Особенность Рсм в том, что если P’ > P” то и для смешенных верно Рсм’ > Рсм”. Это говорит о том, что смещение порядков не влияет на операции над числами.

6.9 Сложение и вычитание чисел с плавающей запятой.

Сложение и вычитание чисел производится на формуле (в предположении что X>Y) приведенной на рис 6.15.

Используемая разрядная сетка показана на рис 6.15(г).

Алгоритм сложения и вычитания.

Производится выравнивание порядков слагаемых Х и Y: порядок меньшего по модулю числа принимается равным порядку большего числа, а мантисса меньшего сдвигается влево на число S-ичных разрядов, равное разности порядков.

Производится сложение (вычитание) мантисс и получается мантисса суммы (разности) чисел X и Y.

Порядок суммы (разности) принимается равным порядку большего числа.

Полученная сумма (разность) нормируется. Арифметические действия над порядками и мантиссами выполняются либо отдельными устройствами, либо последовательно одним устройством, например, ALU рассмотренным ранее.

Операция сложения (вычитания) состоит из этапов:

Прием операндов X и Y

Выравнивание порядков со сдвигом мантисс

Сложение (вычитание) мантисс

Нормализация результата

Структурная схема ALU для сложения (вычитания) чисел с плавающей точкой приведена на рис 6.16.

Работа ALU.

Прием операндов. Прием первого слагаемого (уменьшаемого) X, фиксация знака в триггере ТЗН , установка RGA в «0». Прием второго слагаемого (вычитаемого) Y в RG3, фиксация знака ТЗН , установка RGB в «0».

Операции над порядками. Значения порядков из разрядов операндов α1÷α7 регистров RG1 и RG3 подаются в RGC и RGD соответственно. Далее в блоке обработки порядков происходит их сравнивание по результатам которого: мантисса с меньшим по модулю порядком сдвигается влево на число разрядов, равное разности порядков. За порядок результат операции сложения (вычитания) мантисс принимается больший из порядков.

При сравнении порядков возможны 5 случаев их соотношения и соответствующих операций.

PX – PY > m, где m – число разрядов мантиссы числа Х. за результат операции принимается слагаемое Х, так как при сдвиге мантиссы слагаемого Y все ее разряды примут нулевое значение.

PY – PX > m, где m – число разрядов мантиссы числа Y. За результат операции принимается слагаемое Y по той же причине.

PX – PY = 0, - производится суммирование мантисс числа Х и Y.

PX – PY = K1, (K1 < m) – мантисса числа Y сдвигается на K1 разрядов.

PX – PY = K2, (K2 < m) – мантисса числа Х сдвигается на K2 разрядов.

Процесс сдвига мантисс заключается в следующем: В счетчик циклов СТЦ из блока обработки порядков заносится число разрядов ( К1 или К2) на которое необходимо сдвинуть. Далее, по мере сдвига мантиссы содержимое счетчика уменьшается и по достижении содержимого счетчика СТЦ = 0. Сдвиг прекращается.

Полученные модули мантисс хранятся в RG1 и RG3, их знаки в триггерах знака, а принятый порядок в RGCT1.

Сложение мантисс.

При одинаковых знаках операндов. Модули мантисс передаются в RGA и RGB без изменения и складываются в сумматоре SM. Если окажется, что в разряде SM[7] = 1, то возникло переполнение разрядной сетки, поэтому сумма сдвигается на разряд вправо, а порядок Р увеличивается на 1: т.е. в RGCT1:= RGCT1+1.

Если после этого в RGCT1[α0] = 1, то возникло переполнение порядка, вырабатывается сигнал прерывания вычислительного процесса.

Если переполнения порядка нет, то в RGSM[α1÷α7] заносится порядок из RGCT1, в RGSM[α0] – знак мантиссы из сх.зн., а в RGSM[α8÷α32] мантисса суммы.

При разных знаках операндов. Отрицательная мантисса передается в RGA или RGB в обратном коде, производится суммирование в SM с положительной мантиссой с дальнейшим подсуммированием +1 к результату. Знак результата фиксируется в соответствующем триггере знака. Если полученный результат нормализованный, т.е. в SM[0] ≠0 то в RGSM заносится:

Знак результат в RGSM[α0]

Порядок из RGCT1 в RGSM[α1÷α7]

Модуль мантиссы результата из SM в RGSM[α8÷α32].

Если результат нормализован, т.е. SM[α8,α9,…] = 0 и нет исчезновения мантиссы, т.е. SM[α8÷α32] ≠ 0, то производится нормализация сдвигом мантиссы влево с одновременным уменьшением порядка: т.е. RGCT1:=RGCT1 -1.

При отрицательном переполнении порядка, т.е. при RGCT1[0]формируется признак исчезновения порядка (т.е. результат = 0). Если нормализация происходит без исчезновения порядка, то формируется результат в RGSM и кодов знака, порядка и мантиссы.

Примечание: в операциях с числом с плавающей точкой сложение и вычитание выполняется приближенно, т.к. при выравнивании порядков может произойти потеря младших разрядов одного из операндов. Погрешность в этом случае всегда отрицательна и может доходить до «1» младшего разряда. Поэтому применяется округление результат, для чего используется дополнительный разряд в SM, в который после суммирования добавляется «1».

6.10 Умножение чисел с плавающей точкой.

Производится по формуле, приведенной на рис 6.15 б. Из формулы видно, что при перемножении:

Порядки складываются

Мантиссы перемножаются

Произведение нормализуется и

Ему присваивается знак «+» если знаки сомножителей одинаковы и «-» в противном случае.

Если одна из мантисс равна «0» произведение принимается равным нулю и переполнение не производится.

Если при суммировании порядков возникло переполнение порядка и его знак отрицательный, то результат умножения принимается равным «0» т.к. произведение окажется меньше разрядной сетки.

Если возникло переполнение порядка со знаком «+», то может оказаться, что после нормализации результата перемножения мантисс переполнение исчезнет. Поэтому в этом случае факт переполнения запоминается до окончания нормализации результата.

Как уже упоминалось, операции над порядками могут выполняться в разных блоках ALU или в одном:

В сумматоре SM, в котором выполняются операции перемножения мантисс – последовательно: сначала над порядками, затем над мантиссами.

Операции над порядками в блоке логических операций, а над мантиссами в SM ALU.

Схема ALU для второго случая приведена на рис 6.17.

Назначения RG в схеме:

RG1 – для приема и хранения множимого А.

RG2 и RG2’ – для приема мантиссы множителя В и ее сдвига в процессе перемножения.

RG3 – для приема знака и порядка множителя В и последующего приема частных произведений из RGSM.

RGА – для передачи на сумматор мантиссы множимого А, порядка его КПС блока логических операций и знака в ТЗН.

RGВ – для передачи в SM частичных произведений порядка множителя В в RGD блока логических операций.

RGSM – для приема частичных произведений из SM и последующего результата перемножения: знака, порядка и мантиссы.

RGCT1 – для хранения порядка результата.

СЦТ – счетчик циклов, используется при нормализации.

Работа ALU.

Прием операндов: прием множимого А в RG1, фиксация его знака в NPY? Установка RGA в «0». Прием множителя В: знака и порядка в RG3, а мантиссы В в RG2, фиксация знака ТЗН, установка RGВ в «0».

Передача порядков чисел А и В в RGС и RGD соответственно, их выравнивание в блоке логических операций со сдвигом соответствующей мантиссы в RG1 или RG2, фиксация принятого порядка в RGСТ1. (сдвиг осуществляется под управлением счетчика циклов).

Перемножение мантисс. Передача мантиссы множимого А в RGА и далее в сумматор SM. При значении первого разряда мантиссы множителя В в RG2 равного «1», мантисса числа А фиксируется в RGSM как первое частное произведение и передается в RG3. После этого мантисса в RG2 через RG2’ сдвигается влево на разряд и при значении этого разряда равном «1» процесс повторяется. Если же значение разряда равно «0», то частное произведение в RGSM сдвигается на разряд влево и передается в RG3. (без суммирования). Все повторяется для всех разрядов множителя В.

Окончательный результат фиксируется в RGSM: знак из ТЗН, порядок из RGСТ1 и мантисса из SM, далее из SM на шину BDI.

Таким образом логично сделать вывод – умножение чисел это процесс суммирования мантиссы множимого и частичным произведениями столько раз сколько разрядов в мантиссе числа В, т.е. процесс аналогичен перемножению чисел с фиксированной точкой.

6.11 Деление чисел с плавающей точкой.

Производится в соответствии с формулой приведенной на рис 6.15 в.

Общие замечания: при делении чисел с плавающей точкой обычно, мантисса частного равна частному полученного при делении мантиссы делимого на мантиссу делителя, а порядок частного равен разности порядков делимого и делителя. Частное нормализуется и ему присваивается «+» если знаки делимого и делителя одинаковы и «-» в противном случае.

Если делимое = 0, в частное записывается 0 без выполнения деления.

Если при вычитании порядков образовалось положительное переполнение или если делитель = 0 деление не производится и формируется сигнал прерывания процесса.

При делении нормализованных чисел с плавающей точкой может оказаться, что мантисса делимого много больше мантиссы делителя и тогда мантисса частного может образоваться с переполнением сетки, поэтому часто перед делением мантисс, нарушают нормализацию делителя сдвигом его на разряд влево. Тогда нарушения нормализации частного не происходит.

Деление мантисс как правило происходит аналогично делению чисел с фиксированной точкой. Отличие только в том, что делимое берется такой же длины, что и делитель.

Однако, учитывая то, что мантисса делимого выражается дробным числом, можно условно принять, что делимое имеет двойную длину с нулями в младшей его половине. В этом случае после сдвигов влево частичных остатков, освобождающиеся разряды заполняются нулями и следовательно деление можно выполнять в точности так же как деление целых чисел.

Схема ALU для деления чисел с плавающей точкой, выполняющего в одном SM. (деление: неподвижное делимое и сдвигаемый делитель) рис 6.18.

Операция деления начинается с приема операндов в RG1 и RG2, фиксация знаков в триггерах знаков ТЗН, передачи слагаемых порядков в RGА и RGВ из разрядов RG1[1÷7] и RG2[1÷7]. Далее вычисляется их разность путем сложения в SM прямого кода смещенного порядка РСМ делителя. Результат заносится в RGСТ1. Далее происходит деление мантисс аналогично делению чисел с фиксированной точкой.