- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

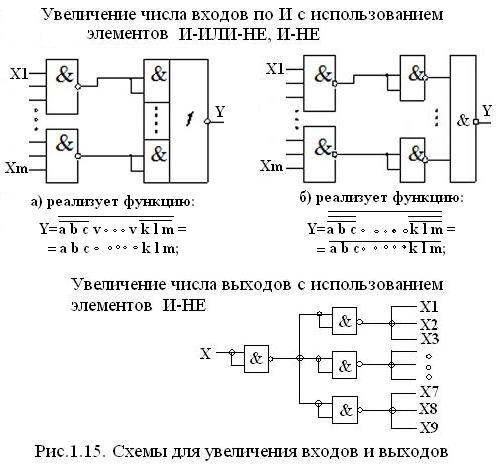

§ 1.8. Разветвления по входу и выходу.

Разветвления можно осуществить следующим способом (Рис. 1.15.).

В любом случае надо учитывать:

Нагрузочные токи и емкости, которые влияют на характеристики схемы.

Каждая линейка (каскад) элементов инвертирует сигнал и вносит дополнительную задержку tр его распространения.

При проектировании схем, также могут вводиться оценочные параметрыдля сравнения узлов:

- суммарная задержка сигнала n·tр, где n – число каскадов,

- число входов М, число выходов Квых, число оборудования Q,

- стоимость.

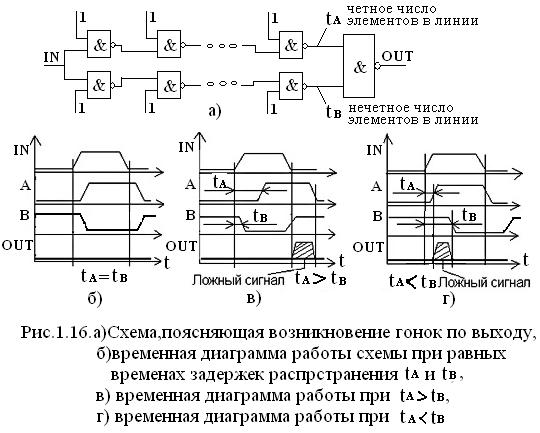

§ 1.9. Гонки.

В качестве примера образования гонок рассмотрим схему и временные диаграммы ее работы, приведенные на Рис. 1.16.

Анализируя данную схему методами алгебры логики можно утверждать, что на выходе OUT всегда должен быть «0». В реальности на выходе OUT может появиться ложный сигнал, поскольку времена задержки распространения по цепям tА и tB могут быть разными. Такое явление получило название «гонки» или «состязания» (races).

При достаточно большой разнице между временами tА и tB ложный сигнал может быть воспринять последующей схемой как истинный логический.

Методы борьбы с гонками (3 основных).

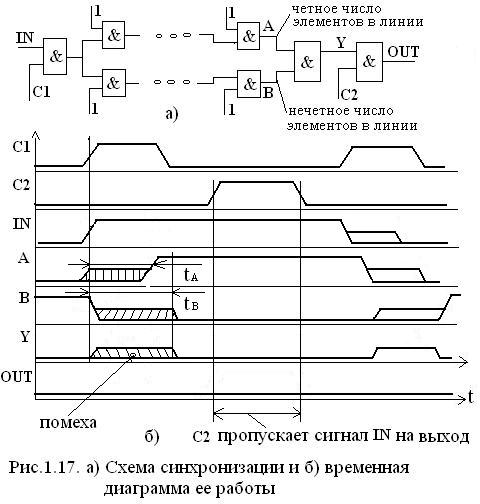

Тактирование (наиболее распространенное). Схема и временная диаграмма ее работы, поясняющая суть метода, приведены на Рис. 1.17.

По всему устройству разводится единая серия тактирующих (синхронизирующих) сигналов, в частности двухфазной синхронизации: С1 и С2, сдвинутых относительно друг друга на полпериода.

Суть метода.

Входной сигнал IN привязывается к синхросигналу С1, то есть входной сигнал проходит по цепям А и В только между двумя соседними С1 (такая привязка сигналов к синхросигналам будет рассмотрена в разделе синхронизация в цифровых устройствах).

Далее сигнал IN может задерживаться по цепям А и В с разными временами распространения, и возникать помеха, но на выход OUT она не попадает, так как элемент И на выходе У закрыт до прихода С2, который подается уже после окончания всех переходных процессов в цепях А и В.

Очевидное требование к С1 и С2:

Временной интервал между С1 и С2 (tсдвига) должен превышать самую большую возможную задержку распространения входного сигнала IN в цепях А и В.

Обычно такой способ борьбы с гонками (и с влиянием переходных процессов на выходах элементов) называют стробированием, а сигналы С1 и С2 – стробами.

Вторым методом борьбы с гонками является построение противогоночных схем.

Как правило в противогоночных схемах вводятся дополнительные связи и элементы так, чтобы нежелательные параллельные пути запирались самим входным сигналом еще до достижение им опасной развилки тракта. Примером такого подхода может служить схема JK-триггера с обратными связями в определенных элементах (JK-триггер рассмотрим позже).

Полезным свойством противогоночных схем оказывается их способность обрабатывать данные по мере их поступления, то есть без привязки к синхронным сигналам, что увеличивает их быстродействие.

Учет минимального времени задержки в цепях. Сложная задача. Во-первых, сложно определять цепи возможного распространения входного сигнала, во-вторых, не всегда известны минимальные времена срабатывания элементов и задержки в линиях, следовательно вероятность появления гонок всегда остается.

Проблема гонок в цифровой технике является весьма серьезной. Сами гонки часто являются причиной непонятных сбоев в работе устройств. Изменение окружающей температуры, старение элементов – все это приводит к изменению времен задержек и ,следовательно, появлению гонок.

Последние два метода применяются редко.

Подробнее о гонках можно прочесть в литературе:

Лазер И.М., Шубарев В.А «Устойчивость цифровых микроэлектронных устройств», М.Радио и связь 1983 г.

«Автоматное управление асинхронными процессами в ЭВМ» под ред. Варшавского В.М. 1986 г.

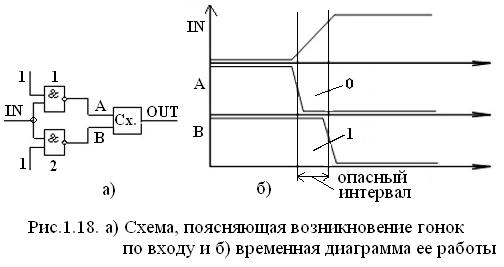

Гонки по входу (Рис. 1.18.)

Возникают вследствие наличия разброса по уровню срабатывания у разных элементов и при излишне пологом фронте сигнала IN.

В интервале «0» - истина, а в интервале «1» - ложь. Результат, принятый последующей схемой будет неверным. Такое явление называется «гонками по входу». Методом борьбы с таким явлением лучше всего является стробирование с установкой на входе схемы конъюнктора.