- •5 Семестр. 51 час. Гр. А-7,8,9-.

- •Глава 1. Системы элементов эвм

- •§ 1.1. Базовый элемент и-не ттл.

- •§1.2. Система элементов мдп (кмдп).

- •§1.3. Система элементов эсл.

- •§ 1.4. Выходные каскады логических элементов.

- •§1.5. Основные параметры логических элементов. Серии микросхем.

- •§ 1.6. Согласование положительной и отрицательной логики.

- •§ 1.8. Разветвления по входу и выходу.

- •§ 1.9. Гонки.

- •Методы борьбы с гонками (3 основных).

- •Глава 2. Устройства эвм.

- •Глава 3. Комбинационные устройства эвм.

- •Глава 4. Счетчики.

- •§4.1 Общие характеристики счетчиков.

- •§4.2 Счетчики с последовательным переносом (непосредственной связью между разрядами).

- •Вычитающий счетчик

- •Счетчики с непосредственной связью и прямым динамическим управлением триггерами.

- •Реверсивные счетчики

- •§4.3. Счетчики с параллельным переносом, с групповой структурой.

- •Работа схемы

- •Счетчики с групповой сруктурой

- •§4.4 Двоично-кодированные счетчики с произвольным модулем счета.

- •Работа счетчика

- •§ 4.5 Счетчики с недвоичным кодированием.

- •§4.6 Счетчик Джонсона.

- •§4.7 Код Грэя

- •§4.8 Полиномиальные счетчики.

- •§ 4.9 Компараторы.

- •Глава 5. Сумматоры.

- •§ 5.1 Полусумматор. Инкрементор.

- •§5.2 Сумматор.

- •§ 5.3 Сумматоры с параллельным переносом.

- •§ 5.4 Двоично-десятичные сумматоры.

- •§ 5.5 Блоки для логических операций

- •Глава 6. Арифметико – логические операции эвм (alu). Основные характеристики alu.

- •Глава 7. Умножители, драйверы, синхронизаторы.

- •Глава 8. Синхронизация и прием внешних сигналов в эвм.

- •Глава 9. Плис – программируемые логические интегральные схемы.

- •§ 9.2. Разновидность плм: ппзу.

- •§ 9.4 Программирование плис.

- •§ 9.5 Расширение функциональных возможностей плм и пмл.

- •§ 9.6 Базовые матричные кристаллы – бмк.

- •Глава 10. Электропитание и безопасность эвм. Введение – напоминание о сети электропитания.

§ 9.4 Программирование плис.

Для реализации функций на ПЛМ необходимо учитывать следующее:

Использовать ПЛМ минимальной сложности, для чего следует уменьшать число термов в заданных функциях их минимизацией.

Программирование ПЛИС производится с помощью специальных устройств – программаторов, в которые вводится информация о необходимости состояния перемычек.

Такую информацию удобно представлять таблицей истинности (программирования).

В таблице используются символы:

Н – переменная входит в прямом виде, следовательно перемычка остается на линии прямого входа, а на его инверсной линии она пережигается.

L – инверсная переменная входит в терм, перемычка сохраняется, а на прямой линии пережигается.

«–» - переменная не входит в терм. Обе перемычки на ее входе можно удалить, либо оставить.

При

входах X· =0,

конъюнктор на выходе будет иметь «0».

=0,

конъюнктор на выходе будет иметь «0».

«А» - ставится в столбце функции и означает наличие связи конъюнктора И с выходом ПЛМ через дизъюнктор ИЛИ, следовательно перемычка должна сохраняться между выходом И и входом ИЛИ.

«–» в столбце функции означает отсутствие перемычки между выходом И и входом ИЛИ.

Последние два пункта обозначают программирование матрицы М2.

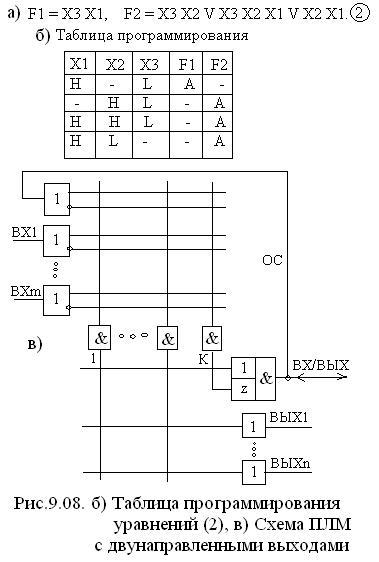

Пример

программирования системы уравнений

![]() приведен на рис.9.08 а) и б).

приведен на рис.9.08 а) и б).

§ 9.5 Расширение функциональных возможностей плм и пмл.

![]() На

рис.9.08 в) приведена схема ПЛМ с

двунаправленными выходами, которая

имеет 4 режима работы, в зависимости от

программирования конъюнктора К.

На

рис.9.08 в) приведена схема ПЛМ с

двунаправленными выходами, которая

имеет 4 режима работы, в зависимости от

программирования конъюнктора К.

Все перемычки на входе конъюнктора К сохранены, на его выходе «0». Буфер Z в третьем состоянии, вход вых/вх работает как вход матрицы М1.

Все перемычки удалены, на выходе К – «1», буфер Z открыт, вывод вх/вых работает как выход М2 – n+1, но его сигнал не используется в матрице М1.

Выход с о.с. – сигнал вывода вх/вых используется в матрице М1.

При управлении буфером Z(вх/вых) – входы К программируются и при «1» на выходе К вывод вх/вых срабатывает как выход М2- n+1. В ПЛМ может быть несколько таких конъюнкторов К и выводов вх/вых, что позволяет менять соотношение числа входов m и выходов n.

Если входов m, выходов n и вх/вых p, то можно иметь:

число входов от m до m+p

число выходов от n до n+p,

При условии, что сумма числа входов и числа выходов не превышает число m+n+p.

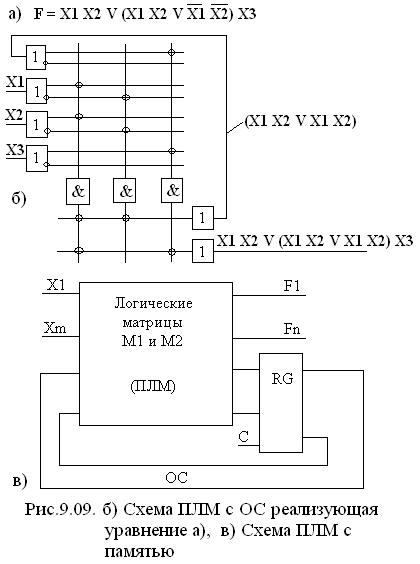

![]() На

рис.9.09 а) и б) приведены примеры а)

уравнения и б) схемы ПЛМ для воспроизведения

функции F

с использованием о.с.

На

рис.9.09 а) и б) приведены примеры а)

уравнения и б) схемы ПЛМ для воспроизведения

функции F

с использованием о.с.

На рис. 9.09 в) приведена схема ПЛМ с памятью (в виде регистра RG), которая может реализовать автомат. Схема характеризуется четырьмя параметрами: m – число входов, n – число выходов, l – число термов, r – число элементов памяти (число разрядов RG).

Результат данного шага обработки информации зависит от результата предыдущего шага благодаря наличию о.с. с RG выходе ПЛМ. Максимальное число внутренних состояний автомата равно 2r. Автомат синхронный, т.к. о.с. активируется по тактовому сигналу С.

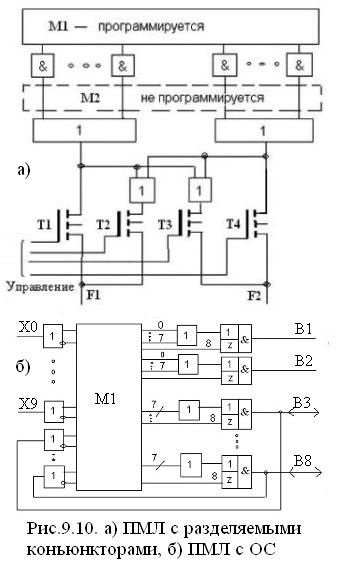

![]() На

рис. 9.10 а) показана структура ПМЛ с

разделяемыми конъюнкторами.

На

рис. 9.10 а) показана структура ПМЛ с

разделяемыми конъюнкторами.

С уть

разделения: для двух смежных ИЛИ в ПМЛ

отводится по несколько конъюгкторов

и, благодаря наличию схем управления

на транзисторах, часть конъюнкторов,

не используемых простой функцией,

например, F1,

может быть переключена для использования

более сложной функцией F2.

уть

разделения: для двух смежных ИЛИ в ПМЛ

отводится по несколько конъюгкторов

и, благодаря наличию схем управления

на транзисторах, часть конъюнкторов,

не используемых простой функцией,

например, F1,

может быть переключена для использования

более сложной функцией F2.

![]() ПМЛ

с обратными связями приведена на рис.9.10

б). Схема имеет 6 двунаправленных входов

В3÷В8. Выходные буферы Z

получают разрешение или запрещение

передачи от матрицы М1.

ПМЛ

с обратными связями приведена на рис.9.10

б). Схема имеет 6 двунаправленных входов

В3÷В8. Выходные буферы Z

получают разрешение или запрещение

передачи от матрицы М1.

В заключение можно отметить, что есть много микросхем (ПЛМ и ПМЛ) с более сложными логическими структурами на выходах, позволяющие реализовывать весьма широкий набор логических выражений. Приведем примеры комплексирования микросхем для увеличения числа их параметров.

На рис. 9.11 приведены:

а) – копмлексирование для увеличения числа n – выходов;

б) – для увеличения числа термов l;

в) – для увеличения числа входов m.