- •Лекция №1. Основные понятия. Первая программа для dos и под Windows. Представление данных в компьютере.

- •Сам ассемблер — программа, которая переводит текст с языка, понятного человеку, в язык, понятный процессору, получает объектный модуль;

- •Компоновщик (linker), который создает исполнимые файлы из одного или нескольких объектных модулей, полученных после запуска ассемблера;

- •Дополнительные вспомогательные программы — компиляторы ресурсов, расширители dos и тому подобное (см. Табл.).

- •Написать её в блокноте, сохранять в *.Asm файл;

- •Из командной строки вызвать ассемблер tasm32.Exe (tasm.Exe);

- •Из командной строки вызвать линковщик tlink32.Exe (tlink.Exe);

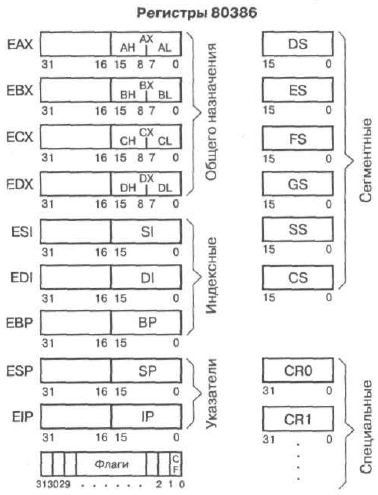

- •Процессоры и их регистры

- •Процессоры x86

- •Регистры процессора

- •Описание регистров

- •Задача: найти старшую часть расширенного регистра (eax, ebx, ..., esi, edi)?

- •0030:4012 (Всё шестнадцатиричное)

- •4) Нельзя использовать сегментный регистр cs в качестве операнда назначения.

- •5) Оператор ptr можно применять и когда требуется принудительно поменять размерность операндов. К примеру, требуется переслать значение 0ffh во второй байт поля flp:

- •Xchg eax,ebx ; обменять содержимое регистров eax и ebx.

- •Xchg al,al ; а эта команда не делает ничего

- •Xchg ax, word ptr [si] ; обменять содержимое регистра ах и слова в памяти по адресу в [si].

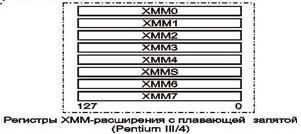

- •Технология sse. Блок xmm

- •Имеются специальные команды сравнения двух вещественных чисел. После их выполнения формируются и помещаются в eflags признаки, характеризующие результат операции.

- •8 Флагов состояния. Эти флаги могут изменяться после выполнения машинных команд;

- •1) Первой известной кодировкой символов была кодировка ascii, и она используется до сих пор. В ascii-кодировке каждый символ занимает 8 бит, или один байт.

- •2. Адресные операнды – задают физическое расположение операнда в памяти с помощью указания двух составляющих адреса: сегмента и смещения. К примеру:

- •6. Структурные операнды используются для доступа к конкретному элементу структуры.

- •7. Записи (аналогично структурному типу) используются для доступа к битовому полю некоторой записи.

- •Команды безусловной передачи управления:

- •Команды условной передачи управления:

- •Команды управления циклом:

- •Лекция № 4. Условные переходы. Арифметиченские команды. Bcd числа.

- •1111111011101101 Инвертируем 0000000100010010

- •Лекция №5. Арифметические команды над целыми числами (продолжение). Арифметические операции над двоично-десятичными числами (bcd числами)

- •К содержимому младшей тетрады al прибавляется 6;

- •Флаг cf устанавливается в 1, тем самым фиксируется перенос в старший разряд для того, чтобы его можно было учесть в последующих действиях.

- •Из содержимого младшей тетрады регистра al вычитается 6;

- •Обнуляется старшая тетраду регистра al;

- •Устанавливает флаг cf в 1, фиксируя воображаемый заём из старшего разряда.

- •Делит ax на 10;

- •Результат деления записывается так: частное – в ah, остаток в al.

- •1) Преобразует двузначное неупакованное bcd-число в регистре ах в двоичное число;

- •2) Полученное двоичное число используется в качестве делимого в операции деления;

- •3) Полученное двоичное число помещается в регистр aх.

- •Деление с остатком

- •Блок-схема вывода результата при делении с остатком Числа с плавающей запятой. Работа с сопроцессором

- •Число имеет вид 1,1100011 × 2-1 или 0,11100011.

- •Переводом в десятичную систему счисления получаем 0,88671875. Лекция №6. Работа с сопроцессором. Команды для работы с fpu. Работа с fpu.

- •Блок-схема вывода на экран вещественного числа, которое хранится в регистре st(0) сопроцессора.

- •Деление с остатком, используя команды целочисленного деления

- •Блок-схема вывода результата при делении с остатком Трансцендентные операции fpu

- •Массивы

- •Перечислением элементов массива в поле операндов одной из директив описания данных. Например:

- •Используя оператор повторения dup. К примеру:

- •4) Mov esi,6*2 ; 2 байта – размер элементов

- •Индексная адресация со смещением — режим адресации, при котором полный адрес формируется из двух компонентов:

- •Базовая индексная адресация со смещением — режим адресации, при котором полный адрес формируется максимум из трех компонентов:

- •Структуры

- •Организовать обращение к элементам структуры.

- •Цепочечные команды или команды обработки строк символов

- •Организация обращения к элементам записи.

- •Iotest record

- •Работа с записями

- •1) Для выделения элемента записи необходимо:

- •2) Чтобы поместить измененный элемент на его место в запись необходимо:

- •3. В конце работы файл следует закрыть.

- •4. Признаком ошибки при выполнении функции dos является взведенный флаг с (переноса).

- •2. Создание файла с усечением существующего до нулевой длины.

- •LpFileName — указатель на asciiz-строку с именем (путем) открываемого или создаваемого файла;

- •DwDesiredAccess — тип доступа к файлу:

- •4) Mov esi,6*2 ; 2 байта – размер элементов

- •Индексная адресация со смещением — режим адресации, при котором полный адрес формируется из двух компонентов:

- •Базовая индексная адресация со смещением — режим адресации, при котором полный адрес формируется максимум из трех компонентов:

- •Структуры

- •Организовать обращение к элементам структуры.

- •Цепочечные команды или команды обработки строк символов

- •Организация обращения к элементам записи.

- •Iotest record

- •Работа с записями

- •1) Для выделения элемента записи необходимо:

- •2) Чтобы поместить измененный элемент на его место в запись необходимо:

- •3. В конце работы файл следует закрыть.

- •4. Признаком ошибки при выполнении функции dos является взведенный флаг с (переноса).

- •2. Создание файла с усечением существующего до нулевой длины.

- •LpFileName — указатель на asciiz-строку с именем (путем) открываемого или создаваемого файла;

- •DwDesiredAccess — тип доступа к файлу:

- •3) Создать и открыть новый файл

- •4) Чтение из файла или устройства

- •5) Переместить указатель чтения/записи

- •1) HFile – хэндл того файла, в котором перемещается указатель.

- •7) Запись в файл или устройство

- •8) Закрыть файл

- •9) Удаление файла

- •Функция 01h – ожидание ввода символа с эхопечатью

- •Функция 0ah – получение строки символов

- •1) Создать каталог

- •2) Удалить каталог

- •5) Определить текущий каталог

- •Перечень функций прерывания 21h, работающих с файлами, которые имеют длинные имена и соответствующие функции api Win32.

- •Перечислим функции api Win32, имеющие отношение к работе с файловой системой.

- •1) В Win32 получить время создания, время последнего доступа и время последней модификации файла можно с помощью функции GetFileTime.

- •3) В Win32 имеется функция GetFileInformationByHandle, с помощью которой можно получить все атрибуты файла:

- •Int 10h ; вызов прерывания bios

- •Основные графические режимы vga

- •Int 10h ; считываем символ и его атрибут

- •Стандартные цветовые палитры в режимах 4,5,6.

- •02H/03h - Чтение/запись секторов.

- •Прямое программирование видеобуфера в текстовом режиме

- •Лекция №6. Работа с сопроцессором. Команды для работы с fpu. Работа с fpu.

- •Лабораторная работа №12. Тема: Графические видеорежимы. Работа с vga-режимами

- •Лабораторная работа № 8. Тема: Работа с файлами

- •Лабораторная работа №5. Тема: Работа с массивами

- •Лекция №1. Основные понятия. Первая программа для dos и под Windows. Представление данных в компьютере.

- •Сам ассемблер — программа, которая переводит текст с языка, понятного человеку, в язык, понятный процессору, получает объектный модуль;

- •Компоновщик (linker), который создает исполнимые файлы из одного или нескольких объектных модулей, полученных после запуска ассемблера;

- •Дополнительные вспомогательные программы — компиляторы ресурсов, расширители dos и тому подобное (см. Табл.).

- •Написать её в блокноте, сохранять в *.Asm файл;

- •Из командной строки вызвать ассемблер tasm32.Exe (tasm.Exe);

- •Из командной строки вызвать линковщик tlink32.Exe (tlink.Exe);

- •Процессоры и их регистры

- •Процессоры x86

- •Регистры процессора

- •Описание регистров

- •Задача: найти старшую часть расширенного регистра (eax, ebx, ..., esi, edi)?

- •0030:4012 (Всё шестнадцатиричное)

- •4) Нельзя использовать сегментный регистр cs в качестве операнда назначения.

- •5) Оператор ptr можно применять и когда требуется принудительно поменять размерность операндов. К примеру, требуется переслать значение 0ffh во второй байт поля flp:

- •Xchg eax,ebx ; обменять содержимое регистров eax и ebx.

- •Xchg al,al ; а эта команда не делает ничего

- •Xchg ax, word ptr [si] ; обменять содержимое регистра ах и слова в памяти по адресу в [si].

- •Технология sse. Блок xmm

- •Имеются специальные команды сравнения двух вещественных чисел. После их выполнения формируются и помещаются в eflags признаки, характеризующие результат операции.

- •8 Флагов состояния. Эти флаги могут изменяться после выполнения машинных команд;

- •1) Первой известной кодировкой символов была кодировка ascii, и она используется до сих пор. В ascii-кодировке каждый символ занимает 8 бит, или один байт.

- •2. Адресные операнды – задают физическое расположение операнда в памяти с помощью указания двух составляющих адреса: сегмента и смещения. К примеру:

- •5. Структурные операнды используются для доступа к конкретному элементу структуры.

- •6. Записи (аналогично структурному типу) используются для доступа к битовому полю некоторой записи.

- •Команды безусловной передачи управления:

- •Команды условной передачи управления:

- •Команды управления циклом:

- •От типа операнда в команде безусловного перехода (ближний или дальний);

- •Лабораторная работа №1. Тема: знакомство с системой программирования Турбо-ассемблер.

- •1) Пересылка данных

- •2) Xor логическое исключающее или

- •3) Команды передачи управления

- •Задание для самостоятельной работы

- •Лабораторная работа №1. Тема: знакомство с системой программирования Турбо-ассемблер.

- •1) Пересылка данных

- •2) Xor логическое исключающее или

- •3) Команды передачи управления

- •Команды вычитания.

- •Команды умножения.

- •Команда деления

- •Команды преобразования

- •Команды сдвига

- •Задание для самостоятельной работы.

- •Лабораторная работа №4. Тема: перевод чисел из шестнадцатиричной системы исчисления в десятичную и в двоичную.

- •Задание для самостоятельной работы.

- •Лекция №10. Сложные структуры данных. Массивы. Структуры.

- •4) Mov esi,6*2 ; 2 байта – размер элементов

- •Индексная адресация со смещением — режим адресации, при котором полный адрес формируется из двух компонентов:

- •Базовая индексная адресация со смещением — режим адресации, при котором полный адрес формируется максимум из трех компонентов:

- •Структуры

- •Организовать обращение к элементам структуры.

- •Цепочечные команды или команды обработки строк символов

- •Организация обращения к элементам записи.

- •Iotest record

- •Работа с записями

- •1) Для выделения элемента записи необходимо:

- •2) Чтобы поместить измененный элемент на его место в запись необходимо:

- •3. В конце работы файл следует закрыть.

- •4. Признаком ошибки при выполнении функции dos является взведенный флаг с (переноса).

- •2. Создание файла с усечением существующего до нулевой длины.

- •LpFileName — указатель на asciiz-строку с именем (путем) открываемого или создаваемого файла;

- •DwDesiredAccess — тип доступа к файлу:

- •Лекция №6. Работа с сопроцессором. Команды для работы с fpu. Работа с fpu.

- •Лекция №6. Работа с сопроцессором. Команды для работы с fpu. Работа с fpu.

- •Лекция №6. Работа с сопроцессором. Команды для работы с fpu. Работа с fpu.

- •Лабораторная работа №1. Тема: знакомство с системой программирования Турбо-ассемблер.

- •1) Пересылка данных

- •2) Xor логическое исключающее или

- •3) Команды передачи управления

- •Лабораторная работа №2. Тема: Работа с арифметическими командами.

- •Команды сложения

- •Команды вычитания.

- •Команды умножения.

- •Команда деления

- •Команды преобразования

- •Команды сдвига

- •Лабораторная работа №4. Тема: перевод чисел из шестнадцатиричной системы исчисления в десятичную и в двоичную.

- •Директива extrn Режимы Ideal, masm

- •Преимущества и недостатки ]Преимущества

- •Недостатки

- •Блок-схема вывода на экран вещественного числа, которое хранится в регистре st(0) сопроцессора.

- •Трансцендентные операции fpu

- •Функция MessageBox

- •1) Первой известной кодировкой символов была кодировка ascii, и она используется до сих пор. В ascii-кодировке каждый символ занимает 8 бит, или один байт.

- •2.Адресные операнды – задают физическое расположение операнда в памяти с помощью указания двух составляющих адреса: сегмента и смещения. К примеру:

- •5. Структурные операнды используются для доступа к конкретному элементу структуры.

- •6. Записи (аналогично структурному типу) используются для доступа к битовому полю некоторой записи.

- •4) Нельзя использовать сегментный регистр cs в качестве операнда назначения.

- •5) Оператор ptr можно применять и когда требуется принудительно поменять размерность операндов. К примеру, требуется переслать значение 0ffh во второй байт поля flp:

- •Xchg eax,ebx ; обменять содержимое регистров eax и ebx.

- •Xchg al,al ; а эта команда не делает ничего

- •Xchg ax, word ptr [si] ; обменять содержимое регистра ах и слова в памяти по адресу в [si].

4) Нельзя использовать сегментный регистр cs в качестве операнда назначения.

5) Оператор ptr можно применять и когда требуется принудительно поменять размерность операндов. К примеру, требуется переслать значение 0ffh во второй байт поля flp:

.data

flp dw ?

.code

start:

----

mov byte ptr (flp+1),0ffh

----

end start

Для двунаправленной пересылки данных применяют команду xchg. Эту же операцию можно выполнить применив последовательность из нескольких команд mov. Общий вид записи:

XCHG <операнд1>, <операнд2>

Содержимое операнда2 копируется в операнд1, а старое содержимое операнда1 — в операнд2. XCHG можно выполнять над двумя регистрами или над регистром и переменной.

Например:

Xchg eax,ebx ; обменять содержимое регистров eax и ebx.

То же, что три команды на языке С:

temp = eax;

eax = ebx;

ebx = temp;

Xchg al,al ; а эта команда не делает ничего

Xchg ax, word ptr [si] ; обменять содержимое регистра ах и слова в памяти по адресу в [si].

Для условной пересылки данных используется команда:

CMOVcc <приёмник><источник>

Набор команд, которые копируют содержимое источника в приемник, если удовлетворяется то или иное условие.

Можно использовать команды CMOVcc сразу после команды СМР (сравнение) с теми же операндами, например:

cmp ах,bх ; сравнить ах и bх

cmovl ax,bx ; если ах < bх, скопировать bх в ах

Слова «выше» и «ниже» в таблице 1 относятся к сравнению чисел без знака, слова «больше» и «меньше» учитывают знак.

Таблица 4.1. Разновидности команды CMOVcc

|

Код команды |

Реальное условие |

Условие для CMP |

|

CMOVA + CMOVNBE |

CF = 0 и ZF = 0 |

если выше; ax>bx если не ниже или равно; ax>bx or ax=bx |

|

CMOVAE + CMOVNB CMOVNC |

CF = 0 |

если выше или равно; ax>bx or ax=bx если не ниже; ax>bx если нет переноса |

|

CMOVB + CMOVNAE CMOVC |

CF = 1 |

если ниже; ax<bx если не выше или равно; ax<=bx если перенос; |

|

CMOVBE + CMOVNA |

CF = 1 и ZF = 1 |

если ниже или равно; ax<=bx если не выше ax<bx |

|

CMOVE + CMOVZ |

ZF = 1 |

если равно; ax=bx если ноль |

|

CMOVG + CMOVNLE |

ZF = 0 и SF = OF |

если больше; ax>bx если не меньше или равно; ax>bx or ax=bx |

|

CMOVGE + CMOVNL |

SF = OF |

если больше или равно; ax>bx or ax=bx если не меньше; ax>=bx |

|

CMOVL + CMOVNGE |

SF <> OF |

если меньше; ax<bx если не больше или равно |

|

CMOVLE + CMOVNG |

ZF = 1 и SF <> OF |

если меньше или равно; ax<bx or ax=bx если не больше |

|

CMOVNE + CMOVNZ |

ZF = 0 |

если не равно; ax!=bx если не ноль |

|

CMOVNO |

OF = 0 |

если нет переполнения |

|

CMOVO |

OF = 1 |

если есть переполнение |

|

CMOVNP CMOVPO |

PF = 0 |

если нет четности если нечетное |

|

CMOVP CMOVPE |

PF = 1 |

если есть четность если четное |

|

CMOVNS |

SF = 0 |

если нет знака |

|

CMOVS |

SF = 1 |

если есть знак |

Для обращения порядка байт в 32-битном регистре используется команда:

BSWAP <регистр 32>

Биты 0 – 15 меняются местами с битами 16–31. Например:

mov eax,12345678h

bswap eax ; теперь в еах находится 78563412h

Чтобы обратить порядок байт в 16-битном регистре, следует использовать команду XCHG:

xchg al,ah ; обратить порядок байт в АХ

Регистры архитектуры x86

Регистры архитектуры x86 (Intel 8086, 80186, 80286, 80386, 80486, Pentium'ы и аналоги этих процессоров от других фирм) представлены на рис. 3.1.

Регистры- указатели

Указатель команд

аккумулятор

база

счётчик

регистр данных

индекс источника

индекс приёмника

указатель базы

указатель стека

Рис. 3.1. Основные регистры процессоров.

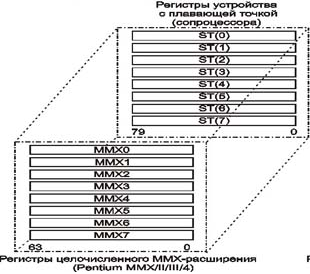

Регистры сопроцессора

Сопроцессор (FPU) предназначен для выполнения операций над вещественными числами.

Восемь регистров данных разрядностью 80 бит организованы в стек. Минимальный размер значения, загружаемого в сопр, - 2 байта/

Регистры данных FPU (Floating Point Unit - арифметический стек) могут быть представлены в следующем виде:

|

Физические номера |

80 бит |

Относительные номера |

|||

|

1 бит |

15 бит |

64 бит |

|||

|

Знак |

Порядок |

Мантисса |

|||

|

0 |

|

|

mm0 |

ST(0) |

|

|

1 |

|

|

mm1 |

ST(1) |

|

|

2 |

|

|

mm2 |

ST(2) |

|

|

3 |

|

|

mm3 |

ST(3) |

|

|

4 |

|

|

mm4 |

ST(4) |

|

|

5 |

|

|

mm5 |

ST(5) |

|

|

6 |

|

|

mm6 |

ST(6 |

|

|

7 |

|

|

mm7 |

ST(7) |

|

|

|

|

|

Регистры MMX/3DNow! |

|

|

Расширение MMX (MultiMedia eXtension - мультимединое расширение)

MMX было первым расширением, реализующим технологию SIMD (Single Instruction - Multiple Data).

Расширение MMX использует новые типы упакованных 64-битные целочисленных данных:

- 8 упакованных байт (Packed byte);

- 4 упакованных слова (Packed word);

- 2 упакованных двойных слова (Packed double word);

- 1 учетверенное слово (Quad word);

Каждая инструкция MMX выполняет действие сразу над всем комплектом операндов (8, 4, 2 или 1), размещенных в адресуемых регистрах. Совпадение регистров MMX и FPU накладывает ограничение на чередование кодов FPU и MMX.

Можно поместить в MMX-регистр одну 8-байтовую целую переменную и использовать её различными командами, можно поместить две 4-байтные переменные или четыре 2-байтных, или восемь переменных по одному байту и производить над ними операции одновременно.

MMX-регистры используются в программах обработки звука и видео, в математических программах, в играх.

Расширение 3DNow!

Технология 3DNow!, разработанная AMD, расширяет возможности MMX и разрабатывалась для трёхмерных приложений. Она позволяет оперировать с новым типом данных - парой упакованных вещественных чисел одинарной точности.

Технология использует те же регистры, что и MMX, но позволяет помещать в них два 32-битных числа с плавающей точкой.

Причём процессор выполнял 2 инструкции 3DNow! за такт, обрабатывая 4 числа с плавающей точкой одновременно