- •Раздел 1. Микропроцессорные системы управления.

- •Раздел 2. Микроконтроллерные системы управления.

- •Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

- •1. Микропроцессорные системы управления

- •1.1. Принципы построения и основы работы

- •Вопросы и задания

- •1.2. Элементная база мпсу

- •Вопросы и задания

- •1.3. Оперативные запоминающие устройства.

- •Вопросы и задания

- •1.4. Постоянные запоминающие устройства.

- •Вопросы и задания

- •1.5. Архитектура микропроцессора типа кр580вм80

- •Вопросы и задания

- •1.6. Типы машинных циклов и слово состояния

- •Вопросы и задания

- •1.7. Командные циклы чтения/записи

- •Вопросы и задания

- •1.8. Командный цикл подтверждения прерывания.

- •1.9. Принципиальные электрические схемы

- •Вопросы и задания

- •1.10. Интерфейс мпсу с изолированной системой шин

- •Вопросы и задания

- •1.11. Интерфейс мпсу с общей системой шин

- •1.12. Организация обслуживания запросов прерывания

- •Вопросы и задания

- •1.13. Программируемый контроллер

- •Вопросы и задания

- •1.14. Программируемый контроллер прерываний

- •Вопросы и задания

- •1.15. Программируемый интервальный таймер

- •Вопросы и задания

- •1.16. Мпсу с вводом-выводом аналоговой информации

- •Вопросы и задания

- •1.17. Выходные каскады мпсу

- •Вопросы и задания

- •2. Микроконтроллерные системы управления

- •2.1. Архитектура микроконтроллера к1816ве51

- •Вопросы и задания

- •2.2. Принципиальная электрическая схема порта

- •2.3. Схемы подключения внешней памяти к мк51

- •Вопросы и задания

- •2.4. Интерфейс мк51 с большим числом

- •Вопросы и задания

- •2.5. Таймер/счетчики мк51.

- •Вопросы и задания

- •2.6. Система прерываний мк51. Использование прерываний в программах

- •Вопросы и задания

- •2.7. Основы организации

- •Допустимые различия скорости приемо-передачи

- •2.8. Организация мультиконтроллерных систем

- •Программы инициализации станции и абонентов

- •Программы станции и абонента в сеансе "станция→абонент"

- •2.9. Микроконтроллерная система управления

- •3. Вопросы эксплуатации микропроцессорных устройств

- •3.1. Отладка аппаратных средств мпсу

- •Вопросы и задания

- •3.2. Отладка программного обеспечения мпсу

- •Вопросы и задания

- •3.3. Методы обеспечения помехоустойчивости мпсу

- •Вопросы и задания

- •1. Группа команд пересылок

- •2. Группа команд инкремента-декремента

- •3. Группа арифметических команд

- •4. Группа логических команд

- •5. Группа команд сдвига

- •6. Группа команд передачи управления

- •7. Группа команд работы со стеком

- •8. Группа команд ввода-вывода и управления микропроцессором

- •1. Группа команд пересылок

- •2. Группа команд арифметических операций

- •3. Группа команд логических операций

- •4. Группа команд операций с битами

- •5. Группа команд передачи управления

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

Вопросы и задания

1. Назовите форматы организации оперативной памяти и типы ПЗУ по способам их программирования.

2. Как определить емкость ПЗУ (в битах, байтах, словах) по обозначению его микросхемы?

3. Поясните диаграммы сигналов в цикле чтения ПЗУ с раздельными шинами адреса и данных.

4. Поясните диаграммы сигналов в цикле чтения ПЗУ с мультиплексируемыми (совмещенными) шинами адреса и данных.

1.5. Архитектура микропроцессора типа кр580вм80

В МПСУ используются различные типы микропроцессоров. Все они работают практически одинаково. Выбор МП типа КР580ВМ80 продиктован тем, что его архитектура стала базовой для всех последующих поколений МП, применяемых в МПСУ, а также вместе с ним впервые был разработан законченный набор интерфейсных схем: PPI, PIC, PIT и др. (рис.1.6). Освоив этот МП и комплект интерфейсных схем, можно самостоятельно освоить другие их типы.

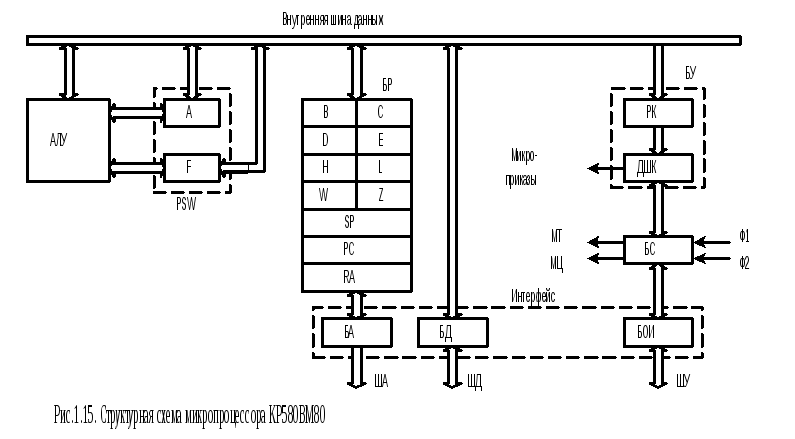

Структурная схема МП КР580ВМ80 приведена на рис.1.15.

Б локи

МП имеют следующее функциональное

назначение:

локи

МП имеют следующее функциональное

назначение:

АЛУ (арифметико-логическое устройство) обеспечивает выполнение логических (сложение, умножение, инверсия и сдвиги) и арифметических (сложение и вычитание) операций над 8-разрядными данными. АЛУ программно недоступно.

А (аккумулятор) является программно доступным 8-разрядным регистром универсального назначения, который используется АЛУ при выполнении им логических и арифметических операций и в А сохраняется итоговый результат. Через А осуществляется обмен информацией с памятью и внешними устройствами.

F (регистр флагов) является 8-разрядным регистром, в котором хранятся признаки (флаги) результатов исполнения команд (рис.1.16).

|

Биты регистра F |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

Флаги регистра F |

S |

Z |

- |

AC |

- |

P |

- |

C |

|

Рис.1.16. Структура регистра флагов |

||||||||

Назначение флагов:

S (Sign) – флаг знака, зависящий от значения 7-го бита результата текущей операции в АЛУ: если этот бит равен 0, то результат считается положительным (число в АЛУ находится в интервале от 0 до 127), если равен 1, то результат считается отрицательным (число в АЛУ находится в интервале от -1 до -128). Соответственно S=0/1 для положительного/отрицательного знака результата в АЛУ.

Z (Zero) – флаг нуля. Z=1, если результат текущей операции равен нулю.

C (Carry) – флаг переноса. Устанавливается в 1 при возникновении переноса из старшего разряда в арифметических операциях, операциях сравнения двух чисел, десятичной коррекции.

AC (Auxiliary carry) – флаг вспомогательного переноса. Устанавливается в 1 при возникновении переноса из третьего разряда в арифметических операциях над однобайтными данными, операциях сравнения двух чисел, десятичной коррекции.

P (Parity) – флаг четности. Устанавливается в 1, если код результата текущей операции содержит четное число единиц.

Из всех флагов регистра F программно доступен только флаг переноса С.

БР – блок регистров. Блоки регистров классифицируются по разрядности и программной доступности.

B, C, D, Е, H, L – блок программно доступных 8-разрядных регистров общего назначения (РОН). Эти регистры могут быть объединены в пары BC, DE и HL, которые являются 16-разрядными и также программно доступными. Регистр HL используется в ряде команд как указатель М адреса памяти.

PSW – 16-разрядный регистр слова состояния программы, являющийся объединением аккумулятора А и регистра флагов F (PSW=A+F).

W, Z – программно недоступные 8-разрядные регистры. Эти регистры используются для приема и временного хранения в них 2-го и 3-го байтов операнда.

SP (Stack Pointer) – указатель стека. В этом регистре хранится адрес ячейки ОЗУ, называемой вершиной стека. Регистр SP программно доступен.

PC (Program Counter) – счетчик команд. В этом регистре устанавливается адрес ячейки ПЗУ, из которой производится в текущем машинном цикле чтение одного из байтов кода команды (см. рис.1.3). РС программно доступен. При включении питания или сбросе в РС записывается адрес 0000Н=0000.0000.0000.0000В.

RA (Register Address) – регистр исполняемого адреса, который выставляется на ножки ША. В фазе чтения команды в RA пересылается содержимое счетчика команд РС. В фазе выполнения команды в зависимости от ее типа содержимое регистра RA формируется из содержимого одного из вышеописанных регистров (A, B, D, E, H, L, W, Z, SP, PC). Регистр RA программно недоступен.

БУ – блок управления микропроцессором.

РК – регистр команд. На фазе чтения команды в него загружается КОП.

ДШК – дешифратор команд, в котором расшифровывается КОП. В результате этой расшифровки:

- определяется количество байт операнда команды;

- определяется количество и тип машинных циклов (МЦ) команды, количество машинных тактов (МТ) внутри каждого МЦ;

- определяется содержание каждого МТ.

Во исполнение МТ и МЦ из ДШК выходят тактируемые сигналы микроприказов на все блоки МП. ДШК является тактируемым комбинационным устройством. В ДШК зашиты все команды микропроцессора.

Б С

– блок синхронизации. Является тактируемым

внешними импульсами Ф1 и Ф2 устройством,

которое формирует сигналы МТ и МЦ в

соответствии с программой, полученной

от ДШК, и одновременно тактирует работу

ДШК.

С

– блок синхронизации. Является тактируемым

внешними импульсами Ф1 и Ф2 устройством,

которое формирует сигналы МТ и МЦ в

соответствии с программой, полученной

от ДШК, и одновременно тактирует работу

ДШК.

Ф1 и Ф2 – синхроимпульсы, вырабатываемые внешним генератором импульсов. Частота генератора в 9 раз выше частоты синхроимпульсов. Пять возможных вариантов параметров синхроимпульсов Ф1 и Ф2 приведены на рис.1.17. Амплитуда импульсов Ф1 и Ф2 составляет +12 В. Частота следования импульсов Ф1 и Ф2 равна 2,5 МГц, а период - 0,4 мкс=400 нс.

МТ – машинный такт является минимальным интервалом машинного времени, в течение которого происходит изменение состояния хотя бы в одном блоке микропроцессора. Длительность МТ равна периоду следования импульсов Ф1 и Ф2.

МЦ – машинный цикл представляет собой совокупность из МТ. В каждом МЦ микропроцессор обращается для чтения или записи либо к памяти, либо к внешнему устройству.

В командах содержится от 1 до 5 МЦ, каждый из которых состоит из 3…5 МТ. Содержимое МЦ и МТ исполняемых команд определяется в ДШК.

Интерфейсный блок обеспечивает связь МП с памятью и внешними устройствами. В него входят буфер адреса (БА), буфер данных (БД) и блок обмена информацией (БОИ). Буферные блоки в режиме вывода информации из МП обеспечивают усиление по току сигналов соответствующих шин. Функции БОИ:

- воспринимает сигнал сброса RES, активный 1;

-

формирует для внешних устройств и памяти

синхросигнал SYNC (активный 1), сигналы

DBIN (РАЗРЕШЕНИЕ ПРИЕМА, подтверждающий

то, что МП принимает информацию с ШД;

активный 1),

![]() (РАЗРЕШЕНИЕ ЗАПИСИ, подтверждающий то,

что МП выводит информацию на ШД; активный

0);

(РАЗРЕШЕНИЕ ЗАПИСИ, подтверждающий то,

что МП выводит информацию на ШД; активный

0);

- обслуживает прерывания, захват шин и режим ожидания МП.

На прерывания задействовано два вывода МП – INT (ЗАПРОС ПРЕРЫВАНИЯ, активный 1) и INTE (РАЗРЕШЕНИЕ ПРЕРЫВАНИЙ, активный 1). INT является входным сигналом, который поступает с внешнего устройства с требованием срочного (внеочередного) его обслуживания. МП может обслужить этот запрос при условии, что в программе выполнена команда EI разрешения обслуживания запроса прерывания. С началом обслуживания прерывания МП сообщает сигналом INTE=0 всем ВУ то, что далее сигналы запросов прерываний по входу INT игнорируются. Режим прерываний широко используется в МПСУ.

На захват шин задействовано два вывода МП – HOLD (ЗАПРОС ЗАХВАТА, активный 1) и HLDA (ПОДТВЕРЖДЕНИЕ ЗАХВАТА, активный 1). HOLD является входным сигналом, который поступает с внешнего устройства с требованием предоставить ему право управлять всеми шинами МЭВМ – ША, ШД и ШУ. Такой режим на практике возникает в случае, когда внешнее устройство должно передать очень большой объем информации в ОЗУ, например с компакт-диска, винчестера. Чтобы ускорить этот процесс, информация передается из источника в ОЗУ не через МП, а напрямую с использованием для этого простых и быстро выполняемых команд. Режим захвата шин называют также режимом прямого доступа к памяти (ПДП). Устройство, выполняющее такую передачу информации, называется контроллером ПДП. В случае предоставления ПДП МП переводит свои шины в 3-е состояние и выставляет сигнал HLDA, после которого активизируется контроллер ПДП. Этот режим в МПСУ не используется, так как объемы оперативной информации в МПСУ всегда очень малы и не превышают нескольких сотен байт.

На режим ожидания МП задействовано два вывода МП – RDY (ГОТОВ, активный 1) и WAIT (ОЖИДАНИЕ, активный 1). Сигнал RDY является входным, а WAIT – выходным. Если режим ожидания не используется, то на вход RDY подается постоянный сигнал 1, иначе к входу RDY подключается ВУ. Режим ожидания вводится в случае выполнения программы обмена информацией между МП и ВУ низкого быстродействия, например с клавиатурой, принтером и т.п. Работа с такими устройствами имеет ту особенность, что ВУ отвечает на сигналы от МП с запаздыванием. Поэтому нужно прервать выполнение программы обмена с "медленным" ВУ до тех пор, пока не будет получен от него ответ. ВУ, установив RDY=0, останавливает выполнение текущей команды, а МП выдает сигнал WAIT=1, который воспринимается ВУ как подтверждение останова выполнения программы и ожидания ответа ВУ. Как только ВУ будет готово к передаче порции информации, оно выставит RDY=1, и возобновит работу прерванная команда (операция) обмена информации. В МПСУ режим ожидания применяется в отладочных операциях и позволяет организовать работу МП с остановками после выполнения очередной команды или очередного цикла.